Field Effect Transistor

-

Upload

srinivas-rao -

Category

Engineering

-

view

1.166 -

download

2

Transcript of Field Effect Transistor

1

1

Field Effect Transistor

AEI302.31 TO 33

Field effect Transistor is a semiconductor device

which depends for its operation on the control of

current by an electric Field

2

2

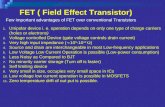

Field Effect TransistorFET has several advantages over BJT

1. Current flow is due to majority carriers only2. Immune to radiation3. High input resistance4. Less noisy than BJT5. No offset voltages at zero drain current 6. High thermal stability

AEI302.31 TO 33

3

JFET Symbol

EC-302.31 t0 32

N Channel FET P Channel FET

Fig 4 . JFET symbols

AEI302.31 TO 33

FET

JFET MOSFET

N-channel p-channel Depletion type Enhancement type

p-channelN-channelp-channel

N-channel

Classification of Field Effect Transistors

AEI302.31 TO 33

5

JFET

Based on the construction JFETS are of Two types

1.N Channel FET

2.P Channel FET

AEI302.31 TO 33

6

6

Construction

Drain

Source

GATE

For a N Channel FET an N type silicon Bar is

used

Heavily doped P type material is

deposited on either side of the bar to

form GATE

The two ends of the bar are known

as Source and Drain

Fig 3. Construction of N Channel FET EC-302.31 t0 32

AEI302.31 TO 33

7

7

Construction of FET Source : The source is the terminal through

which majority carriers enter the Silicon Bar

Drain : Terminal through which Majoroty carriers leave the bar

Gate: controls Drain current and is always reverse biased

EC-302.31 t0 32

AEI302.31 TO 33

8

8

Construction of FET Analogy : The operation of FET can be compared to the

water flow through a flexible pipe When One end is pressed the cross sectional area

decreases hence water flow decreases In a FET drain is similar to outlet Gate is similar to control in the figure 2

AEI302.31 TO 33

9

9

Principle

9 when the pipe is pressed at one end

water flow decreases

Fig2. water Pipe analogy

Inlet ( Source)

Outlet (Drain)

Control (Gate)

AEI302.31 TO 33

10

10

Operation Principle : To control the drain current FET

makes use of channel formed in by Space charge region between Gate and the bar

By increasing the reverse bias the width of space charge region decreases

As a result the channel Resistance increases The Drain current decreases

AEI302.31 TO 33

+

11

11

Working

+Drain

Source

GATE

Source is connected to

-ve Of the battery 1

Drain is connected to

+ve of the battery

Gate is reverse Biased

by battery 2

A channel is established

along the length of the

bar because of Space

charge Region

As we increase the

Reverse bias on Gate

(VGS)The channel width

decreases

Space charge Region

Channel

AEI302.31 TO 33

+

12

12

Working

+Drain

Source

GATE

As we increase the

Reverse bias on Gate

(VGS)The channel width

decreases

It is Possible to adjust the

bias such that Drain

current becomes zero

The Bias voltage at which

Drain current becomes

Zero is Known as pinch

off voltage

AEI302.31 TO 33

13

Working

N Channel FET P Channel FET

Source connected to -VE

Drain Connected to +ve

Gate connected to –ve (Reverse Biased)

Source connected to +VE

Drain Connected to -ve

Gate connected to +ve (Reverse Biased)

AEI302.31 TO 33

14

14

Working

1. when Voltage is applied between source and Drain majority

carriers move through the channel between depletion region

2. The value of Drain current is maximum when no external

voltage is applied between gate and source

3. When gate to source reverse bias increases the depletion

region widens and channel width decreases hence Drain

current decreases

14

AEI302.31 TO 33

15

15

Working

1. Hence Drain current decreases

2. When gate to source voltage is increased further The channel

completely closes

3. This is called pinch off region

4. This reduces Drain current to Zero

5. The Gate to source voltage at which the Drain current is zero

is called “ Pinch off Voltage”

15

AEI302.31 TO 33

16

16

P Type and N type FETs 16

P Channel FET

1.Current carriers are holes

2.Mobility of holes is poor

3.More noise

4.Low Transconductance

N Channel FET

1. Current carriers are Electrons

2. Mobility of electrons is almost twice that of Holes in P channel FET

3. Low input Noise4. Large Transconductance

AEI302.31 TO 33

17

17

JFET Parameters 17

Electrical behavior is described in terms of the

parameters of the Device. They are obtained from the

characteristics. Important Parameters for FET are

1.DC Drain resistance

2.AC drain Resistance

3.Transconductance

AEI302.31 TO 33

18

18

JFET Parameters 18

1. DC Drain resistance : Defined as Ratio of Drain

to source Voltage VDS to Drain current ID. Also

called static or Ohmic Resistance

2. Mathematically

RDS= VDS/ID

AEI302.31 TO 33

19

19

JFET Parameters 19

1. AC Drain resistance : Defined as the resistance

between Drain to source when JFET is operating

in Pinch off Region or saturation Region

2. Mathematically

D

DSD I

Vr

When VGS is constant

AEI302.31 TO 33

20

20

JFET Parameters 20

1. Transconductance (gm): It is given by the ratio

of small change in drain current to the

corresponding change in the Gate to source

Voltage VGS. Also known as Forward

Transmittance

2. Mathematically

DS

Dm V

Ig

AEI302.31 TO 33

21

21

FET and BJT 21

BJT 1. Bipolar device

2.Current controlled device

3.Low input impedance

4.Low thermal stabilty

5.Lower switching speeds

6.More noisy

7.Diffuicult to fabricate on IC

FET1. Uni polar device 2. Voltage controlled Device3. High input impedance (in

Mega ohms)4. Better thermal stability5. High switching speeds6. Less Noisy7. Easy to fabricate

AEI302.31 TO 33

22

22

Drain Characteristics 22 Drain characteristics show the relation between the

drain to source voltage and VDS and drain current ID

AB

Avalanche BreakdownID

VDS

- VGS

OHMIC Region Pinch Off

Region Breakdown Region

VGS= 0

AEI302.31 TO 33

23

23

Drain Characteristics 23 Drain characteristics show the relation between the

drain to source voltage and VDS and drain current ID

AB

Avalanche BreakdownID

VDS

- VGS

OHMIC Region Pinch Off

Region Breakdown Region

VGS= 0 When VDS=0 , ID=0 as VDS increases ID also

increases up to Knee Point AThis region is Known as

OHMIC region

In the region AB Drain current increases as

inverse square law rate with Drain to source

Voltage

At the Drain to source Voltage corresponding

to point B Channel width reduces to a

minimum value and is known as pinch off

AEI302.31 TO 33

24

24

Drain Characteristics 24 Drain characteristics show the relation between the

drain to source voltage and VDS and drain current ID

AB

Avalanche BreakdownID

VDS

- VGS

OHMIC Region Pinch Off

Region Breakdown Region

VGS= 0Pinch Off Region

This region is Shown by BC known as saturation or

constant current region

Drain current remains at its maximum value IDSS

Drain current ID is given by

C

2

1

P

GSDSSD V

VII

AEI302.31 TO 33

25

25

Drain Characteristics 25 Drain characteristics show the relation between the

drain to source voltage and VDS and drain current ID

AB

Avalanche BreakdownID

VDS

- VGS

OHMIC Region Pinch Off

Region Breakdown Region

VGS= 0Breakdown Region

This region is Shown by CD Drain current increases

Rapidly with VDS

The device gets damaged due to

avalanche Breakdown mechanism

C

D

EC-302.31 t0 32

AEI302.31 TO 33

DISADVANTAGES OF FET OVER BJT

FETs have a drawback of smaller gain bandwidth product compared to BJT.

AEI302.31 TO 33

The high input impedance, low output impedance and low noise level make FET for superior of the bipolar transistor.

ApplicationsAs a buffer amplifier which isolates the preceding stage

from the following stage.

Features

AEI302.31 TO 33

Phase shift oscillators: The high input impedance of FET is especially valuable in phase shift oscillator to minimize the loading effect.

In voltmeters: The high input impedance of FET is useful in voltmeters to act as an input stage.

FET APPLICATIONS

AEI302.31 TO 33

AEI302.34 29

JFET N CHANNEL JFET

P CHANNEL JFET

AEI302.34 30

Classification of MOSFETs

MOSFET

Depletion type Enhancement type

p-channelN-channelp-channel

N-channel

AEI302.34

31

Metal oxide semiconductor field effect transistor (MOSFET)

MOSFET is an important semiconductor device and is widely used in many circuit application.

The input impedance of a MOSFET is much more than that if a FET because of very small leakage current.

• MOSFETs has much greater commercial Importance than JFET

N Channel

Drain

Substrate

Gate

Source

Oxide layer

p

AEI302.34 32

•The MOSFET can be used in any of the circuits covered for the FET.

•Therefore all the equations apply equally well to the MOSFET and FET in amplifier connections.

N Channel

Drain

Substrate

Gate

Source

Oxide layer

p

MOSFET (contd)

AEI302.34 33

•MOSFETs uses a metal gate electrode (instead of p-n junction in JFET), separated from the semi conductor by an Insulating thin layer sio2 to modulate the resistance of the conduction channel.

MOSFET (contd)

N Channel

Drain

Substrate

Gate

Source

Oxide layer

p

AEI302.34 34

• It is also called as insulated gate FET (IGFET)

•MOSFETs operates both in the depletion mode as well as an the enhancement mode

N Channel

Drain

Substrate

Gate

Source

Oxide layer

p

MOSFET (contd)

AEI302.34 35

N channel P channel

D

S

G

CIRCUIT SYMBOLS OF MOSFET

D

G

S

AEI302.34

36

There is only a single p-region. This is called substrate.

A thin layer of metal oxide is deposited over the left side of the channel. A metallic gate is deposited over the oxide layer. As silicon dioxide is an insulator, therefore a gate is insulated from the channel. For this reason MOSFET is some times called insulated gate FET.

Differences between MOSFET and FET

AEI302.35 to 36

37ENHANCEMENT MOSFET

A p-channel MOSFET consists of lightly doped n-substrate into which two heavily doped p+ regions act as the source and the drain.

A thin layer of SiO2 is grown over the surface of the entire assembly..

P channel Enhancement MOSFET

source Gate DrainSi o2 layer

Al layer

-------P+ P+

N-type substrate

InducedP channel

+++

AEI302.35 to 36 38

P channel Enhancement MOSFET

• Holes are cut into this SiO2 layer for making contact with p+ source and drain regions.

• On the SiO2 layer, a metal (alluminium) layer is overlaid covering the entire channel region from source to drain.

• This aluminum layer constitutes the gate.

Construction

source Gate DrainSi o2 layer

Al layer

-------P+ P+

N-type substrate

InducedP channel

+++

AEI302.35 to 36

39

The area of MOSFET is typically 5 square mills or less.

This area is extremely small being only about 5% of the area required for a bipolar junction transistor.

A parallel plate capacitor is formed with the metal areas of the gate and the semiconductor channel acting as the electrodes of the capacitor.

The oxide layer acts as the dielectric between the electrodes.

P channel Enhancement MOSFET

Construction

source Gate DrainSi o2 layer

Al layer

-------P+ P+

N-type substrate

InducedP channel

+++

AEI302.35 to 36 40

p channel

S

G

D

p channel enhancement MOSFET

G

D

S

substrate

symbols

AEI302.35 to 36

41WORKING The substrate will be

connected to the common terminal i.e., to the ground terminal.

A negative potential will be applied to the gate.

This results in the formation of an electric field normal the SiO2 layer.P channel Enhancement MOSFET

source Gate DrainSi o2 layer

Al layer

-------P+ P+

N-type substrate

InducedP channel

+++

AEI302.35 to 36 42

• This electric field originates from the induced positive charges on the semiconductor side on the lower surface of the SiO2 layer.

• The induced positive charge become minority carriers in the n-type of substrate.

P channel Enhancement MOSFET

WORKING

source Gate DrainSi o2 layer

Al layer

-------P+ P+

N-type substrate

InducedP channel

+++

AEI302.35 to 36 43

D

S

G

Enhancement MOSFET symbols

N channel N channel

substrate

G

S

D

AEI302.35 to 36 44

+ + + +N+ N+

P-type substrate

InducedN channel

------

sourceGate Drain

Si o2 layer

N channel Enhancement MOSFET

Al layer• It consists of a lightly doped p type substrate in to which two heavily Doped n type material are diffused.

• The surface is coated with a layer of silicon dioxide(Sio2).

• Holes are cut through the Sio2 to make contact with n-type blocks.

WORKING

AEI302.35 to 36 45

+ + + +N+ N+

P-type substrate

InducedN channel

------

source Gate Drain

Si o2 layer

N channel Enhancement MOSFET

Al layer

• The surface area between drain and source a metal plate is deposited from which gate terminal is taken out.

• Metal (Al) is deposited through the Holes to form drain andsource terminals

WORKING

AEI302.35 to 36 46

+ + + +N+ N+

P-type substrate

InducedN channel

------

source

Gate Drain

Si o2 layer

N channel Enhancement MOSFET

Al layer

•Gate is insulated from the body of FET so it is called insulated gate FET(IGFET).

•Structurally there exits no channel between sourceand drain so MOSFET some times called as N-channel enhancement type

•Because a thin layer of P-type substrate touching the metal oxide film provides channel for electrons and hence acts like N-type material.

AEI302.35 to 36 47

+ + +n+ n+

p-type substrate

Inducedn channel

-----

DrainSi o2 layer

Al layer

n channel Enhancement MOSFET

• Drain is made positive with respect to the source and no potential is applied to the gate as shown in figure.

• The two n-blocks and p-type substrate form back to back pn junctions connected by the Resistance of the p-type material.

• Both the junctions cannot be forwarded at the Same time so small drain current order of few nano amperes flows.

WORKING OF THE ENHANCEMENT MOSFET

SOURCE

AEI302.35 to 36 48

• So MOSFET is cut off when gate source voltage Is zero.

• That is why it is called normally-OFF MOSFET.

• The gate is made positive with respect to source substrate as shown in figure.

• A channel of electrons (n- channel) is formed in between the source and drain regions.

+ + +n+ n+

p-type substrate

Inducedn channel

- - -

Gate DrainSi o2 layer

Al layer

WORKING OF THE ENHANCEMENT MOSFET

SOURCE

AEI302.35 to 36 49

+ + +n+ n+

p-type substrate

Inducedn channel

- - -

Gate DrainSi o2 layer

Al layer

N channel Enhancement MOSFET

•When positive voltage is applied to gate the capacitor begin to charge.

•Behaves as a capacitor with gate metal acting as one electrode, upper surface of the substrate as other electrode and sio2 layer as dielectric medium.

SOURCE

AEI302.35 to 36 50

•Consequently positive charges appears on the gate and negative charges appears in the substrate between the drain and source.

•The n-channel thus formed is called induced n-channel or n-type inversion layer.

+ + +n+ n+

p-type substrate

Inducedn channel

- - -

Gate Drain

Al layer

N channel Enhancement MOSFET

SOURCE

•As VGS ,no.electrons in the channel , ID .

AEI302.35 to 36 51

The minimum gate source voltage which produces the induced n-channel is called threshold voltage VGS(th) when VGS < VGS (th), ID=0.

Drain current starts only VGS >VGS (th).

For a given value of VDS as VGS is increased , more and more electrons accumulate under the gate and ID increases.

AEI302.35 to 36 52

• So the conductivity of the channel is enhanced

by the positive bias on the gate, the device is

known as enhancement mode MOSFET.

• The n-channel MOSFET can never operate with a negative gate voltage.

AEI302.35 to 36 53

•It is observed that the drain current has been enhanced on application of negative gate voltage.

•This is the reason for calling it as enhancement MOSFET.

•By increasing the gate potential, pinch off voltage and drain currents are increased.

•The curves are similar to drain characteristics of JFET.

-10

-8

-6

-4

-2

Id(Ma)

Vds (v)

V gs=-20

-16

-12

0 -5 -10 -15 -20

• Drain characteristics

AEI302.37 TO 38 54

S

D

G

ENHANCEMENT MOSFET

N channelN channel

substrate

G

S

D

AEI302.37 TO 38 55

CIRCUIT SYMBOLS OF DEPLETION TYPE MOSFET

DEPLETION MOSFET

N channel

D

G

S

substrate

N channel

D

S

G

AEI302.37 TO 38

56CONSTRUCTIONDepletion MOSFET may be

fabricated from the basic MOSFET structure.

An n-type channel is obtained by diffusion between N+ type source and drain in an n-channel MOSFET.

N channel Depletion MOSFET

Drain

n+ n+

p-type substrate

Diffusedn channel

source GateSi o2 layer

Al layer

AEI302.37 TO 38 57

CONSTRUCTION

•In depletion MOSFET a lightly doped n-type channel has been introducedbetween to heavily doped source& drain blocks,.

N channel Depletion MOSFET

Drain

n+ n+

p-type substrate

Diffusedn channel

source GateSi o2 layer

Al layer

AEI302.37 TO 38

58

P channel Depletion MOSFET

•Depletion MOSFET may be fabricated from the basic MOSFET structure.

•An p-type channel is obtained by diffusion between p+ type source and drain in an p-channel MOSFET.

CONSTRUCTION OF P CHANNEL DEPLETION MOSFET

Drain

n+ n+

p-type substrate

Diffusedn channel

source GateSi o2 layer

Al layer

AEI302.37 TO 38 59

P channel Depletion MOSFET

•In p-channel depletion MOSFETs are made by using n-type substrate and diffusing a lightly doped p-type channel between two heavily dopedP-type source & drain blocks

Drain

n+ n+

p-type substrate

Diffusedn channel

source GateSi o2 layer

Al layer

AEI302.37 TO 38 60

D

S

G

S

D

Gsubstrate

P channel P channel

Symbols of p channel depletion MOSFET

AEI302.37 TO 38 61

• Negative gate operation of a depletion MOSFET is called Its depletion mode Operation

• When Vgs =0 electrons can flow freely from source to drain through the conducting channel. since a channel exists between drain & source, Id flows even when Vgs =0.

• It is also known as normally –ON MOSFET

p-type substrate

Si o2 layer

n+

sourceGate Drain

Al layerV GS

+++++++++

N channel Depletion MOSFET

Working

AEI302.37 TO 38 62

p-type substrate

When negative voltage is applied to the gate as shown in Fig positive charges are induced in the channel by capacitor action

The induced positive charges make the channel less conductive and drain current decreases as V GS is made more negative.

Si o2 layer

n+

sourceGate Drain

Al layerV GS

+++++++++

Working

N channel Depletion MOSFET

AEI302.37 TO 38 63

With negative voltage a depletion MOSFET behave like JFET.

Si o2 layer

n+

sourceGate Drain

Al layerV GS

+++++++++

Working

N channel Depletion MOSFET

AEI302.37 TO 38

64

When positive voltage is applied to the gate free

electrons are Induced channel .

• This enhances the conductivity of the channel so increasing amount of current between terminals

• Since the action of negative voltage on gate is to

deplete the channel of free n-type charge carriers so named as depletion MOSFET.

AEI302.37 TO 38

65

Drain Characteristics of depletion MOSFET

When the gate source voltage is zero

considerable drain current flows.

When the gate is applied with negative voltage, positive charge are induced in the n-channel through the SiO2 layer of the gate capacitor.

}

Enhancement Mode

Depletion Mode

8

6

4

2

0 5 10 15 20

Id(ma)

V ds

Fig.38.3

}VGS= -3V

VGS= -1V

VGS= 0V

VGS= +1V

VGS= +2V

AEI302.37 TO 38 66

• The conduction in n-channel FET is due to electrons i.e., the majority carriers.

•Therefore the induced positive charges make the n-channel less conductive.

•The drain current therefore gets reduced with increase in the gate bias voltage.

}}

Enhancement Mode

Depletion Mode

8

6

4

2

0 5 10 15 20

Id(ma)

V ds

Fig. 38.3

Drain Characteristics of depletion MOSFET

AEI302.37 TO 38 67

The distribution of charges in the channel results in depletion of majority carriers.

That is why this type of FET is called depletion MOSFET.

The voltage drop due to the drain current causes the channel region nearer to the drain to be more depleted than the region due to the source.

}}Depletion

Mode

8

6

4

2

0 5 10 15 20

Id (ma)

V ds

Enhancement Mode

Fig. 38.3

Drain Characteristics of depletion MOSFET

AEI302.37 TO 38 68

}}Depletion

Mode

8

6

4

2

0 5 10 15 20

Id(ma)

V ds

• This is similar to the pinch off in JFET.

Enhancement Mode

Fig. 38. 3

Drain Characteristics of depletion MOSFET

AEI302.37 TO 38

69

Application of positive gate voltage results in induced negative channel in the n-type channel

• The depletion MOSFET can also be operated in enhancement mode simply by applying a positive voltage to the gate

Drain Characteristics of depletion MOSFET

AEI302.37 TO 38

70Thus the conductivity of the channel gets increased the n-channel depletion MOSFET can be used as in enhancement mode by changing the gate voltage polarity.

• When a MOSFET is operated this way, we can it as dual mode MOSFET.

Drain Characteristics of depletion MOSFET

AEI302.39 71

Sno JFET MOSFET

1. JFET Gate is not insulated from the channel

MOSFET or IGFET is insulated from the channel

2. Channel and gate forms two pn junctions

Channel and gate forms parrallel plate capacitor.

3. There are only 3 leads There are 4 leads

4. Can be operated in depletion mode only

Can be operated inboth depletion and enhancement mode

5. Input impedance is high Input impedance is very high

6. Signal handling capacity is less

Signal handling capacity is more

7. Gate current is more Gate current is very less

8. Fabrication is complex and costly

Easy to fabricate,cheap. Most

Comparison of MOSFET and JFET

AEI302.39 72

Advantages of MOSFET Over JFET

• The insulated gate in MOSFET s result in much greater input impedance than that of JFET

• Inter electrode capacitance are independent of bia voltage and these capacitances are smaller incase of MOSFETs than JEFT.

• It is easier to fabricate MOSFET than JFET.

• MOSFET has no gate diode. This makes it possible to operate with +ve or –ve gate voltages

AEI302.39 73

Application of MOSFETs

• Because of higher input resistance ,the enhancement type MOS devices have been used as micro-resistor in integrated micro-circuits .

• For electrometer circuits where exceptionally low currents are to be measured MOSFETs are most nearly ideal.

• MOSFET s are very small in size .which make them suitable for highly complex digital arrays

AEI302.40

74

CONSTUCTION OF COMPLEMENTARY MOSFET(CMOS)

In this device two MOSFETs that are complementary to each other are used.

N+ P+N+ P+

P- WellN-substrate

Q2

Q1

G

S2 S1

D

AEI302.40 75

N+ P+N+ P+

P- WellN-substrate

•The drains of both the MOSFETs are combined and single terminal is taken.

Q2

Q1

G

S2 S1

D

CONSTRUCTION OF CMOSFET(contd..)

AEI302.40 76

N+ P+N+ P+

P- WellN-substrate

Q2

Q1

G

S2 S1

D

•Similarly the gates of both the transistors are combined and a single gate terminal is taken out.

•Here the input is appllied at the input

terminal vi.

CONSTRUCTION OF CMOSFET(contd..)

AEI302.40

77

When vi is high i.e., equal to -VDD then Q1 is turned ON and Q2 is turned OFF.

The output VO is zero.

Similarly when the input voltage Vi is low i.e., equal to 0v, the Q2 turned ON and Q1 turned OFF.

V1

-VDD

Q1

Q2

V0

WORKING PRINCIPLE OF CMOSFET

AEI302.40 78

•So the output voltage Vo lies at –V dd level i.e., high.

•Thus the CMOSFET in this configuration works as an inverter.V1

-VDD

Q1

Q2

V0

WORKING PRINCIPLE OF CMOSFET(contd..)

AEI302.40 79

V1

VDD

Q1

Q2

V0

•The key advantage of using CMOS design is this extremely low power consumption usually of the order of 50mv

AEI302.41 80

1

CONSTRUCTION OF UJT

80

P

N

B1

B2

E

PN Junction

N type Silicon bar

UJT consists of lightly doped

n-type silicon bar with an electrical

connection on each end

These connections are called

base1 (B1)and base2(B2 )

Along the bar between two bases,

nearer to base2 a P-N junction

is formed by doping P-type

material

AEI302.41 81

1 The lead connected to the P-type material is called emitter

UJT is a three terminal device.

since the device has one p-n junction and three leads, it is called as unijunction transistor

81

P

N

B1

B2

E

PN Junction

N type Silicon bar

CONSTRUCTION OF UJT(contd.)

AEI302.41 82

1

82

P

N

B1

B2

E

PN Junction

N type Silicon bar

With only one p-n junction, the device is really a form of diode because two base terminal are taken from one section of the diode this device is also called double-based diode

The emitter is heavily doped the n-region, is lightly doped for this reason the resistance between the base terminals is very high (5to10 kohms) when emitter lead is open

CONSTRUCTION OF UJT (contd.)

AEI302.41 83

UNI JUNCTION TRANSISTOR

DEVICE CIRCUIT SYMBOL

83

AEI302.41 84

Equivalent circuit of UJT

0 The PN junction behaves like a diode

The lightly doped silicon bar has high resistance can be represented by two resistors connected in series RB1 and RB2.

0

84

AEI302.41 85

0

The Resistance offered by N-type bar between Base-1 and Emitter is referred as RB1.

The Resistance offered by N-type bar between Base-2 and Emitter is referred as RB2.

0

85

Equivalent circuit of UJT(contd.)

AEI302.41 86

0

The Resistance of N-type bar is known as Base spreading resistance RBB.

RBB = RB1 + RB2

Equivalent circuit of UJT(contd.)

AEI302.41 87

Intrinsic stand of ratio

0

The intrinsic stand-off ratio is denoted by η.

η = RB1/(RB1+RB2)

87

AEI302.41 88

0

The intrinsic stand-off ratio is the property of a UJT is always less than unity

Typical range of η is lies between 0.5 to 0.8

8888

Intrinsic stand of ratio

AEI302.42 89

UNI JUNCTION TRANSISTOR

DEVICE CIRCUIT SYMBOL

89

AEI302.42 90

WORKING OF UJT

1

With emitter open the voltage VBB is applied between two bases with Base2 positive with respect to Base1.A voltage gradient will established along the N-type Bar.

The voltage drop across RB1 is V1.

1

90

AEI302.42 91

1

V1= η VBB where η =RB1/(RB1+RB2)

VD is the barrier voltage of the emitter diode. Then the Total reverse bias voltage is V1+VD= η VBB+VD.

For Silicon VD=0.7V.

1

91

WORKING OF UJT(contd.)

AEI302.42 92

1

Let emitter supply voltage VE is slowly

increased. When VE

becomes equal to η VBB,

Emitter current IE will

reduced to zero.

1

92

WORKING OF UJT(contd.)

AEI302.42 93

1

With equal voltage levels on each side of diode neither reverse nor forward current will flow.

When emitter voltage VE is

further increased, the diode becomes forward biased as soon as it exceeds to the reverse voltage ηVBB+VD.

1

93

WORKING OF UJT(contd.)

AEI302.42 94

1

This value of Emitter voltage VB is called peak point voltage and denoted by VP.

VP= ηVBB+VD.

N-type Uni junction transistor

94

WORKING OF UJT(contd.)

AEI302.42 95

When VE=VP emitter current starts to flow through RB1, this minimum current that is required to trigger the UJT is called peak point emitter current IP.

95

WORKING OF UJT(contd.)

AEI302.42 96

1

When emitter voltage exceeds ηVBB+VD then emitter diode starts conducting.

When the emitter diode starts conduction, charge carriers are injected into RB1 region of the bar. Hence the resistor of RB1 decreases rapidly due to additional charge carriers.

96

WORKING OF UJT(contd.)

AEI302.42 97

1

With this decrease in resistance the voltage drop across RB1 decreases. This decrease of voltage causes the emitter diode to be heavily forward biased.

1

97

WORKING OF UJT(contd.)

AEI302.42 98

1

This results large forward

current, consequently more

charge carries are injected in RB1

region. This causes further

reduction in the resistance of the

RB1 region.

1

98

WORKING OF UJT(contd.)

AEI302.42 99

1 Thus the emitter current goes on increasing and limited by emitter power supply. The emitter voltage VE decreases

with the increase in emitter current.

1

99

WORKING OF UJT(contd.)

AEI302.42 100

1

Hence UJT exhibits negative resistance characteristic. UJT is usually triggered into conduction by applying suitable positive pulse to the emitter.

1

100

WORKING OF UJT(contd.)

AEI302.42 101

1 It can be turned off by applying a

negative trigger pulse.

The Base-2 (B2) is used only for

applying external voltage VBB

across it.

1

101

WORKING OF UJT(contd.)

AEI302.43

102

V-I CHARACTERISTICS OF UJT

Circuit setup Equivalent circuit

Fig .3 (a) Fig.3 (b)

AEI302.43

103

When emitter voltage VE is less

than peak voltage the emitter

diode is reverse biased.

V-I CHARACTERISTICS OF UJT

AEI302.43 104

Current flows into the emitter because of minority charge carriers i.e. reverse leakage current.

This region shown in characteristic curve is called the cut-off region.

1

1

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 105

When conduction is

established at VE=VP the emitter potential VE starts

decreasing with increase in

emitter current IE.

1

1

1

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 106

1

As soon as emitter current

begins to flow the region

between the emitter junction

and Base-1(B1) is flooded by

holes i.e. positive charge

carriers from the heavily doped

P-region .

0

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 107

Consequently it’s conductivity goes up and the

resistance of the region RB1

decreases a lot.

This in turn decreases the emitter to Base voltage and increases emitter current.

10

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 108

This phenomenon

continuous until the

emitter to base voltage VE

becomes very small. This

voltage is called valley point

emitter voltage.

0

0

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 109

The region between peak

point to valley point is

called negative resistance

region.

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 110

Once the valley point

reached any further

increase in emitter

current, places the device

in saturation.

0

0

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 111

Peak point emitter current (Ip) It is the emitter current at which

UJT is driven into on state.

It represents the minimum current that is required to trigger the UJT. It is inversely proportional to the inter

base voltage VBB.

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 112

VALLY POINT VOLTAGE (VV)

The valley point voltage is the emitter voltage at which UJT goes into saturation.

• The valley voltage

increases with increase in

inter base voltage VBB

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.43 113

0

Vally point current (IV)

The valley point current is the minimum emitter current at which UJT goes into saturation.

It increases with increase in inter-base voltage VBB.

0

V-I CHARACTERISTICS OF UJT (contd.)

AEI302.44 114

APPLICATIONS OF UJT

• Phase control.

• Relaxation oscillator.

• Timing circuits.

• Switching.

AEI302.44 115

• Pulse generation.

• Sine wave generator.

• Voltage or current regulator supplies.

APPLICATIONS OF UJT

AEI302.44 116

FEATURES OF UJT

• A stable triggering voltage i.e., a fixed fraction of applied

inter base voltage VBB

• A very low value of triggering current.

AEI302.44 117

• A high pulse current capability.

• A negative resistance characteristic.

• Low cost.

FEATURES OF UJT