EE201L ClassNotes Ch10 Counters transparencies · 2016. 4. 28. ·...

Transcript of EE201L ClassNotes Ch10 Counters transparencies · 2016. 4. 28. ·...

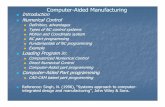

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 1 / 8C Copyright 2006 Gandhi Puvvada

Chapter 10Counters (a short discussion)

1 Decimal count sequence:

Ex: 788, 789, 790, . . .

Ex: 798, 799, 800, . . .

Generalization:

2 Binary count sequence:

In a multi-bit up counter, a bit (such as Q2) will flip (in-crement) when all its right neighbors (Q1 and Q0) are________________ (all 1’s / all 0’s).

In a multi-bit down counter, a bit (such as Q2) will flip(decrement) when all its right neighbors (Q1 and Q0)are ________________ (all 1’s / all 0’s).

3 Basic element in building a counter: A toggle flip-flop

A JK FF with its J and K tied to ________________ (0,0 / 1,1) acts as a toggle FF.

If the J and K are tied to ________________ (0,0 / 1,1), the FF remains stay put.

4 Ripple counter

Which of the following is an up-counter and which is a down-counter? Whatare the rest?Do you call the counter a positive-edge triggered counter or a negative-edge triggered counter or a mixed-edge triggered counter? Whey are these called ripple counters?

01

100

1 10

010101 0

1100

1 10

010101

Q2 Q1 Q0 Q2 Q1 Q0

J QCLK

Q K

J QCLK

Q K

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 2 / 8C Copyright 2006 Gandhi Puvvada

The above 4 hook-ups are reproduced below with an inverter in clock input of the left-most FF. Answerthe same question for these 4 hook-ups.

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

CLK

CLK

CLK

CLK

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

CLK

CLK

CLK

CLK

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 2 / 8C Copyright 2006 Gandhi Puvvada

The above 4 hook-ups are reproduced below with an inverter in clock input of the left-most FF. Answerthe same question for these 4 hook-ups.

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

CLK

CLK

CLK

CLK

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

J QCLK

Q K

VCC

VCC

CLK

CLK

CLK

CLK

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 3 / 8C Copyright 2006 Gandhi Puvvada

5 Building a toggle flip-flop using a D-FF

Which of the following D-FF hook-ups act as a toggle FF? How do you describe the others?

Which of the following D-latch hook-ups act as a toggle latches!? How do you describe the others?

6 Ripple counter using D-FFs

In lab #4, you built a ripple counter, using negative-edge triggered JK Flip-Flops.Build a 4-bit ripple UP counter using the four D-FF hookups given below. This counter shall count-upwhenever the sysclk produces a positive edge. Label the four outputs RQ3RQ2RQ1RQ0 (RQ0 is the LSB. "R" stands for "ripple).

To change the above design so as to make the counter to count on the negative edges of the sysclk,would you change just one of the four FFs to a negative-edge triggered FF or all the four? If one, which one?

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

DQ

CL

K

sysclk

Q

DQ

CL

KQ

DQ

CL

KQ

DQ

CL

KQ

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 3 / 8C Copyright 2006 Gandhi Puvvada

5 Building a toggle flip-flop using a D-FF

Which of the following D-FF hook-ups act as a toggle FF? How do you describe the others?

Which of the following D-latch hook-ups act as a toggle latches!? How do you describe the others?

6 Ripple counter using D-FFs

In lab #4, you built a ripple counter, using negative-edge triggered JK Flip-Flops.Build a 4-bit ripple UP counter using the four D-FF hookups given below. This counter shall count-upwhenever the sysclk produces a positive edge. Label the four outputs RQ3RQ2RQ1RQ0 (RQ0 is the LSB. "R" stands for "ripple).

To change the above design so as to make the counter to count on the negative edges of the sysclk,would you change just one of the four FFs to a negative-edge triggered FF or all the four? If one, which one?

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

D QCLK

Q

DQ

CL

K

sysclk

Q

DQ

CL

KQ

DQ

CL

KQ

DQ

CL

KQ

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 4 / 8C Copyright 2006 Gandhi Puvvada

7 Ripple counter vs. Synchronous counter:

You may have seen in one of the episodes of "I love Lucy". Lucy tries to dance by lookingat other dancers rather than by following the beat of the drum.

If the FF propagation delay is 1 ns, then, in the case of a 32-bit ripple counter

In the case of a synchronous counter design, each FF shall be prepared individually to toggle if appro-priate on the tick of the next clock.

8 A synchronous counter with CLR, LOAD, and EN controls

To build the three bit incrementer, do you need 3 full-adders or 3 half-adders? __________________

D Q

I00I01I02

I10I11I12

Y0Y1Y2

S

A0A1A2

B0B1B2 S0

S1S2

AdderMux

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

001

Most Significant

Least Significant

BA0BA1BA2

LOAD

Register

000

2 1 Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

3

CLR

CLK

A0A1A2

B0B1B2 S0

S1S2

Adder

001

A0

A1

A2

S0

S1

S2

NC(no connection)

1

Simplify this further!

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 4 / 8C Copyright 2006 Gandhi Puvvada

7 Ripple counter vs. Synchronous counter:

You may have seen in one of the episodes of "I love Lucy". Lucy tries to dance by lookingat other dancers rather than by following the beat of the drum.

If the FF propagation delay is 1 ns, then, in the case of a 32-bit ripple counter

In the case of a synchronous counter design, each FF shall be prepared individually to toggle if appro-priate on the tick of the next clock.

8 A synchronous counter with CLR, LOAD, and EN controls

To build the three bit incrementer, do you need 3 full-adders or 3 half-adders? __________________

D Q

I00I01I02

I10I11I12

Y0Y1Y2

S

A0A1A2

B0B1B2 S0

S1S2

AdderMux

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

001

Most Significant

Least Significant

BA0BA1BA2

LOAD

Register

000

2 1 Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

3

CLR

CLK

A0A1A2

B0B1B2 S0

S1S2

Adder

001

A0

A1

A2

S0

S1

S2

NC(no connection)

1

Simplify this further!

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 5 / 8C Copyright 2006 Gandhi Puvvada

9 A 4-bit free-running synchronous counter

10 Transitional values at the output of counters during transition

all 1’s (1111_1111_1111_1111) rolling over to all 0’s (0000_0000_0000_0000),

is it possible that any 16-bit number may appear at the output of the counter for a very short time during the transition? ___________ (Yes / No).Does your answer assume that the counter is a ripple counter or a synchronous counter or any of the two types? ________________________ Is there any harm due to these transitional values? ____________________________________________________________________

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

001

Most Significant

RegisterQ0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

CLK

D QQ3* Q3

B3

A3

S3

D QCLK

D QCLK

D QCLK

D QCLK

sysclk

sysclk

sysclk

sysclk

D QCLKsysclk

Instead of looking at half-adders building an incre-menter, you can explain the design slightly differently.

The XOR gate in front of the D-FF acts like an inverterif the control input is a 1. Else (if the control input is azero), it (the XOR gate) acts like a non-inverter. So basically, the control input (CTRL) is telling the D-FF (through the XOR gate) whether it should be tog-gling on the next clock.

CTRLi Qi

Label the outputs

Q

Q

Q

Q

CTRLi = Qi-1 . Qi-2 . . . . . Q0

Can you replace this with a 3-input and gate to improve performance?

D QCLKsysclk

Make a 5-bit counter using this building block.

0

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 5 / 8C Copyright 2006 Gandhi Puvvada

9 A 4-bit free-running synchronous counter

10 Transitional values at the output of counters during transition

all 1’s (1111_1111_1111_1111) rolling over to all 0’s (0000_0000_0000_0000),

is it possible that any 16-bit number may appear at the output of the counter for a very short time during the transition? ___________ (Yes / No).Does your answer assume that the counter is a ripple counter or a synchronous counter or any of the two types? ________________________ Is there any harm due to these transitional values? ____________________________________________________________________

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

001

Most Significant

RegisterQ0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

CLK

D QQ3* Q3

B3

A3

S3

D QCLK

D QCLK

D QCLK

D QCLK

sysclk

sysclk

sysclk

sysclk

D QCLKsysclk

Instead of looking at half-adders building an incre-menter, you can explain the design slightly differently.

The XOR gate in front of the D-FF acts like an inverterif the control input is a 1. Else (if the control input is azero), it (the XOR gate) acts like a non-inverter. So basically, the control input (CTRL) is telling the D-FF (through the XOR gate) whether it should be tog-gling on the next clock.

CTRLi Qi

Label the outputs

Q

Q

Q

Q

CTRLi = Qi-1 . Qi-2 . . . . . Q0

Can you replace this with a 3-input and gate to improve performance?

D QCLKsysclk

Make a 5-bit counter using this building block.

0

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 6 / 8C Copyright 2006 Gandhi Puvvada

11 Enable control

Consider the following two designs. Are they both right designs? Is one of them better if you want to build a "fast" counter?

12 Truncated Counters

Complete the following two incomplete designs of a truncated counter with 5 states 0, 1, 2, 3, 4, (from4 back to 0). Which is better if we want to build a "fast" counter.

13 Special 3-bit counter skipping 0, 1, and 2 ( 3, 4, 5, 6, 7, 3, 4, 5, 6, 7, . . .)

Complete the following two designs. Why one of them is a "bad" design?

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

CLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

00

Most Significant

Least SignificantRegister

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

ENCLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

001

Most Significant

Least SignificantRegister

000

1 Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

CLR

CLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

001

Most Significant

Least SignificantRegister

000

1 Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

CLR

CLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

001

Most Significant

Least SignificantRegister

110

1 Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

LOAD

CLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

001

Most Significant

Least Significant Register

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

CLK

PRE

PRE

CLR

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 6 / 8C Copyright 2006 Gandhi Puvvada

11 Enable control

Consider the following two designs. Are they both right designs? Is one of them better if you want to build a "fast" counter?

12 Truncated Counters

Complete the following two incomplete designs of a truncated counter with 5 states 0, 1, 2, 3, 4, (from4 back to 0). Which is better if we want to build a "fast" counter.

13 Special 3-bit counter skipping 0, 1, and 2 ( 3, 4, 5, 6, 7, 3, 4, 5, 6, 7, . . .)

Complete the following two designs. Why one of them is a "bad" design?

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

CLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

00

Most Significant

Least SignificantRegister

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

ENCLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

001

Most Significant

Least SignificantRegister

000

1 Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

CLR

CLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

001

Most Significant

Least SignificantRegister

000

1 Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

CLR

CLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

001

Most Significant

Least SignificantRegister

110

1 Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

LOAD

CLK

D Q

A0A1A2

B0B1B2

S0S1S2

Adder

001

Most Significant

Least Significant Register

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

CLK

PRE

PRE

CLR

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 7 / 8C Copyright 2006 Gandhi Puvvada

14 Cascading Counters: Build a 6-bit counter by cascading two 3-bit counters

Try completing this alternative design and also criticize the same.

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

CLK

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q3

Q4

Q5

D Q

D Q

Q3*

Q4*

Q5*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

CLK

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

CLK

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q3

Q4

Q5

D Q

D Q

Q3*

Q4*

Q5*

EN_CLK

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 7 / 8C Copyright 2006 Gandhi Puvvada

14 Cascading Counters: Build a 6-bit counter by cascading two 3-bit counters

Try completing this alternative design and also criticize the same.

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

CLK

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q3

Q4

Q5

D Q

D Q

Q3*

Q4*

Q5*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

CLK

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q0

Q1

Q2

D Q

D Q

Q0*

Q1*

Q2*

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

EN

CLK

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

Least SignificantRegister

Q3

Q4

Q5

D Q

D Q

Q3*

Q4*

Q5*

EN_CLK

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 8 / 8C Copyright 2006 Gandhi Puvvada

15 Fix Mr. Bruin, I mean, Mr. Bruin’s design of a stop watch. This stop watch goes from 0:00 to 1:59 (1 Min. 59 Sec.) and rolls back to 0:00. It has a CLEAR and START/STOP controls.

16 Timing analysis of a counter

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

RegisterQS0

QS1

QS2

D Q

D Q

QS0*

QS1*

QS2*

CLK

D QQS3* QS3

B3

A3

S3

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

000

Y3

I130

I03

0

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

Y3

I13

I03

EN CLR

START/STOP

Least Significant

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

RegisterQTS0

QTS1

QTS2

D Q

D Q

QTS0*

QTS1*

QTS2*

CLK

D QQTS3* QTS3

B3

A3

S3

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

000

Y3

I130

I03

0

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

Y3

I13

I03

EN CLR

Least Significant

CLEAR

CLEAR

D QCLKCLK

QM

EE201L_ClassNotes_Ch10_Counters_transparencies.fm

4/24/06 EE201L Class Notes - Chapter #10 Counters Page 8 / 8C Copyright 2006 Gandhi Puvvada

15 Fix Mr. Bruin, I mean, Mr. Bruin’s design of a stop watch. This stop watch goes from 0:00 to 1:59 (1 Min. 59 Sec.) and rolls back to 0:00. It has a CLEAR and START/STOP controls.

16 Timing analysis of a counter

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

RegisterQS0

QS1

QS2

D Q

D Q

QS0*

QS1*

QS2*

CLK

D QQS3* QS3

B3

A3

S3

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

000

Y3

I130

I03

0

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

Y3

I13

I03

EN CLR

START/STOP

Least Significant

D Q

A0A1A2

B0B1B2 S0

S1S2

Adder

001

Most Significant

RegisterQTS0

QTS1

QTS2

D Q

D Q

QTS0*

QTS1*

QTS2*

CLK

D QQTS3* QTS3

B3

A3

S3

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

000

Y3

I130

I03

0

I00I01I02

I10I11I12

Y0Y1Y2

S

Mux

Y3

I13

I03

EN CLR

Least Significant

CLEAR

CLEAR

D QCLKCLK

QM