DVClub January 18th 2009 Coverage Closure Mike Bartley, TVS

description

Transcript of DVClub January 18th 2009 Coverage Closure Mike Bartley, TVS

Test and Verification Solutions 118th January 2010

DVClub

January 18th 2009

Coverage Closure

Mike Bartley, TVS

2Test and Verification Solutions 218th January 2010

Welcome

• 5th DVClub event– Bristol, UK wide, international

• Next events– Using Design IP – a Verification Perspective– Integration Verification– Using Open Source and Free Verification tools

• Software Test Club• Thank you

– Patrick Thornhill, Bryan Dickman, Rob Williams– Sponsors - UWE, ARM, Infineon, NMI, TVS, Synopsys

• Speakers12.10: Dan Benua, Corporate Application Engineering Manager, Synopsys

12.30: Dr. Giovanni Squillero, Politecnico di Torino

13.00: Avi Ziv, IBM Research Lab at Haifa, Israel

• Survey– 30 respondents!

3Test and Verification Solutions 318th January 2010

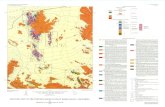

Which coverage metrics do you use for in your dynamic verification flow?

Other coverage metrics used– Certitude– Toggle coverage of integration nets for SoCs– Configuration Coverage– SW Metrics, API Coverage, Interrupt Coverage

0.00%

20.00%

40.00%

60.00%

80.00%

100.00%

Diretced testcoverage

Code Coverage Functional Coverage Assertion Coverage

4Test and Verification Solutions 418th January 2010

Distribution of effort in directed testing

Other areas of effort• Regression management• Covering legacy tests• Praying we haven't forgotten anything

0%

10%

20%

30%

40%

50%

60%

% of effort expended

% o

f re

sp

on

den

ts

Defining directed tests

Writing directed tests

Debugging tests

Signing off holes

5Test and Verification Solutions 518th January 2010

Distribution of effort in code coverage

Other areas of effort• Develop formal coverage closure scripts • Regr mgmt, merging, results collation and display

0%

5%

10%

15%

20%

25%

30%

35%

% of effort expended

% o

f re

sp

on

den

ts

Reviewing coverage achieved

Trying to fill coverage holes

Signing off holes

6Test and Verification Solutions 618th January 2010

Distribution of effort in code coverage

Other areas of effort• Develop formal coverage closure scripts • Regr mgmt, merging, results collation and display

0%

5%

10%

15%

20%

25%

30%

35%

% of effort expended

% o

f re

sp

on

den

ts

Reviewing coverage achieved

Trying to fill coverage holes

Signing off holes

7Test and Verification Solutions 718th January 2010

Distribution of effort in functional coverage

Other areas of effort• Writing the functional coverage • Regr mgmt, merging, resultscollation and display

0%

10%

20%

30%

40%

50%

60%

70%

80%

90%

1 2 3 4 5 6 7 8 9 10 11

% of effort expended

% o

f re

spo

nd

ents

Defining functional coveragepoints

Debugging coverage holes

Reviewing coverage achieved

Trying to fill coverage holes

Signing off holes

8Test and Verification Solutions 818th January 2010

Which platforms do you use to collect your FUNCTIONAL COVERAGE in your dynamic verification flow?

Other platforms• PSL (3)• Home grown (2)• Cadence transaction explorer (TxE)

0%

10%

20%

30%

40%

50%

60%

System Verilog e Other platforms