DSP DesignDSP Design Introduction and DSP Basics · PDF fileDSP DesignDSP Design Introduction...

Transcript of DSP DesignDSP Design Introduction and DSP Basics · PDF fileDSP DesignDSP Design Introduction...

DSP Design

DSP DesignDSP Design

Introduction and DSP Basics

Viktor Öwall

ikt ll@ it [email protected]

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Wh d fi d it?Where do we find it?

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

The first pacemaker 1958Karolinska Institutet, Stockholm

DSP Design

What is a Digital Signal Processor?

• Real time requirement• Data driven

• Works on time discrete sampled data of a continous signal

Data driven

• Programmable or Custom DSPs

• What to use depends on requirements Sample rateTh h tThroughput Power - energy AreaWordlength – precision Flexibility Time to market

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

Volume

DSP Design

Wh d fi d it?Where do we find it?Very Low PowerSample Rate: 8/16kHz

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

Extremely Low PowerSample Rate: <1kHz

Low PowerEx. Sample Rate UMTS filter: 15MHz

DSP Design

f SExample of DSP Applications• Speech & AudioSpeech & Audio

– coding, MP3– recognition

echo cancellation– echo cancellation• Image

– coding, MPEG4– Filtering

• Wireless Communication– Channel coding/decodingg g– Equalization– Channel estimation– Smart antennasSmart antennas

• Beam forming• MIMO, Multiple Input Multiple Output

• Etc Etc Etc

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

• Etc, Etc, Etc...

DSP Design

f SExample of DSP ”Primitives”C• Convolutions

• FiltersFIR– FIR

– IIR– Wave digital

• Correlation• FFT• DCT• LMS – Least Mean Square

t• etc...

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Two Basic DSP Structures

x(n)x(n)

y(n)

D D Dx(n)

h0 h3h2h1D

y(n)D

FIR Fi it I l R IIR I fi it I l RFIR – Finite Impulse Response

4-tap FIR filter

IIR – Infinite Impulse Response

Biquad section

No feedback Feedback

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Often comprised of several DSP primitivesp p- Acoustic Echo Cancellation -

N d l i i l thNo delay in signal path

Delay in coefficient update

S bb d hSubband approach Reduces complexity

and achievesand achievesFaster convergence

Morgan and Thi 1995

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

Morgan and Thi, 1995Anders Berkeman

DSP Design

N f S bb dFor computational complexity the most important parameter

Nr. of SubbandsFor computational complexity the most important parameter is the number of subbands.

FIR 889Mmult/s

LMS

FIRFFT

889Mmult/s

s LMS90%FB

mul

t/s

43Mmult/sFFTFB

1000

LMS

FB FIR76%LMS

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

Nr. of Subbands

DSP Design

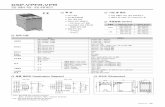

Echo Canceller chipEcho Canceller chip0.35m, 5 Metal Layer CMOS, 2002

DataSample rate = 16kHz

fTarget fclk = 17MHz

128 subbands

>2M transistors (46k cells)

10 RAM - 247kbits10 RAM 247kbits

2 ROM - 29kbits

120 IO120 IO

5.019x5.76mm2 = 29mm2

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

29mm2

DSP Design

Different applications different demandsDifferent applications, different demands...a simplified view

FlexibiltyComplexity

Low powerLow cost

Lower powerLower costComplexity Low cost

FlexibiltyLower cost

Processors Processors ASICs

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

ProcessorsFPGAs

ProcessorsASICs

ASICsProcessors

DSP Design

Standard Processors orStandard Processors orSpecial Purposep p

Algorithm

Standard Processor

SpecialPurpose

• Programable/Flexible• Short design time/TTM

• High calculation capacity• Low power consumptionShort design time/TTM

• Low price?p p

• Low price at volume– What is volume?

Main focus of this CourseViktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

Main focus of this Course

DSP Design

Architectural options• OTS (Off The Shelf) processors

– Programmable microprocessors or DSPB d i t ti l it f DSP ll MAC– Based on generic computational units, for DSPs usually MAC

– Prefabbed or IP cores

• Time-multiplexed application specific processors– Several algorithmic operations performed on same hardware unit– Several algorithmic operations performed on same hardware unit– Trades reduced HW for longer computation time

• Hardware mapped architectures– One (or more) hardware unit per algorithmic operation

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

( ) p g p– High HW cost and high throughput

DSP Design

Time multiplexed to save hardwareTime multiplexed to save hardware

1

0:

N

kknxkhnyFIR

0k

Hardware mappedTime-multiplexed

D D Dx(n)

ppcMUX

h0 h3h2h1

y(n)REG

y( )

1 sample/ccN fixed multipliers

N cc/sample1 generalized multiplier N fixed multipliers

N-1 addersge e a ed u t p e

1 adders1 coefficient memory

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

+ control

DSP Design

Hardware Implementation TechniquesHardwareHardwareSolution

FPGA F ll C tFPGA Full Custom

More on Thursday!

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Thi i l l k tThis course mainly looks at specialized architectures p

Could be used for eitherCould be used for eitherFPGA or ”ASIC”

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Energy Efficiency

One of the key design issues today!

Why energy and not power?

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Utilizing the computation time?

MIPS

• Can we control the clock frequency?

• What power down options do we have?Compute as fast as we can? • What power down options do we have?– clock gating– various sleep modes

Compute as slow

• Can we scale the power supply?– Dynamic– How many levels

as we’re allowed?• What cell library can we choose?

– Low power

TimeMax computationtime

– High speed

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

time

DSP Design

Energy efficiency (MOPS/ W)Energy efficiency (MOPS/mW)

1000

100

1000

es

10

100

a Ef

ficie

ncie

1gy an

d Ar

ea

MicroprocessorsDedicated

0,1

Ener

g DedicatedDesignsGeneral

Purpose DSP’s

0,01

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

Chip Number (see next slide)Courtesy: Professor Bob Brodersen, UC Berkeley

DSP Design

ISSCC Chips (0 18μm –0 25μm)ISSCC Chips (0.18μm –0.25μm)

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Results in fully parallel solutionsResults in fully parallel solutionsReducing supply voltage saves energy: E = CV2

Energy Area

64-point FFTE

16-State Viterbi Decoder

64-point FFTT f d

16-State Viterbi DecoderEnergy per

Transform (nJ) Decoder

Energy per Decoded bit (nJ)

Transforms per second per unit area

(Trans/ms/mm2)

DecoderDecode rate per unit

area (kb/s/mm2)

Direct-Mapped Hardware 1.78 0.022 2,200 200,000

FPGA 683 5.5 1.8 100

Low-Power DSP 436 19.6 4.3 50

High-Performance DSP 1700 108 10 150

(numbers taken from vendor-published benchmarks)Orders of magnitude lower efficiency

even for an optimized processor architecture

1000

5000

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

even for an optimized processor architectureCourtesy Ning Zhang, Berkeley Wireless Research Center (BWRC)

DSP Design

Questions?

Which structure gets the job done?

Which structure use the least energy?

Which structure use the least area?

Et t tEtc, etc, etc...

How do we design architectures to achieve it?How do we design architectures to achieve it?

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

...and now to the course!...and now to the course!

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

ScopeHow to get from a signal processing algorithm to an EFFICIENT

implementation using

– Different numbering systems– Pipelining

P ll li– Parallelism– Unfolding and folding– Strength reduction, i.e. complexity of operations.g p y p– etc, etc,...

in a structured way!in a structured way!

Case studies: FFT, image filtering, acoustic echo cancellation,

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

, g g, ,pacemakers,...

DSP Design

GoalsGoalsAims: Knowledge

After completing the course the student should: – have gained an understanding for the relationship between parameters such as– have gained an understanding for the relationship between parameters such as

calculation capacity, power consumption and silicon area – be familiar with transformations that help the designer to develop different

solutions for a given signal processing algorithm. g g p g g– understand how different number representations affect the solution.

Aims: SkillsAims: SkillsAfter completing the course the student should:

– be able to suggest a processor architecture from a given set of critera. b bl t l hit t d t lt ti l ti– be able to analyze a processor architecture and suggest alternative solutions.

Aims: AttitudeAfter completing the course the student should:

– have gained an overview of the field of implementation aspects of signal processing algorithms.

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

– feel well equipped to design an application specific processor given a specification using the methodologies covered in the course.

DSP Design

LogisticsLogistics• Web: htt // it lth / / ti180• Web: http://www.eit.lth.se/courses/eti180

• LecturesTuesdays 13 15 in MH:A– Tuesdays, 13-15, in MH:A

– Thursdays, 15-17, in E:1406• SeminarsSeminars

– Wednesdays 13-15 and 15-17.• No seminar 1st week• Weeks 2 and 3 in E:2349• Weeks 4 to 7 in E:4116

• Question hours• Question hours– Fridays 10-12 and 13-15

by Reza Meraji, Room E:2336

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Compulsary PartsCompulsary Parts

• 2 labs, planned for weeks 3 and 6 & 7– MATLAB (2 hours)– MATLAB (2 hours)– Hardware design in CatapultC (2 + 2 hours)

• Homework seminars, week 4 and 6

results in grade 3

• Written exam for grade 4 & 5Wednesday December 16 2pm 7pm

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

Wednesday, December 16. 2pm-7pm.

DSP Design

LitteratureLitterature

• Course Litterature– Keshab K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementationg g g y g p

• Extended Reading Al V O h i R ld W S h f ith J h R B k Di t Ti Si l– Alan V. Oppenheim, Ronald W. Schafer with John R. Buck, Discrete-Time Signal Processing, Prentice Hall, 1999, ISBN 0-13-754920-2.

– John G. Proakis and Dimitris Manolakis, Digital Signal Processing: Principles, Algorithms and Applications Prentice Hall 1995 ISBN 0133737624Algorithms and Applications, Prentice Hall, 1995, ISBN 0133737624.

– Sanjit K. Mitra, Digital Signal Processing. A Computer Based Approach, McGRAW-HILL, 2001 ISBN: 0-07-118175-X

– Lars Wanhammar, DSP Integrated Circuits, Academic Press, 1999, ISBN 0-12-734530-2Lars Wanhammar, DSP Integrated Circuits, Academic Press, 1999, ISBN 0 12 734530 2

S

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

• Seminar exercises and Lab manual will be available on the web.

DSP Design

MapMapE-building2nd floor2nd floor

Reza

Viktor, 3rd floor

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Digital ComplexityDigital Complexity

some examples from Wireless SystemsWireless Systems

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

The Evolving Wireless SceneThe Evolving Wireless SceneMore bit/($·nJ)More bit/($·nJ)

100Mb

More bit/secMore bit/sec

One solution10Mb

802 11 (LAN)

802.1aMetropolitan

One solution cannot fit all systems!

a Rate

100Kb

1Mb3G Cellular

802.11 (LAN)

Bluetooth (PAN)

y

Data

10Kb

100Kb

2.5 G Cellular

1KbCellular (WAN)Sensor networks

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.seRange

1m 10m 100m 1km 10kmCourtesy: Prof. Jan Rabaey, BWRC

DSP Design

OFDMOFDMkx ,0

ks ,0

snt

IDFT

l to

seria

l

kx ,1

CP

ks ,1

N-p

oin

Par

alle

x kNs ,1kNx ,1

,

Large number of subcarriers large FFT

OFDM:• DVB-2/4/8k FFT• WLAN IEEE802.11a/g-64 FFT (48+4 subcarriers)

LTE L T E l i

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

• LTE – Long Term Evolution

DSP Design

The Cost of Approaching Shannon’s Bound

100000

xity

1/2 LDPC, N=107, 1100 iterationsfor BER of 10-5

1000

10000

mpl

ex

8/9 Capacity Bound

/ , ,

100

ve C

o

8/9 Turbo, =4, N=4k

2/3 Turbo, =4, N=64k 1,2, and 3 iterations

2/3 Capacity Bound1/2 Capacity Bound

10

Rel

ati

1/2 Turbo, =4, N=64k 1,2, and 3 iterations

8/9 LDPC, N=4k 1,3, 8/9 Conv. Code,

1/2 Conv. Code, =4, N=64k

2/3 Conv. Code, =4, N=64k

10 2 4 6 8 10 12

SNR (db)

8/9 LDPC, N 4k 1,3, and 5 iterations =3, N=4k

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

SNR (db)Courtesy Engling Yeo, UCB

DSP Design

The Cost of Approaching Shannon’s Bound

100000

xity 1/2 LDPC, N=107, 1100 iterations

for BER of 10-5

1000

10000

mpl

ex

/ , ,

100

ve C

om 1/2 Turbo, =4, N=64k 1,2, and 3 iterations1/2 Capacity Bound

10

Rel

ativ

1/2 Conv. Code, =4, N=64k

10 2 4 6 8 10 12

SNR (db)

R

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

SNR (db)Courtesy Engling Yeo, UCB

DSP Design

Multiple Antenna Systems – e.g. MIMOTx Rx High complexity

receiver

Multiple Antenna Systems e.g. MIMO

Tx

T

DataRx

R

Symbol Detection

r = Hs + n s = H-1r^ ^S/P

Tx

Tx

Rx

Rx Channel Estimation

Matrix Inversion

HH-1^

Estimation Inversion

PE PE PEPE PEInversion of

PE PE PE

PE PE

PE

PE PE

PE

PE

triangular sub-matrix• Multi-antenna approach exploits

multi-path by sending data along several channels

QR-factorisation

PEPE

PE PE

PE

PE

PE

PE

PE

PE

• Results in large theoretical improvements in bandwidth efficiency for fading channels

• But…computationally hungry

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

But…computationally hungry

DSP Design

MIMO Hardware perspectiveMIMO Hardware perspectiveRxTx

RxSymbol

Detection

r = Hs + n s = H-1r^ ^TxData

S/PRx

Rx

Detection

Channel Estimation

Matrix Inversion

HH-1^Tx

Tx

WLAN 802.11n ExampleModulation 256QAM; 4 Tx antennas; 108 sub-channels 4s per symbolModulation 256QAM; 4 Tx antennas; 108 sub-channels, 4s per symbolML detection 1.159 x 1017 lattice points/secCurrent DSP technology is 1G inst/s 108 processors!gy pOR (“Moores Law” ..... processor capability doubles every 18 months)

MUST WAIT 40years!

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

From Mike Faulkner, Victoria Univ.

DSP Design

RTrading Complexity – 4x4 antennasRTrading Complexity 4x4 antennas

BEER Sub-optimal QPSK

(square-root) 0 35 μm(square root) 0.35 μm

Sphere 16QAM 0.35 μmML-detection

#mult/

ML detection

S ft O t t

symbol

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

+ Soft Output 0.13 μm

DSP Design

Sphere DecodingSphere Decoding

Simplified 2D-caseML Detection Sphere Detection

Simplified 2D-case

Limited search space reduced complexity

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Looking at ComplexityLooking at Complexity

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Isn’t Moore Enough?The number of transistors

Isn’t Moore Enough?Moores´s Law

The number of transistors per chip will double every year.

(1965)(1965)... in 1975 changes to every 2 years

Gordon MooreOne of the founders of Intel

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

Technology roadmap: http://www.itrs.net/

DSP Design

Algorithms beats Moore beats ChemistsAlgorithms beats Moore beats Chemists10000000 Algorithmic Complexity

100000

1000000 Processor Performance (~Moore’s Law)

3G

10000

100000

100

1000 2G

10Battery Capacity

1G1

1980

1984

1988

1992

1996

2000

2004

2008

2012

2016

2020

1G

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

1 1 1 1 1 2 2 2 2 2 2

Courtesy: Ravi Subramanian (Morphics)

DSP Design

C l itComplexityComplexity of Algorithms are increasing

with new systemsyNumber of transistors possible to implement

on a die is incresing (Moore’s law)on a die is incresing (Moore s law)

Often mature algorithms (systems) go to non custom solutionsnon-custom solutions.

But there is always new algorithms

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

and there is power and price...

DSP Design

Evolution

• Mature systemsi e low performance compared to state of the art– i.e. low performance compared to state of the art

– implemented on standard platformsmature technologies– mature technologies

– ex. GSM

• New systems– i e high performancei.e. high performance– use non-standard architectures and components– ex. 3G or new generations...

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

ex. 3G or new generations...

DSP Design

DSP basicsDSP basics

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Digital signal processing algorithms works on samples of a continous signals.samples of a continous signals.

Sampling rate = nr. of samples processed/secondSampling rate nr. of samples processed/second

Analog

DigitalSignal

Continoussignal

DigitalSignal

Processing

Sampledsignal

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Two Basic DSP Structures

x(n)x(n)

y(n)

D D Dx(n)

h0 h3h2h1D

y(n)D

FIR Fi it I l R IIR I fi it I l RFIR – Finite Impulse Response

4-tap FIR filter

IIR – Infinite Impulse Response

Biquad section

No feedback Feedback

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

Th FIR filtThe FIR filter

1N

knxkhny

0k

knxkhny

h( ) is the impulse response which definesh(.) is the impulse response which defines the filter response, e.g. low- or highpass.

x(n) x(n-1) x(n-2) x(n-3)D D D

x(n)

h0 h3h2h1

x(n 1) x(n 2) x(n 3)

h0 h3h2h1

y(0)

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(0)

DSP Design

Th FIR filtThe FIR filterD D Dx(n) D D D

h0 h3h2h1

y(n)

A higher order filter, more taps, will result in a steeper filter function but has higher complexity!

The filter order is nr. of taps - 1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

FIR filter in MatlabFIR filter in MatlabD D Dx(n)

h0 h3h2h1

y(n)y( )

FIR-filters can be designed withfir1(N,Wn) – N’th order filter with the cut-off frequency Wn must ( ) q ybe between 0 < Wn < 1.0, with 1.0 corresponding to half the sample rate.

0 250 12

0 15

0.2

0.25

0.08

0.1

0.12

32-taps 8-order

0 05

0.1

0.15

0.02

0.04

0.06

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se1 2 3 4 5 6 7 8 9

0

0.05

0 5 10 15 20 25 30 35-0.02

0

DSP Design

FIR-filter frequency responseUse fft to transform h(.) to

1.4

Use fft to transform h(.) to frequency domain and plot.

1

1.2 32-taps8-taps

0.8

1

0.4

0.6

0 200 400 600 800 1000 12000

0.2

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

Symmetry when real input to fft.

DSP Design

Linear phase FIR filtersLinear phase FIR filters0.6

0.8

1

0.08

0.1

0.12

-0.2

0

0.2

0.4

0

0.02

0.04

0.06

0 5 10 15 20 25 30 35-0.4

Linear phase filters has a constant group delay in the passband, i.e. all frequency components are delayed equally no phase distortion.Li h filt f fi 1() h t i ffi i t

0 5 10 15 20 25 30 35-0.02

Linear phase filters, e.g. from fir1(), has symmetric coefficients.This can be used to simplify the filter structure.

Dx(n) DDDx(n)

D

D D

D

h0 h2h1 h4

y(n)

h3

y(n)

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(n) y( )

DSP Design

The FIR filter hardware mappedThe FIR filter, hardware mapped

1N

0k

knxkhny

)3()2()1()0()0( 3210 xhxhxhxhy

R R R

clock

x(0) x(-1) x(-2) x(-3)REG

REG

REG

h0 h3h2h1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(0)

DSP Design

Th FIR filtThe FIR filter

The input samples have been delayed one time unit, i.e. clock cycle!

, y

0 1 2 31 1 0 1 2y h x h x h x h x

D D Dx(1)

h0 h3h2h1

x(0) x(-1) x(-2)

h0 h3h2h1

y(1)

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

The FIR filter next clock cycleThe FIR filter, next clock cycle

1N

0k

knxkhny

)2()1()0()1()1( 3210 xhxhxhxhy

R R R

clock

x(1) x(0) x(-1) x(-2)REG

REG

REG

h0 h3h2h1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(1)

DSP Design

Ti lti l d t h dTime multiplexed to save hardware1N

1

0:

N

kknxkhnyFIR

0k

D D Dx(n)cMUX

h0 h3h2h1

( )

REG

y(n)

1 sample/ccN fi d lti li

N cc/sample1 generalized multiplierN fixed multipliers

N-1 adders

g p1 adders1 coefficient memory

t l

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

+ control

DSP Design

Ti lti l d t h dTime multiplexed to save hardwareSample

x(n)

SampleMem

0How many clock cycles?

coeffMUX

( )

Why the ”0”?

Why the extra reg?REG

D D Dx(n)

y(n)

REG D D D( )

h0 h3h2h1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(n)

DSP Design

Ti lti l d t h dTime multiplexed to save hardwareSample 0 (0)h(0) 0

x(0)

SampleMem

0

cc0: x(0)h(0)+0

coeffMUX

( )

h(0)h(0)

REG

D D Dx(n)

y(-1)

REG D D D( )

h0 h3h2h1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(n)

DSP Design

Ti lti l d t h dTime multiplexed to save hardwareSample 0 (0)h(0) 0

x(-1)

SampleMem

cc0: x(0)h(0)+0

cc1: x(-1)h(1)+x(0)h(0)x(0)h(0)

coeffMUX

( )

h(1)h(1)

REG

D D Dx(n)

y(-1)

REG D D D( )

h0 h3h2h1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(n)

DSP Design

Ti lti l d t h dTime multiplexed to save hardwareSample 0 (0)h(0) 0

x(-2)

SampleMem

cc0: x(0)h(0)+0

cc1: x(-1)h(1)+x(0)h(0)x(-1)h(1)+ x(0)h(0)

cc2: x( 2)h(2)+ x( 1)h(1)+x(0)h(0)coeffMUX

( )

h(2)

cc2: x(-2)h(2)+ x(-1)h(1)+x(0)h(0)

h(2)

REG

D D Dx(n)

y(-1)

REG D D D( )

h0 h3h2h1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(n)

DSP Design

Ti lti l d t h dTime multiplexed to save hardwareSample 0 (0)h(0) 0

x(-3)

SampleMem

cc0: x(0)h(0)+0

cc1: x(-1)h(1)+x(0)h(0)x(-2)h(2)+ x(-1)h(1)+ x(0)h(0)

cc2: x( 2)h(2)+ x( 1)h(1)+x(0)h(0)coeffMUX

( )

h(3)

cc2: x(-2)h(2)+ x(-1)h(1)+x(0)h(0)cc3: x(-3)h(3)+ x(-2)h(2)+ x(-1)h(1)+x(0)h(0)

h(3)

REG

D D Dx(n)

y(-1)

REG D D D( )

h0 h3h2h1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(n)

DSP Design

Ti lti l d t h dTime multiplexed to save hardwareSample 0 (0)h(0) 0

x(1)

SampleMem

cc0: x(0)h(0)+0

cc1: x(-1)h(1)+x(0)h(0)

cc2: x( 2)h(2)+ x( 1)h(1)+x(0)h(0)0

coeffMUX

( )

h(0)

cc2: x(-2)h(2)+ x(-1)h(1)+x(0)h(0)cc3: x(-3)h(3)+ x(-2)h(2)+ x(-1)h(1)+x(0)h(0)

cc4: x(1)h(0)+0; new iterationh(0) cc4: x(1)h(0)+0; new iteration

REG

D D Dx(n)

y(0)

REG D D D( )

h0 h3h2h1

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(n)

DSP Design

Ti lti l d t h dTime multiplexed to save hardwareSample

x(n)

SampleMem

0

CONTROLsample

coeffMUX

( )

FSMFinite State Machine

address

Finite State Machinereset

REG

D D Dx(n)load

y(n)

REG D D D( )

h0 h3h2h1

load

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

y(n)

DSP Design

The IIR filter, direct form IThe IIR filter, direct form I

m n

y n b x n i a y n j The impulse response also includes feedback terms.

0 1

i ji j

y n b x n i a y n j

y(n)x(n) b0 y(n)x(n)

Z-1

+0

b1Z-1

+

a1

Z-1+

b1

Z-1+

a1

Z 1

+bm-1

Z 1

+an-1

Z-1

bmZ-1

an

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

• Steeper impulse response but possibility for unstability

DSP Design

The IIR filter direct form IIThe IIR filter, direct form II

m n

i jy n b x n i a y n j 0 1

i ji j

Each part is a linear time-invariant system d th d b dand the order can be reversed.

x(n)+

b0 y(n)+

Z-1

+

+b1

Z-1

+a1

Z-1+

b 1

Z-1+

a 1

Z-1+

bm-1

bZ-1+

an-1

a

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

bman

DSP Design

The IIR filter direct form IIThe IIR filter, direct form II

m n

i jy n b x n i a y n j 0 1

i ji j

y y j

The two parts can be collapsed into one with a minimum number of delay elements.

x(n) + +y(n)b0

Z-1

+

+a1

+

+b1

Z-1+ +

b

Z-1

+an-1

+bm-1

b

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

an bm

DSP Design

The IIR filter cascade formThe IIR filter, cascade form1 2sN b b b 1 2

0 1 21 2

1 1 2

; 1 / 21

sNk k k

k k k

b b z b zH z Ns Na z a z

1 1 2k k k

x(n) y(n)

D

D

D

D

D

DD D D

• Often cascaded with shorter sections which are combined,easier to design when fixed-point arithmetic.

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

g p• The above is often referred to as biquad sections.

DSP Design

DFT - FFT

• The DFT/FFT is one of the most common digital signal processing algorithmsprocessing algorithms.

• Used to determine frequency content of a discrete signal• Used to determine frequency content of a discrete signal sequence.

• Transform between time and frequency domains.

• The FFT is a low complexity way of computing the DFT.

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

DSP Design

N-point DFTN point DFT

110)()(1

NkWkXN

kn Nknjkn eW /21,...,1,0,)()(0

NkWnxkXn

knN

jN eW

N filt f l th N O(N2)Complex

N filters of length N O(N2)

Nx(n) X(0)

p

NOnly every Nth sample

( )X(1)

N X(N-1)

• The DFT determines spectral content at N equally spaced frequency points, p q y p q y pi.e. coorelates with different frequencies,

( ) sampleanalysis

mff m

N

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

• N samples are needed.

DSP Design

FFT is low complexity DFTX(0)

X(8)

x(0)

x(1)

FFT is low complexity DFT

X(12)

X(4)

X(8)

x(3)

x(2)

x(1)

W 0

W 4

X(2)

X(6)

X(10)W 2

W 6

x(4)

x(6)

x(5)

W 0

W 0

stages)(log2 N

X(1)

X(9)

x(8)

(9)

W 8X(14)

6

x(7)

W 0

0

W 4)( 2NODFT

X(13)

X(5)

X(9)

x(11)

x(10)

x(9)

W 3

W 1

W 2 W 0

W 4)(log

2 2 NNFFT

X(3)

X(7)

X(11)

x(12)

x(14)

x(13) W 5

W 4

W 2

W 0

2FFT

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden - www.eit.lth.se

X(15)

X(7)

x(15)

x(14)

W 7

W 6

W 6

W 4 W 0

W 4