Designing Fibonacci Sequence Using Verilog.

-

Upload

deardestiny -

Category

Documents

-

view

1.299 -

download

40

Transcript of Designing Fibonacci Sequence Using Verilog.

-

7/30/2019 Designing Fibonacci Sequence Using Verilog.

1/8

1

1. AIM: To design Fibonacci Sequence using Verilog.2. SOFTWARES USED:Xilinx Synthesis Tool ISE 9.2i3. INTRODUCTIONHardware description language (HDL) is a general-purpose language intended to describecircuits textually, for a computer to read. In electronics, a hardware description language or HDL

is a specialized computer language used to describe the structure, design and operation of

electronic circuits, and most commonly, digital logic circuits. A hardware description language

enables a precise, formal description of an electronic circuit that allows for the automated

analysis, simulation, and simulated testing of an electronic circuit. It also allows for the

compilation of an HDL program into a lower level specification of physical electronic

components, such as the set of masks used to create an integrated circuit.

Hardware description languages such as Verilog HDL and VHDL are very popular today.

Verilog HDL originated in 1983 at Gateway Design Automation. Later, VHDL was developed

under contract from DARPA. Initially a proprietary language, but became open standard in early

1990s, then IEEE standard ("1364") in 1995, revised in 2002, and again in 2005. Today Verilog

HDL is an accepted IEEE standard.

A Verilog HDL is a general-purpose hardware description language similar to C programming

language. It is a textual description consisting of expressions, statements and control structures.

One important difference between most programming languages and HDLs is that HDLs

explicitly include the notion of time. HDLs form an integral part of Electronic design automation

systems, especially for complex circuits, such as microprocessor.

-

7/30/2019 Designing Fibonacci Sequence Using Verilog.

2/8

2

3.1.TYPICAL DESIGN FLOW OF HDL

Fig. Typical design flow of Hdl

A Verilog design consists of a hierarchy of modules. Modules encapsulate design hierarchy, and

communicate with other modules through a set of declared input, output, and bidirectional ports.

Internally, a module can contain any combination of the following: net/variable declarations (wire,

reg, integer, etc.), concurrent and sequential statement blocks, and instances of other modules

(sub-hierarchies). Sequential statements are placed inside a begin/end block and executed in

sequential order within the block. However, the blocks themselves are executed concurrently,

making Verilog a dataflow language.

-

7/30/2019 Designing Fibonacci Sequence Using Verilog.

3/8

3

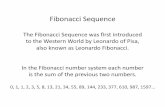

3.2.FIBONACCI SEQUENCE

The Fibonacci Series is a sequence of numbers first created by Leonardo Fibonacci in 1202. It is a

deceptively simple series, but its ramifications and applications are nearly limitless. It has

fascinated and perplexed mathematicians for over 700 years, and nearly everyone who has worked

with it has added a new piece to the Fibonacci puzzle, a new tidbit of information about the series

and how it works. By definition, the first two numbers in the Fibonacci sequence are 0 and 1, and

each subsequent number is the sum of the previous two.

By definition of fibonacci, the first two numbers are :

Fibonacci(0)= 0

Fibonacci(1)=1

The next number is always the sum of the previous two.

Fibonacci(n)=Fibonacci(n-1)+Fibonacci(n-2)

Fibonacci(2)=0+1=1

Fibonacci(3)=1+1=2

Fibonacci(4)=1+2=3

Fibonacci(5)=2+3=5

Fibonacci(6)=3+5=8

Fibonacci(7)=5+8=13

Fibonacci(8)=8+13=21

Fibonacci(9)=13+21=34

Fibonacci(10)=21+34=55

Fibonacci(11)=34+55=89

Fibonacci(12)=55+89=144

-

7/30/2019 Designing Fibonacci Sequence Using Verilog.

4/8

4

4. APPLICATION OF FIBONACCI SEQUENCE

The Fibonacci numbers are an example of a complete sequence. This means that every positive

integer can be written as a sum of Fibonacci numbers, where any one number is used once at most.

Specifically, every positive integer can be written in a unique way as the sum of one or

more distinct Fibonacci numbers in such a way that the sum does not include any two consecutive

Fibonacci numbers. This is known as Zeckendorf's theorem, and a sum of Fibonacci numbers that

satisfies these conditions is called a Zeckendorf representation. The Zeckendorf representation of a

number can be used to derive its Fibonacci coding. . Fibonacci mathematics is a constantly

expanding branch of number theory, with more and more people being drawn into the complex

subtleties of Fibonacci's legacy.

Fibonacci numbers are found in branching plants as they grow. There is one stem which branches

into two. Then one of the new stems branches into two while the other one waits. This pattern of

one branching while the other waits is repeated for each of the new stems. An example would be

the sneezewort although some trees, root systems and algae exhibit this type of branching pattern.

Fibonacci numbers are used by some pseudorandom number generators.

A special value, closely related to the Fibonacci series, is called the golden section. This value is

obtained by taking the ratio of successive terms in the Fibonacci series. If a graph of these values

are plotted it is seen that they seem to be tending to a limit. This limit is actually the positive root

of a quadratic equation and is called the golden section, golden ratio or sometimes the golden

mean. The golden section is normally denoted by the Greek letter phi.

http://en.wikipedia.org/wiki/Complete_sequencehttp://en.wikipedia.org/wiki/Zeckendorf%27s_theoremhttp://en.wikipedia.org/wiki/Fibonacci_codinghttp://en.wikipedia.org/wiki/Pseudorandom_number_generatorshttp://en.wikipedia.org/wiki/Pseudorandom_number_generatorshttp://en.wikipedia.org/wiki/Fibonacci_codinghttp://en.wikipedia.org/wiki/Zeckendorf%27s_theoremhttp://en.wikipedia.org/wiki/Complete_sequence -

7/30/2019 Designing Fibonacci Sequence Using Verilog.

5/8

5

5. VERILOG CODE

5.1.VERILOG MODULE

module fibonacci(clock,reset,value);

input clock,reset;

output [31:0]value;

reg [31:0]previous,current;

reg [5:0]counter;

//Reset the circuit

always@(posedge reset)

begin

previous

-

7/30/2019 Designing Fibonacci Sequence Using Verilog.

6/8

6

5.2.TEST BENCH

module fibtb();

reg clock,reset;

wire [31:0]value;

fibonacci f1(value,clock,reset);

initial

begin

reset=1;

#10 reset=0;

end

initial

begin

clock=0;

forever #10 clock=~clock;

end

initial

begin

#500 $finish;

end

endmodule

-

7/30/2019 Designing Fibonacci Sequence Using Verilog.

7/8

7

6. SIMULATION OUTPUT

-

7/30/2019 Designing Fibonacci Sequence Using Verilog.

8/8

8

7. CONCLUSIONThis report is a conceptual review of how to generate Fibonacci sequence in Verilog HDL. This

report aims at providing laymans understanding to the function of Fibonacci sequence.

Fibonacci numbers are the the members of the Fibonacci series, which grows up accord to

Fibonacci rule. The rule states, the present number in the series is the sum of past number and

and the number before past, with the initial condition that, series starts from 0, and the second

term is 1.

8. REFERENCES[1]. Samir Palnitkar, Verilog HDL: Digital Design and Synthesis, Prentice Hall, 2nd

edition,2003.

[2]. B.Bala Tripura Sundari,Design through Verilog HDL, John Wiley & Sons Publishers, 1stedition,2004

[3].http://www.mathsisfun.com/numbers/fibonacci-sequence.html

[4].http://www.leonardo-fibonacci-numbers.com/

http://www.mathsisfun.com/numbers/fibonacci-sequence.htmlhttp://www.mathsisfun.com/numbers/fibonacci-sequence.htmlhttp://www.mathsisfun.com/numbers/fibonacci-sequence.htmlhttp://www.leonardo-fibonacci-numbers.com/http://www.leonardo-fibonacci-numbers.com/http://www.leonardo-fibonacci-numbers.com/http://www.leonardo-fibonacci-numbers.com/http://www.mathsisfun.com/numbers/fibonacci-sequence.html