Design Kit - CYBERNETv2 = 0 v3 = 5 vrefab 1.25vdc o_b o_a1 o_b1 o_a rsb 7.9ohm l2 9.15mh ic = 0 1 2...

Transcript of Design Kit - CYBERNETv2 = 0 v3 = 5 vrefab 1.25vdc o_b o_a1 o_b1 o_a rsb 7.9ohm l2 9.15mh ic = 0 1 2...

2-Phase Bipolar Stepping Motor Driver Using

TB62206FG

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 1

Design Kit

Contents

Slide #

1. Background

1.1 Bipolar Stepping Motors.......................................................................................

1.2 Torque vs. Speed.................................................................................................

1.3 Bipolar Operating Mode.......................................................................................

2. Application Circuit......................................................................................................

2.1 Specification........................................................................................................

2.2 Calculating Equations..........................................................................................

3. Stepper Motor Switching Sequences

3.1 Full Step Switching Sequence.............................................................................

3.2 Half Step Switching Sequence.............................................................................

4. Functions

4.1 STANDBY............................................................................................................

4.2 TORQUE.............................................................................................................

4.3 Phase A Over-current Protection..........................................................................

4.4 Phase B Over-current Protection.........................................................................

5. Output Ripple Current................................................................................................

5.1 Stepping Motor Phase Inductance at The Chopping Frequency..........................

5.2 Ripple Current Simulation....................................................................................

6. The Current Changing Rate.......................................................................................

6.1 Stepping Motor Phase Inductance at The Phase Frequency................................

6.2 Current Changing Rate Simulation.......................................................................

7. Optimization of The Drive Voltage VM.......................................................................

Simulations index............................................................................................................

3

4

5-6

7

8-9

10

11-12

13-14

15-16

17-18

19-20

21-22

23

24

25-26

27

28

29-30

31-32

33

2All Rights Reserved Copyright (C) Bee Technologies Corporation 2009

1.1 Bipolar Stepping Motors

• There are two winding with no center taps.

• The drive circuitry requires an H-bridge control circuit for each winding, as the drive circuit need to

change the polarity of each pair of motor poles.

• The current sequences are shown below.

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 3

• Full Step • Half Step

Io(A)100%

-100%

100%

-100%Io(B)

time

Io(A)

100%

0%

Io(B)

time

-100%

100%

0%

-100%

1.2 Torque vs. Speed

• The inductance of the motor winding determines the rise and fall time of the current through the

winding.

• The current-vs-time function through each winding depend on the drive circuitry and the motor

characteristics.

• The rise time is determined by the drive voltage, while the fall time depends on the circuitry used

to dissipate the stored energy in the motor winding (fast or slow decay).

• The effect of the inductance of the motor windings is to reduce the available torque, as shown in

the Torque-vs-Speed curve.

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 4

100%

-100%

Time

ideal

actual

Torque

Speed

Running Torque

Cutoff

Speed

Max. Speed

1.3 Bipolar Operating Mode

Charge mode Slow decay mode

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 5

Fast decay mode

OFF

ON

ON ONON ON

ONOFF

OFF

OFF OFF OFF

• These figure show how TB62206FG switches the current in each motor winding on and off, and

controlling its direction, in three different modes.

1.3 Bipolar Operating Mode

U1 U2 L1 L2

Charge ON OFF OFF ON

Slow OFF OFF ON ON

Fast OFF ON ON OFF

• In TB62206FG, three modes as shown above are automatically switched to control the

constant current

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 6

• Charge mode, the H-bridge forward state to allow current to flow from the supply

through the motor winding and onward to ground.

• Slow decay mode, in this mode, winding current is re-circulated by enabling both of

the low-side FETs in the bridge.

• Fast decay mode, the H-bridge reverses state to allow winding current to flow in a

reverse direction.

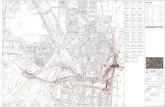

2. Application Circuit

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 7

O_A

O_A1

O_B1

O_BO_B

RRSA 0.5ohmO_B1

V5Vref AB1.25Vdc

O_A1

O_A

RSB

L2

IC = 0

1

2

0

Cv ref AB1uF

00

L1

IC = 012

RSA

RRSB 0.5ohm

0

VM124V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = 0

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

0

Cosc 560pF

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

Ph_BPh_A

Ph_B

Ph_A

2.1 Specification

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 8

Operating Conditions

Characteristics Symbol Value Unit

Power supply voltage VDD 5 V

Motor supply voltage VM 24 V

Reference voltage VREF 1.25 V

Logic input voltage VIN 5 V

Output current IOUT 0.5 A

Phase signal input frequency fPHASE 250 Hz

Chopping frequency fchop 101 kHz

Oscillation frequency fCR 813 kHz

2.1 Specification

Time

2.540ms 2.544ms 2.548ms 2.552ms 2.556ms 2.560ms 2.564ms 2.568ms 2.572ms 2.576ms 2.580ms

I(U1:OUT_A)

500mA

420mA

540mA

SEL>>

V(U1:CR)

1.0V

2.0V

3.0V

4.0V

• This figure shows the output current IOUT ,the oscillation frequency fCR ,and the

chopping frequency fchop.

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 9

IOUT = 0.5A

fchop = 101kHz

fCR = 813kHz

Charge mode

Slow decay mode

Fast decay mode

2.2 Calculating Equations

• The output current value (set current value) can be determined by setting the sensing resistor (RRS) and reference voltage (Vref).

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 10

%1005

1 %)71,100(

RS

TorqueOUT

R

TorqueVrefI

• The oscillation frequency is calculated as follows:

(1)

(2))600(523.0

1

CRCf

OSCOSC

CR

• The chopping frequency fchop is calculated as follows:

(3)

8

chopCR

ff

O_B1

O_B

O_A

O_A1

RSB 7.9ohm

L29.15mHIC = -0.5

1

2

L19.15mHIC = -0.5

12

RSA7.9ohm

O_A

O_A1

O_B1

O_B

RRSA 0.5ohm

V5Vref AB1.25Vdc

0

Cv ref AB1uF

00

RRSB 0.5ohm

0

VM124V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/2}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

Ph_BPh_A

Ph_B

Ph_A

3.1 Full Step Switching Sequence

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 11

Full-step sequences

control signals

Analysis

Time Domain (Transient)

Run to time: 8ms

Start saving data after: 0ms

Maximum step size: -

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 1p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

3.1 Full Step Switching Sequence

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 12

• This figure shows the simulation result of the circuit with Full-step switching sequence.

Phase A

Phase B

Enable A

Enable B

IOUT A

IOUT B

Time

0s 4.0ms 8.0ms

I(U1:OUT_B1)

-1.0A

0A

1.0A

I(U1:OUT_A1)

-1.0A

0A

1.0A

V(U1:ENABLE_B)

0V

SEL>>

V(U1:ENABLE_A)

0V

V(PH_B)

0V

V(PH_A)

0V

O_B1

O_B

O_A

O_A1

RSB 7.9ohm

L29.15mHIC = -0.5

1

2

L19.15mHIC = -0.5

12

RSA7.9ohm

O_A

O_A1

O_B1

O_B

RRSA 0.5ohm

V5Vref AB1.25Vdc

0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

0

V_ENABLE_A

TD = 0

TF = {tf phase}PW = {3*pwphase/4}

PER = {tphase/2}

V1 = 0

TR = {trphase}

V2 = 5V

00

V_ENABLE_B

TD = {tphase/8}

TF = {tf phase}PW = {1*pwphase/4}

PER = {tphase/2}

V1 = 5V

TR = {trphase}

V2 = 0

V_PHASE_A

TD = 0

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B1

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

EN

_B

EN

_A

EN_AEN_B

0

Cv ref AB1uF

00

RRSB 0.5ohm

0

VM124V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Half Step

Ph_BPh_A

Ph_B

Ph_A

3.2 Half Step Switching Sequence

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 13

Half-step sequences

control signals

Analysis

Time Domain (Transient)

Run to time: 8ms

Start saving data after: 0ms

Maximum step size: -

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 1p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

3.2 Half Step Switching Sequence

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 14

• This figure shows the simulation result of the circuit with Half-step switching sequence.

Phase A

Phase B

Enable A

Enable B

IOUT A

IOUT B

Time

0s 2.0ms 4.0ms 6.0ms 8.0ms

I(U1:OUT_B1)

-1.0A

0A

1.0A

I(U1:OUT_A1)

-1.0A

0A

1.0A

V(U1:ENABLE_B)

0V

SEL>>

V(U1:ENABLE_A)

0V

V(U1:PHASE_B)

0V

V(U1:PHASE_A)

0V

O_A

O_A1

O_B1

O_B

RRSA 0.5ohm

V5T1 = 0T2 = 2000uT3 = 2000.1u

V1 = 0V2 = 0V3 = 5

Vref AB1.25Vdc

O_B

O_A1

O_B1

O_A

RSB 7.9ohm

L29.15mHIC = 0

1

2

L19.15mHIC = 0

12

RSA7.9ohm

0

Cv ref AB1uF

00

RRSB 0.5ohm

0

VM124V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = 0

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

Ph_BPh_A

Ph_B

Ph_A

0

VenT1 = 0

T2 = 0.1uV1 = 0

V2 = 5

4.1 STANDBY

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 15

STANBY turn on

(LH) at 2ms

Analysis

Time Domain (Transient)

Run to time: 8ms

Start saving data after: 0ms

Maximum step size: -

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 10p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

4.1 STANDBY

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 16

• This figure shows the simulation result of the circuit when V(STANDBY) changes from

LH.

Phase A

Phase B

Enable A

STANDBY

IOUT A

IOUT B

Enable B

Ccp1

Time

0s 4.0ms 8.0ms

I(U1:OUT_B1)

-1.0A

1.0ASEL>>

I(U1:OUT_A1)

0A

V(U1:ENABLE_B)

0V

V(U1:ENABLE_A)

0V

V(PH_B)

0V

V(PH_A)

0V

V(U1:CCP_A)

20V

30V

V(U1:STANDBY)

0V0 5V

Charge Pump Start

STANDBY TURN-ON

O_A

O_A1

VTRQT1 = 0T2 = 4000uT3 = 4000.1u

V1 = 5V2 = 5V3 = 0

O_B1

O_B

VenT1 = 0

T2 = 0.1uV1 = 0

V2 = 5

RRSA 0.5ohm

Vref AB1.25Vdc

O_B

O_A1

O_B1

O_A

RSB 7.9ohm

L29.15mHIC = -0.5

1

2

L19.15mHIC = -0.5

12

RSA7.9ohm

0

Cv ref AB1uF

00

RRSB 0.5ohm

0

VM124V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = 0

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

Ph_BPh_A

Ph_B

Ph_A

0

4.2 TORQUE

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 17

TORQUE (HL) at

4ms

Analysis

Time Domain (Transient)

Run to time: 8ms

Start saving data after: 0ms

Maximum step size: -

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 1p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

Time

0s 4.0ms 8.0ms

I(U1:OUT_B1)

-500mA

500mA

SEL>>

I(U1:OUT_A1)

0A

V(U1:ENABLE_B)

0V

V(U1:ENABLE_A)

0V

V(PH_B)

0V

V(PH_A)

0V

V(U1:TORQUE)

0V

4.2 TORQUE

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 18

• This figure shows the simulation result of the circuit when V(TORQUE) changes from HL

,then the output current changes from 100% to 71%.

Phase A

Phase B

Enable A

TORQUE

IOUT A

IOUT B

Enable B

5 0V

IOUT =100% 70%

100% 71%

100% 71%

O_A

O_A1

O_B1

O_B

V5

T1 = 0T2 = 1200uT3 = 1200.1u

V1 = 0V2 = 0V3 = 5

VenT1 = 0

T2 = 0.1uV1 = 0

V2 = 5

+

-

+

-

S1S

VON = 1.0VVOFF = 0.0V

ROFF = 1.2RON = 0.15

Vref AB3Vdc

O_B1

O_B

O_A

O_A1

RSB 3.5ohm

L29.15mHIC = -0.5

1

2

L19.15mHIC = -0.5

12

RSA3.5ohm

0

0

Cv ref AB1uF

00

RRSB 1.2ohm

0

VM124V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/2}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

Ph_BPh_A

Ph_B

Ph_A

4.3 Phase A Over-current Protection

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 19

RRSA (1.2 0.15),

IOUT(0.54A) at 1ms

Analysis

Time Domain (Transient)

Run to time: 4.5ms

Start saving data after: 0ms

Maximum step size: -

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 1p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

RS is a small value to test

over current condition.

Time

0s 2.0ms 4.0ms 4.5ms

I(U1:OUT_B1)

-0.75A

0.75A

SEL>>

I(U1:OUT_A1)

0A

2.0A

V(PH_B)

0V

7.5V

V(PH_A)

0V

7.5V

V(U1:STANDBY)

0V

7.5V

4.3 Phase A Over-current Protection

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 20

• This figure shows the simulation result of the circuit when Phase A output current exceeds

the ISD(3A), then OCP shutdowns the output.

Phase A

Phase B

STANDBY

IOUT A

IOUT B

Io > ISD (3A)

OUTPUT TURNED OFF

OUTPUT SHUT DOWN

O_A

O_A1

O_B1

O_B

V5

T1 = 0T2 = 2000uT3 = 2000.1u

V1 = 0V2 = 0V3 = 5

VenT1 = 0

T2 = 0.1uV1 = 0

V2 = 5

+

-

+

-

S1S

VON = 1.0VVOFF = 0.0V

ROFF = 1.2RON = 0.15

Vref AB3Vdc

0

0

Cv ref AB1uF

00

0

VM124V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/2}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

RRSA 1.2ohm

Ph_BPh_A

Ph_B

Ph_A

O_B

O_A1

O_B1

O_A

RSB 3.5ohm

L29.15mHIC = -0.5

1

2

L19.15mHIC = -0.5

12

RSA3.5ohm

4.4 Phase B Over-current Protection

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 21

RRSB (1.2 0.15),

IOUT(0.54A) at 1ms

Analysis

Time Domain (Transient)

Run to time: 6ms

Start saving data after: 0ms

Maximum step size: -

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 1p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

RS is a small value to test

over current condition.

Time

0s 2.0ms 4.0ms 6.0ms

I(U1:OUT_B1)

2.0A

SEL>>

I(U1:OUT_A1)

0A

V(PH_B)

0V

7.5V

V(PH_A)

0V

7.5V

V(U1:STANDBY)

0V

7.5V

4.4 Phase B Over-current Protection

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 22

• This figure shows the simulation result of the circuit when Phase B output current exceeds

the ISD(3A), then OCP shutdowns the output.

Phase A

Phase B

STANDBY

IOUT A

IOUT B

Io > ISD (3A)

OUTPUT SHUT DOWN

OUTPUT SHUT DOWN

Time

2.54ms 2.58ms

I(U1:OUT_B1)

400mA

600mA

I(U1:OUT_A1)

400mA

600mA

SEL>>

5 Output Ripple Current

• This figure shows the output ripple current of the Mixed Decay Mode ,which consist of

Charge ,Slow decay ,and Fast decay mode ,with 101kHz chopping frequency.

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 23

IOUT = 0.5A

fchop = 101kHz

IOUT A

IOUT BCharge mode

Slow decay mode Fast decay mode

5.1 Stepping Motor Phase Inductance at The Chopping Frequency

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 24

• Ls(H) vs. Frequency(Hz) is shown in figure above. Ls value at the chopping frequency

(approximately 100kHz) will be used as stepping motor phase inductance.

Stepping Motor Phase Inductance

0

0.002

0.004

0.006

0.008

0.01

0.012

1.E+02 1.E+03 1.E+04 1.E+05

Frequency (Hz)

Ls(H

)

Ls

Ls = 1.7mH @

fchop=100kHz

O_A

O_A1

O_B1

O_B

RRSA 1.2ohm

V5Vref AB3Vdc

0

Cv ref AB1uF

00

RRSB 1.2ohm

0

VM124V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/2}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

Ph_BPh_A

Ph_B

Ph_A

O_B1

O_B

O_A

O_A1

RSB 7.9ohm

L21.7mHIC = -0.5

1

2

L11.7mHIC = -0.5

12

RSA7.9ohm

5.2 Ripple Current Simulation

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 25

Ls = 1.7mH is input as

the stepping motor

phase inductance value

Analysis

Time Domain (Transient)

Run to time: 4ms

Start saving data after: 0ms

Maximum step size: -

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 1p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

Time

2.593ms 2.595ms 2.597ms 2.599ms 2.601ms 2.603ms

I(U1:OUT_A1)

300mA

400mA

500mA

600mA

700mA

SEL>>

5.2 Ripple Current Simulation

• The simulation result shows the current ripple that agrees to the measurement data.

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 26

Current ripple

Current ripple

Simulation

Measurement

Time

0s 4.0ms

I(U1:OUT_A1)

0A

-800mA

800mA

6. The Current Changing Rate

• This figure shows the current changing rate (rise and fall time) that is determined by

the phase inductance value.

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 27

Fall timeRise time

100%

-100%

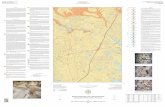

6.1 Stepping Motor Phase Inductance at The Phase Frequency

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 28

• Ls(H) vs. Frequency(Hz) is shown in figure above. Ls value at the phase frequency (250

Hz) will be used as stepping motor phase inductance.

Stepping Motor Phase Inductance

0

0.002

0.004

0.006

0.008

0.01

0.012

1.E+02 1.E+03 1.E+04 1.E+05

Frequency (Hz)

Ls(H

)

Ls

Ls = 9.15mH @

fphase=250Hz

O_A

O_A1

O_B1

O_B

RRSA 0.5ohm

V5Vref AB1.25Vdc

0

Cv ref AB1uF

00

RRSB 0.5ohm

0

VM24V CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = 0

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

O_B

O_A1

O_B1

O_A

RSB 7.9ohm

L29.15mHIC = -0.5

1

2

L19.15mHIC = -0.5

12

RSA7.9ohm

Ph_BPh_A

Ph_B

Ph_A

6.2 Current Changing Rate Simulation

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 29

Ls = 9.15mH is input as

the stepping motor

phase inductance value.

Analysis

Time Domain (Transient)

Run to time: 4ms

Start saving data after: 0ms

Maximum step size: -

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 1p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

6.2 Current Changing Rate Simulation

• The simulation result shows the current changing rate (rise and fall time) that agrees to the

measurement data.

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 30

Current ripple

Current ripple

VM=24VVM=24V

Time

0s 1.0ms 2.0ms 3.0ms 4.0ms

I(U1:OUT_A1)

0A

-0.75A

0.75A

V(PH_B)

0V

7.5V

SEL>>

V(PH_A)

0V

7.5V

O_A

O_A1

O_B1

O_B

O_B

RRSA 0.5ohm

O_B1

V5Vref AB1.25Vdc

O_A1

O_A

RSB 7.9ohm

L29.15mHIC = -0.5

1

2

0

Cv ref AB1uF

00

L19.15mHIC = -0.5

12

RSA7.9ohmRRSB 0.5ohm

0

VM24 CVM1

100uF

00

U1

TB62206FG

CCP1 = 0.22UFCCP2 = 0.01UF

VM = 24COSC = 560PFROSC = 3.6K

FIN

CRVDDVREF_AVREF_BRS_B

RS_AVMCCP_CCCP_BCCP_A STANDBY

OUT_A1PHASE_APHASE_B

OUT_A

OUT_BENABLE_AENABLE_B

OUT_B1TORQUE

V_PHASE_A

TD = 0

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0

TR = {trphase}

V2 = 5V

V_PHASE_B

TD = {tphase/4}

TF = {tf phase}PW = {pwphase}PER = {tphase}

V1 = 0V

TR = {trphase}

V2 = 5

0 0

PARAMETERS:

f phase = 250Hz

tphase = {1/f phase}

tdphase = {trphase+pwphase/2}

pwphase = {-2*trphase+tphase/2}

trphase = 100n

tf phase = {trphase}

VDD5Vdc C1

10uF

0 0

Rosc 3.6kohm

Cosc 560pF

0

0

Cccp_10.22uF

Cccp_20.022uF

250Hz Full Step

Ph_BPh_A

Ph_B

Ph_A

7. Optimization of The Drive Voltage VM

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 31

The Drive Voltage

Source: VM

Analysis

Time Domain (Transient)

Run to time: 4.5ms

Start saving data after: 0ms

Maximum step size: 1u

(SKIPBP)

Parametric Sweep

Voltage source

Name: VM

Value list: 12, 18, 24

.Options

RELTOL: 0.01

VNTOL: 1.0m

ABSTOL: 1.0n

CHGTOL: 10p

GMIN: 1.0E-12

ITL1: 500

ITL2: 200

ITL4: 100

Time

0s 4.0ms

I(U1:OUT_A1)

0A

SEL>>

V(PH_B)

0V

7.5V

V(PH_A)

0V

7.5V

7. Optimization of The Drive Voltage VM

• These figures show that the current changing rates (rise and fall time) depend on the drive voltage

(VM). The higher current changing rate means higher phase frequency is available.

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 32

Current ripple

Current ripple

VM=18V

VM=24V

VM=12VVM=24V

VM=18V

VM=12V

Simulations index

Simulations Folder name

1. Full Step Switching Sequence.......................................................

2. Half Step Switching Sequence.......................................................

3. STANDBY.......................................................................................

4. TORQUE........................................................................................

5. Phase A Over-current Protection....................................................

6. Phase B Over-current Protection...................................................

7. Ripple Current Simulation..............................................................

8. Current Changing Rate Simulation.................................................

9. Optimization of The Drive Voltage VM..........................................

Full-Step

Half-Step

STANDBY

TORQUE

OCP_A

OCP_B

RIPPLE

I_Step

VM

All Rights Reserved Copyright (C) Bee Technologies Corporation 2009 33

![[XLS]data. · Web view0. 0. 2. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0. 0.](https://static.fdocuments.net/doc/165x107/5ab13df97f8b9ac66c8c4034/xlsdata-view0-0-2-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0.jpg)

![[XLS] · Web view0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 7 2 0 0 0 0 0 0 0 0 0 0 0 5 4 0 0 0 0 0 0 0 0 0 0 0 5 4 0 0 0 0 0 0 0 0 0 0 0 5 4 0 0 0 0 0 0 0 0 0 0 0 5 4 0 0 0 0](https://static.fdocuments.net/doc/165x107/5aad015d7f8b9a8d678d9907/xls-view0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-7-2-0-0-0-0-0-0-0-0-0.jpg)

![Clinical data successes - Joseph Paul Cohen...cat = [0 0 1 0 0 0 0 0 0 0 0 0 0 0 … 0] dog = [0 0 0 0 1 0 0 0 0 0 0 0 0 0 … 0] house = [1 0 0 0 0 0 0 0 0 0 0 0 0 0 … 0] Note!](https://static.fdocuments.net/doc/165x107/5fdf222a2dd17b0d95129a68/clinical-data-successes-joseph-paul-cohen-cat-0-0-1-0-0-0-0-0-0-0-0-0-0.jpg)

![[XLS] · Web view517 0 0 1 2 3 41 20 0 0 0 0 0 0 0 41 20 0 0 0 0 0 0 0 0 0 41 20 0 0 0 0 0 0 0 0 0 41 20 0 0 0 0 0 0 41 20 0 0 0 0 0 0 0 0 41 20 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0](https://static.fdocuments.net/doc/165x107/5ac92e3b7f8b9acb7c8d5fad/xls-view517-0-0-1-2-3-41-20-0-0-0-0-0-0-0-41-20-0-0-0-0-0-0-0-0-0-41-20-0-0-0.jpg)