Department of Electronics & Communication Engineering ... · PRACTICAL INSTRUCTION SHEET ......

Transcript of Department of Electronics & Communication Engineering ... · PRACTICAL INSTRUCTION SHEET ......

AIM: Design, simulation and analysis of two input NAND and NOR gate.

Theory: NAND stands for NOT AND. An AND gate followed by a NOT circuit makes it

a NAND gate. The truth table of a NAND gate is obtained from the truth table of an AND

gate by complementing the output entries. The output of a NAND gate is logic‘0’when all

its inputs are a logic‘1’.For all other input combinations.

NOR stands for NOT OR. An OR gate followed by a NOT circuit makes it a NOR gate. The

truth table of a NOR gate is obtained from the truth table of an OR gate by complementing

the output entries. The output of a NOR gate is a logic‘1’when all its inputs are logic‘0’.For

all other input combinations, the output is a logic‘0’

Dev Bhoomi Institute Of Technology Department of Electronics & Communication

Engineering

LABORATORY MANUAL

PRACTICAL INSTRUCTION SHEET

EXPERIMENT NO. 1 ISSUE NO. : ISSUE DATE:

July 2012

REV. NO. : REV. DATE :

PAGE: 3

LABORATORY Name & Code: PCS-854 CAD LAB SEMESTER: VIII

U1A

1 2 7400N

V1

1kHz

5 V

V2

1kHz

5 V

0 0

3

XSC1

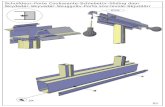

Figure: 2 Input NAND Gate

G

T

4

3 2

1

P T

ektr

on

ix

U1A

1 2 7402N

V1

1kHz

5 V

V2

1kHz

5 V

0 0

3

XSC1

Figure: 2 Input NOR Gate

G

T

4

3 2

1

P T

ektr

on

ix

AIM: Design, simulation and analysis of Push Pull Amplifier

Theory: The push-pull amplifier is a power amplifier and is frequently employed in the

output stages of electronic circuits. It is used whenever high output power at high efficiency

is required. Fig. shows the circuit of a push-pull amplifier. Two transistors Tr1 and Tr2

placed back to back are employed. Both transistors are operated in class B operation i.e.

collector current is nearly zero in the absence of the signal. The centre-tapped secondary of

driver transformer T1 supplies equal and opposite voltages to the base circuits of two

transistors. The output transformer T2 has the centre- tapped primary winding. The supply

voltage VCC is connected between the bases and this centre tap. The loud-speaker is

connected across the secondary of this transformer. The input signal appears across the

secondary AB of driver transformer. Suppose during the first half-cycle (marked 1) of the

signal, end A becomes positive and end B negativities. This will make the base-emitter

junction of Tr1 reverse biased and that of Tr2 forward biased. The circuit will conduct

current due to Tr2 only and is shown by solid arrows. Therefore, this half-cycle of the signal

is amplified by Tr2 and appears in the lower half of the primary of output transformer. In

the next half- cycle of the signal, Tr1 is forward biased whereas Tr2 is reversing biased.

Therefore, Tr1 conducts and is shown by dotted arrows. Consequently, this half-cycle of the

signal is amplified by Tr1 and appears in the upper half of the output transformer primary.

The centre-tapped primary of the output transformer combines two collector currents to

form a sine wave output in the secondary.

Dev Bhoomi Institute Of Technology Department of Electronics and Communication

Engineering

LABORATORY MANUAL

PRACTICAL INSTRUCTION SHEET

EXPERIMENT NO. 2 ISSUE NO. : ISSUE DATE:

July 2012

REV. NO. : REV. DATE :

PAGE: 4

LABORATORY Name & Code: PCS-854 CAD LAB SEMESTER: VIII

XSC2 4

R1 5kΩ

Ext T rig +

_

V2

20 V A B

C1 Q1

2N3904

+ _ + _

3

10uF

IC=0V

D1

1N4001GP

Input 2 1

C3 8 10

V1

D2

1N4001GP 100uF

IC=0V

1 Vpk

1kHz

0°

C2 7 Q2

2N3906

10uF

IC=0V

R3 100Ω

R2 5kΩ

0

0

Figure: Push Pull Amplifier

AIM: Design, simulation and analysis of NMOS and CMOS inverter.

Theory: CMOS inverters are commonly used to build square-wave oscillators for

generating clock signals. These clock generators offer good stability, operation over a wide

supply voltage range (3– 15V) and frequency range (1 Hz to in excess of 15MHz), low

power consumption and an easy inter face to other logic families. The most fundamental

circuits the ring configuration of any odd number of inverters. Inverting gates such as

NAND and NOR gates can also be used instead. This configuration does not make a

practical oscillator circuit a sits frequency of Oscillation is highly susceptible to variation

with temperature, supply voltage and external loading.

Dev Bhoomi Institute Of Technology Department of Electronics and Communication

Engineering

LABORATORY MANUAL

PRACTICAL INSTRUCTION SHEET

EXPERIMENT NO. 3 ISSUE NO. : ISSUE DATE:

July 2012

REV. NO. : REV. DATE :

PAGE: 3

LABORATORY Name & Code: PCS-854 CAD LAB SEMESTER: VIII

VDD

5V

XSC1

Ext T rig

VDD

Q1

2N6804

2 1

V1

1kHz

+

_

A B

+ _ + _

5 V Q2 0

2VNS6S659

VSS

0V

Figure: CMOS Inverter

XSC1

Figure: Resistive Load NMOS Inverter

VDD

5V Ext T rig

+

_

VDD A B

+ + _ _

R1 1kΩ

1

Q2

2

V1

1kHz

5 V

2VNS6S659

VSS

0V

0

AIM: Design, simulation and analysis of Full Adder.

Theory:

Dev Bhoomi Institute Of Technology Department of Electronics and Communication

Engineering

LABORATORY MANUAL

PRACTICAL INSTRUCTION SHEET

EXPERIMENT NO. 4 ISSUE NO. : ISSUE DATE:

July 2012

REV. NO. : REV. DATE :

PAGE: 2

LABORATORY Name & Code: PCS-854 CAD LAB SEMESTER: VIII

Figure: Full Adder

XSC2 XSC3

Ext T rig +

_

A B

Ext T rig +

_ XSC1

+ _ + _ A B

+ _ + _ Ext T rig

+

_

A B

U2 + + _ _

A B

SUM CARRY

4 5

3 CIN

2 1 FULL_ADDER

V1

1kHz

5 V

V2

1kHz

5 V

V3

1kHz

5 V

0

AIM: Design, simulation and analysis of Up/ Dow Counter.

Theory: The down-counter is implemented by connecting the Q0 and Q1 outputs.

The up-counter and down-counter can be implemented as a single counter circuit by

adding some extra logic. In the circuit diagram, the Up-down counter is configured to count

up or down by setting the DOWN / UP input to logic 1 or 0 respectively. When the DOWN /

UP input is set to logic 1, upper AND gates are enabled, allowing flip-flip 2 to toggle its

state when F0 output of flip- flop 1 is logic 1. Similarly when both F0 and F1 outputs are

logic 1, flip-flop 3 toggles its state. When the DOWN / UP input is set to logic 0, the lower

AND gates are enabled. When F0 is logic 0, Q0 is logic 1 and the flip-flop 2 toggles its

output state. Similarly, when both outputs F0 and F1 are at logic 0, that is, Q0 and Q1 are at

logic 1 the flip-flop 3 toggles its state. During the counting sequence, the DOWN / UP input

can be set to logic 1 or 0 at any time to reverse the counting sequence.

Dev Bhoomi Institute Of Technology Department of Electronics and Communication

Engineering

LABORATORY MANUAL

PRACTICAL INSTRUCTION SHEET

EXPERIMENT NO. 5 ISSUE NO. : ISSUE DATE:

July 2012

REV. NO. : REV. DATE :

PAGE: 2

LABORATORY Name & Code: PCS-854 CAD LAB SEMESTER: VIII

Pag

e12

V2 5 V

5

0 U1 U2 U3 U4

SET

4 J

CLK

K

Q 1

SET

2 SET

3 SET

~Q

J Q

CLK

K ~Q

J Q

CLK

K ~Q

J Q

CLK

K ~Q

1kHz

5 V RESET RESET RESET RESET

0 JK_FF JK_FF JK_FF JK_FF

6

G

P 1 2 3 4 T

XSC2 Tektronix

AIM: Design simulation and analysis of Multiplexer.

Theory:

Dev Bhoomi Institute Of Technology Department of Electronics and Communication

Engineering

LABORATORY MANUAL

PRACTICAL INSTRUCTION SHEET

EXPERIMENT NO. 6 ISSUE NO. : ISSUE DATE:

July 2012

REV. NO. : REV. DATE :

PAGE: 3

LABORATORY Name & Code: PCS-854 CAD LAB SEMESTER: VIII

Pag

e12

1 2

5 V V4 V3 3

4

5 V V5 0 V V6 6

0 V 5

V1

1kHz

5 V

V2

1kHz

5 V

D0

D1

D2

D3

A

B

~G

Y

~W

MUX_4TO1

0

Ext T rig

+

_

A B

+ + _ _

7

XSC1

U1