CSCI 150 Introduction to Digital and Computer System Design … · 2020. 11. 24. · Vector3. NOT...

Transcript of CSCI 150 Introduction to Digital and Computer System Design … · 2020. 11. 24. · Vector3. NOT...

-

23.11.20 16:59CSCI 150 Introduction to Digital and Computer

System Design Lecture 5: Registers II

Jetic Gū

2020 Summer Semester (S2)

-

Overview

• Focus: Fundamentals of Complex Digital Circuit Design

• Architecture: von Neumann

• Textbook v4: Ch7 7.6; v5: Ch6 6.6

• Core Ideas:

1. Implementation of Register Microoperations

-

Register Transfer Operations

Revie

w

P0 Review

Operator Example

Assignment

-

Implementation of Datapath I

Summ

ary

P1 Datapath

Architecture

-

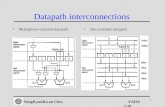

Datapath

Datapath and Control Unit1. ALU connected to Reg for 1st input

2. ALU connected to Reg for 2nd input

3. ALU connected to Reg to store result

4. CU tells ALU which register to take as 1st input

5. CU tells ALU which register to take as 2st input

6. CU tells ALU which operation to do

7. CU tells which Reg to store result in Using decoder and EN on each Register

Revie

w

P1 Datapath

Adder-Subtractor

(ALU)

Control Unit (CU)

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

45

6

3

Red: AddressGreen: Mode

7Dec

-

Single Register Microoperations

• In reality, a single circuit is designed to do multiple stuff

• a CPU can perform thousands/millions of different types of instructions

• How to design it?

• Let’s start with single register Microoperations

• Input: one of the registers; Output: another one of the registers;

Conc

ept

P1 Datapath

-

Single Register Microoperations

Conc

ept

P1 Datapath

Operator Example

Assignment

-

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

Select Registers for Input• Suppose we have 4 registers, we want to select one to provide input to a

functional block

Conc

ept

P1 Datapath

Control Unit (CU)

Functional Block 1

Functional Block N

…

CLK

-

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

Select Registers for Input• Suppose we have 4 registers, we want to select one to provide input to a

functional block

Conc

ept

P1 Datapath

Control Unit (CU)

Functional Block 1

Functional Block N

…

• Suppose registers, each 8-bit

2n

CLK

-

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

Select Registers for Input• Suppose we have 4 registers, we want to select one to provide input to a

functional block

Conc

ept

P1 Datapath

Control Unit (CU)

Functional Block 1

Functional Block N

…

• Suppose registers, each 8-bit

2n

• What kind of multiplexer should be used?

CLK

-

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

Select Registers for Input• Suppose we have 4 registers, we want to select one to provide input to a

functional block

Conc

ept

P1 Datapath

Control Unit (CU)

Functional Block 1

Functional Block N

…

• Suppose registers, each 8-bit

2n

• What kind of multiplexer should be used?

• How many bits on the red wire?

CLK

-

Select Registers to Output• Suppose we have 4 registers, we want to select one to store our output

Conc

ept

P1 Datapath

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

8-bit Data

EN

EN

EN

EN

Control Unit (CU)

CLK

-

Select Registers to Output• Suppose we have 4 registers, we want to select one to store our output

Conc

ept

P1 Datapath

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

8-bit Data

EN

EN

EN

EN

Control Unit (CU)

CLK

-

Select Registers to Output• Suppose we have 4 registers, we want to select one to store our output

Conc

ept

P1 Datapath

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

8-bit Data

EN

EN

EN

EN

Control Unit (CU)

Dec

CLK

-

Select Registers to Output• Suppose we have 4 registers, we want to select one to store our output

Conc

ept

P1 Datapath

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

• Suppose registers, each 8-bit

2n

8-bit Data

EN

EN

EN

EN

Control Unit (CU)

Dec

CLK

-

Select Registers to Output• Suppose we have 4 registers, we want to select one to store our output

Conc

ept

P1 Datapath

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

• Suppose registers, each 8-bit

2n

• What kind of decoder should be used?

8-bit Data

EN

EN

EN

EN

Control Unit (CU)

Dec

CLK

-

Select Registers to Output• Suppose we have 4 registers, we want to select one to store our output

Conc

ept

P1 Datapath

REG 0Q

D

REG 1Q

D

REG 2Q

D

REG 3Q

D

• Suppose registers, each 8-bit

2n

• What kind of decoder should be used?

• How many bits on the red wire?

8-bit Data

EN

EN

EN

EN

Control Unit (CU)

Dec

CLK

-

Single Register Microoperations

• Assignment e.g. ax

-

Single Register Microoperations

0. Assignment e.g. ax

-

Functional Block N5. Rotate L/R

Single Register Microoperations

0. Assignment e.g. ax

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)

Functional Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)• Select Input REG to be fed

into Processing BlocksFunctional

Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)• Select Input REG to be fed

into Processing BlocksFunctional

Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)• Select Input REG to be fed

into Processing Blocks

• Select mode for Processing Blocks

Functional Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)• Select Input REG to be fed

into Processing Blocks

• Select mode for Processing Blocks

Functional Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)• Select Input REG to be fed

into Processing Blocks

• Select mode for Processing Blocks

• Select Processing Block for output to REG

Functional Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)• Select Input REG to be fed

into Processing Blocks

• Select mode for Processing Blocks

• Select Processing Block for output to REG

Functional Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)• Select Input REG to be fed

into Processing Blocks

• Select mode for Processing Blocks

• Select Processing Block for output to REG

• Select Receiving REG

Functional Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Single Register Microoperations

Conc

ept

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Red: AddressGreen: Mode

Control Unit (CU)• Select Input REG to be fed

into Processing Blocks

• Select mode for Processing Blocks

• Select Processing Block for output to REG

• Select Receiving REG

Dec

Functional Block 1

0. Assign.

…

1. Transfer2. Shift L/R3. NOT4. Vector5. Rotate L/RFunctional Block N

-

Multiple Register Microoperations

Conc

ept

P1 Datapath

Operator Example

Assignment

-

Datapath

Multiple Register Microoperations

Conc

ept

P1 Datapath

Adder-Subtractor

(ALU)

Control Unit (CU)

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

45

6

3

Red: AddressGreen: Mode

7Dec

• Extension: how to incorporate more multiple register functional blocks?

• Extension: how to incorporate more single register functional blocks?

-

Example Datapath Question 1

• The control unit selects between 4 operations A, B, C, D.

• A, B, C, D each takes 1/1/2/2 register(s) as input and outputs to 1 register

• A, B, C, D doesn’t have additional mode selections

• Specify the control unit interface to the datapath

• Draw the circuit diagram of such datapath with a register array

Exerc

ise

P1 Datapath

-

Example Datapath Question 1

Exerc

ise

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Dec

Functional Block 1

…

Functional Block N

Control Unit (CU)

-

Example Datapath Question 1

Exerc

ise

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Dec

Functional Block 1

…

Functional Block N

Control Unit (CU)

-

Example Datapath Question 1

Exerc

ise

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Dec

Control Unit (CU)

-

Example Datapath Question 1

Exerc

ise

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Dec

Functional Block A

Functional Block B

Functional Block C

Functional Block D

Control Unit (CU)

-

Example Datapath Question 1

Exerc

ise

P1 Datapath

Register Array (Reg)

REG AXQ

DREG BX

QD

REG CXQ

DREG DX

QD

……

Dec

Functional Block A

Functional Block B

Functional Block C

Functional Block D

Control Unit (CU)

![Geometric Transformations. Class 3 차원 Vector 와 4x4 Matrix Class 를 만들어 본다 class Vector3 { public: float p[3]; }; class Vector3 { public: float p[3]; };](https://static.fdocuments.net/doc/165x107/56649efc5503460f94c101ab/geometric-transformations-class-3-vector-4x4-matrix-class-.jpg)