Conception de circuits analogiques et numériques avec des ...

Cours Conception circuits numériques - unilim.fr · •Avec des circuits à architecture...

Transcript of Cours Conception circuits numériques - unilim.fr · •Avec des circuits à architecture...

Formation VHDL Vahid MEGHDADI

Vahid Meghdadihttp://www.unilim.fr/pages_perso/vahid/

Cours Conception circuits numériques– 6x1h30 de cours + 1h30 exam

– 17 HTP (5x3h + 2h !)

Notation

– Exam théorique

– Evaluation TP

– Exam pratique

1

Formation VHDL Vahid MEGHDADI

2

Introduction aux

conceptions

numériques

Une partie de ce cours a été emprunté de DSPedia développé par Dr. Bob Stewart à steepest ascent, Glasgow.

Formation VHDL Vahid MEGHDADI

3

Chapitre : Introduction

Introduction

Implantation des circuits numériques

•Avec des éléments discrets

•Avec des microprocesseurs, micro contrôleurs, DSP

•Avec des circuits à architecture programmable PAL, GAL, FPGA

•Avec des circuits intégrés ASIC

PLD : Programmable Logic Device, CPLD : Complex PLD, PAL: Programmable Array Logic, GAL: Generic Array Logic, FPGA : Field Programmable Gate Array, ASIC : application-specific integrated circuit

Formation VHDL Vahid MEGHDADI

4

•Circuit figé

•Circuit imprimé difficile à modifier

•Intégration limitée

•Coût élevé

•Justifié pour de petits circuits

Circuit avec des éléments discrets

Introduction

Formation VHDL Vahid MEGHDADI

5

Circuit à fonctionnement programmable

Microprocesseur

Mémoire

Périphérique

•A base des microprocesseurs, Microcontrôleurs, DSP

•En modifiant le programme on modifie la fonction

•Plus souple que les circuits à éléments discrets

•Vitesse limitée (mais qui augmente sans cesse)

•Parallélisme compliqué (mais faisable)

•Intégration encore limitée

•Adapté à des opérations séquentielles

Introduction

Formation VHDL Vahid MEGHDADI

6

Circuit à architecture programmable

Introduction

•Une quantité importante de portes logiques

•Des matrices d'interconnections programmables

•Modification du fonctionnement sur le circuit (ISP: In-System Programming)

•Souplesse assurée

•Coût de fabrication faible (pour un nombre limité)

•Intégration forte

•Adapté à des applications gourmandes en logique

•Temps de développement dépend de l'application

• Compliqué pour implanter des algorithmes complexes

Formation VHDL Vahid MEGHDADI

7

Les ASIC

Application Specific Integrated Circuit

• Coût très bas uniquement pour de gros

tirages

• Temps de développement important

• Pas de modifications une fois fabriqué

• Nécessitant un fondeur pour la fabrication

Introduction

Formation VHDL Vahid MEGHDADI

8

Low development cost

Short time to market

Reconfigurability

High performance

ASICs FPGAs

Low power

Low cost inhigh volumes

ASIC ou FPGA ?

Introduction

Formation VHDL Vahid MEGHDADI

9

Conception physique (layout)

Conception structurelle TTL

Conception logique

Introduction

Evolution : Méthodes de CAO

Conception fonctionnelle RTLProgrammation Verilog/VHDL

Synthèse comportemental

Formation VHDL Vahid MEGHDADI

11

Exemple

VGA

Une carte polyvalente et reconfigurable

Introduction

Connecteur

d’extension

Formation VHDL Vahid MEGHDADI

12

Logique (FPGA) ou software (µP et DSP) ?

• Vitesse• Possibilité de parallélisme (calcul dans l’espace ou dans le temps)

• Exemple y=Ax²+Bx+C

Introduction

DSP FPGA

Formation VHDL Vahid MEGHDADI

13

Intérêt de la logique par rapport à µP

• Jeu d’instruction peut ne pas contenir l’opération voulue

• Processeur peut contenir des circuits qui ne servent à rien dans notre application (Par exemple URAT)

• Processeur a besoin de la mémoire pour garder le programme et les valeurs intermédiaires

• Le nombre de bits pour présenter les données peut être trop ou peu

• Parallélisme très limité par software

Introduction

Formation VHDL Vahid MEGHDADI

14

Architecture des FPGA

Feild Programmable Gate Array

CLB CLB CLB CLBCLB CLB CLB

CLB CLB CLB CLBCLB CLB CLB

CLB CLB CLB CLBCLB CLB CLB

CLB CLB CLB CLBCLB CLB CLB

CLB CLB CLB CLBCLB CLB CLB

CLB CLB CLB CLBCLB CLB CLB

CLB CLB CLB CLBCLB CLB CLB

CLB= Configurable Logic

Block

Introduction

Formation VHDL Vahid MEGHDADI

15

FPGA architecture interne

Programmable

IO

BLE# 1

BLE# N

NOutputs

I

Inputs

Clock

I

N

Programmable

Logic (CLB)

KLUTInputs D FF

Clock

Out

Programmable

Routing

Introduction

BLE= Basic Logic Element

Formation VHDL Vahid MEGHDADI

16

Look-Up Table (LUT)

State

OutInputs

Clock

Enable

Architecture simplifiée de CLB

Out = f (in0, in1, in2, in3)

Introduction

Formation VHDL Vahid MEGHDADI

17

FPGA Xilinx

Xilinx a été fondée en 1984 pour fabriquer des circuits à logique programmable.

Plusieurs familles de FPGA

•Série 4000 (les années 90)

•Spartan (1998)

•Spartan (II, III, VI) (depuis 2000) (Spartan 6 depuis 2009)(spartan7 2017)

•Virtex (II, IV, V, VI, VII) (depuis 2001)

•Artix (2010)

•Kintex (2010)

•Zynq (SoC) (2011)

Introduction

Formation VHDL Vahid MEGHDADI

18

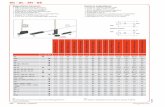

Spartan (depuis 1998)

Le nombre de broches I/O, le nombre de CLB différentie les FPGA de la famille.

Introduction

Remarque

Formation VHDL Vahid MEGHDADI

22

La famille Virtex

•Les LUT transformables en registre à décalage

•Plus de CLB, plus de mémoire, plus de slices par CLB

•Plus de I/O

•Multiplieurs câblés à partir de Virtex II

•DSP slices

•Microprocesseur embarqué (PowerPC)

Introduction

Remarque

Formation VHDL Vahid MEGHDADI

25

Virtex 5 et le LUT

LUT à 6 entrées et 2 sorties: permettant de construire des logiques plus sophistiques dans un seul slice.

Remarque

Formation VHDL Vahid MEGHDADI

28

Outil de développement

L’IDE (Integrated development environment)

- jusqu’en 2012 : ISE

- Depuis 2012 VIVADO

- La dernière version d’ISE : 14.7

En TP on utilise ISE qui supporte spartan 6.

Pour la série 7, on doit utiliser Vivado

Formation VHDL Vahid MEGHDADI

29

Conception circuit

o Les blocs reconfigurables

o Structure régulière de “logic cells”, connectée par un réseau d’interconnexions

o La configuration est stocké dans un SRAM, qui doit être chargé au démérrage

EP

RO

M

Introduction

Formation VHDL Vahid MEGHDADI

30

HDL(VHDL /Verilog)

Synthesize

Netlist

Map

Place

Route

Bitstream

o Hardware design is traditionally done by modeling the system in a hardware description language

o An FPGA “compiler” (synthesis tool) generates a netlist,

o which is then mapped to the FPGA technology,

o the inferred components are placed on the chip,

o and the connecting signals are routed through the interconnection network.

Design flow

Introduction

Formation VHDL Vahid MEGHDADI

31

Synthèse HDL

⊕

RegisterRegister

aa

bboutputoutput

clkclk

resetreset

clearclear

DD QQ

process(clk, reset)

begin

if reset = ‚1‘ thenoutput <= ‚0‘;

elsif rising_edge(clk) thenoutput <= a XOR b;

end if;

end process;

HDL(VHDL /Verilog)

Synthesize

Netlist

Map

Place

Route

Bitstream

Introduction

Formation VHDL Vahid MEGHDADI

32

HDL(VHDL /Verilog)

Synthesize

Netlist

Map

Place

Route

Bitstream

⊕

RegisterRegister

aa

bboutputoutput

clkclk

resetreset

clearclear

DD QQ

Technology Mapping

Introduction

Formation VHDL Vahid MEGHDADI

33

Placement & Routage

HDL(VHDL /Verilog)

Synthesize

Netlist

Map

Place

Route

Bitstream

Introduction

Formation VHDL Vahid MEGHDADI

34

Système embarqué traditionnel

Power Supply

CLKCLK

CLKcustomIF-logic

SDRAM SDRAMSRAM SRAMSRAM

Memory Controller

UARTLC

DisplayController

InterruptController

Timer

AudioCodec

CPU(uP / DSP) Co-

Proc.

GP I/O

AddressDecode

Unit

EthernetMAC

Images by H.Walder

Introduction

Formation VHDL Vahid MEGHDADI

35

FPGACLKCLK

CLKcustomIF-logic

SDRAM SDRAMSRAM SRAMSRAM

Memory Controller

UART

DisplayController

Timer

Power Supply

LC

AudioCodec

CPU(uP / DSP) Co-

Proc.

GP I/O

AddressDecode

Unit

EthernetMAC

InterruptController

Images by H.Walder

Système embarqué traditionnel

Introduction

Formation VHDL Vahid MEGHDADI

36

System on Chip Configurable (CSoC)

Power Supply

SDRAM SDRAMSRAM SRAMSRAM

LC

AudioCodec EPROM

Images by H.Walder

Introduction

Formation VHDL Vahid MEGHDADI

37

Avantages

Moins de composantes physiques

Cycle de conception plus rapide

Programmable sur le circuit (Mise à jour, modification...)

Plus performant grâce à l’intégration

Horloge peut être plus rapide dans la puce que sur le circuit imprimé

Optimisation entre modules possible

Introduction

Formation VHDL Vahid MEGHDADI

38

Chapitre : Introduction A VHDL

Introduction au langage

VHDL

Introduction A VHDL

Formation VHDL Vahid MEGHDADI

39

V H D L

V VHSIC (Very High Speed Integradted Circuit)

H Hardware

D Description

L Language

Introduction A VHDL

Formation VHDL Vahid MEGHDADI

40

Un peu d’histoire

•Début des années 80•la nécessité d’un langage non ambigu des systèmes matériels pour intégration à grande échelle•normalisation pour être indépendant du fournisseur

•Norme définitive adoptée en 1987 : IEEE Std 1076

•La norme a été revue en 93, 2000 et 2002

•Les premiers outils de synthèse en 1995

Introduction A VHDL

Remarque

Formation VHDL Vahid MEGHDADI

41

Qu’est ce que on attend de VHDL

• VHDL est utilisé pour

• Décrire des circuits numériques

• Décrire des machines à états

• Préparer des signaux de test pour simuler cette écriture

• Le langage concurrent : Verilog

Introduction A VHDL

Formation VHDL Vahid MEGHDADI

42

Qu’est ce que on attend des outils de synthèse

•Une fois le programme en VHDL est écrit, il faut maintenant

le réaliser

•Synthèse logique : générer des fonctions logiques à partir

du programme

•Implémentation : adapter la logique synthétisée à la cible

(FPGA, CPLD)

•Génération : Générer un fichier binaire à télé-charger sur

le « device »

Introduction A VHDL

Formation VHDL Vahid MEGHDADI

43

Niveau d’abstraction

Comportemental

RTL

Logique

Layout

Introduction A VHDL

VHDL

Synthèsecomportemental

Synthèselogique

Placementroutage

Formation VHDL Vahid MEGHDADI

44

Il existe 5 catégories d’unité de conception

•L’entité (mot clé entity)

Décrit un système vu extérieur (boîte noire)

•L’architecture (mot clé architecture)Décrit l’intérieur (le fonctionnement) d’une boîte noire.

•La configuration (mot clé configuration)

•La déclaration de paquetage (mot clé package)

•Le corps de paquetage (mot clé package body)

Structure du VHDL

Chapitre : Structure du VHDL

Circuit principal Circuit

principal

Package (librairie)

Formation VHDL Vahid MEGHDADI

45

Minimum design en VHDL

Deux unités obligatoires

• une entité

• une architecture Un circuit décrit en VHDL

Déclaration d’entité

Architecture

Formation VHDL Vahid MEGHDADI

46

Exemple simple: entité

Exemple: L’entité du circuit ci-contre qu’on appellera « AOI»

entity AOI is

Port(

A,B,C,D: in std_logic;

F : out std_logic);

end AOI;

AOI

L’entité déclare la vue externe du circuit : les ports d’entrée-sorties et leur type. Elle peut aussi déclarer des paramètres.

Formation VHDL Vahid MEGHDADI

4747

ENTITY nand_gate IS

PORT(

a : IN STD_LOGIC;

b : IN STD_LOGIC;

z : OUT STD_LOGIC

);

END nand_gate;

Reserved words

Entity namePort names Port type

Semicolon

No Semicolon

after last port

Port modes (data flow directions)

Entité décortiquée

ENTITY nand_gate IS PORT(a,b: IN STD_LOGIC;z : OUT STD_LOGIC

);END nand_gate;

Même chose mais en moins lisible, non recommandée !!

Entité

Formation VHDL Vahid MEGHDADI

48

Remarque

std_logic définit un type plus que binaire. En fait, un objet de type std_logic peut recevoir des valeurs ‘0’ et ‘1’ mais aussi autres valeurs comme par exemple « haute impédance ».

On verra les types bien tôt.

On remarque aussi les modes des signaux: in, out. Il y en a d’autres: buffer, inout.

Formation VHDL Vahid MEGHDADI

49

Exemple simple: architecture

architecture v1 of AOI is

-- les déclarations

begin

F <= not((A and B) or (C and D));

end v1;

L’architecture définit le fonctionnement du circuit.

Formation VHDL Vahid MEGHDADI

50

Remarque

On remarque l’opérateur d’affectation <=

Les opérateurs logiques "and", "or", "nor", "nand" et "not"font parti des opérateurs connus du langage.

On remarque aussi que -- est utilisé pour des commentaires.

Il existe deux parties dans l’architecture - avant begin : zone des déclarations

- Après begin : la partie "exécutable".

Formation VHDL Vahid MEGHDADI

51

Exemple simple: architecture bis

architecture v2 of AOIis

signal I1,I2,I3: std_logic;

begin

I1 <= A and B;

I2 <= C and D;

I3 <= I1 or I2;

F <= not I3;

end v2;

I1, I2 et I3 sont des signaux internes.

Formation VHDL Vahid MEGHDADI

52

Principe de concurrence

architecture v3 of AOI is

signal I1,I2,I3: std_logic;

begin

I1 <= A and B;

I2 <= C and D;

I3 <= I1 or I2;

F <= not I3;

end v3;

architecture v2 of AOI is

signal I1,I2,I3: std_logic;

begin

I1 <= A and B;

F <= not I3;

I2 <= C and D;

I3 <= I1 or I2;

end v2;

architecture v4 of AOI is

signal I1,I2,I3: std_logic;

begin

F <= not I3;

I3 <= I1 or I2;

I2 <= C and D;

I1 <= A and B;

end v4;

Tous les mêmes !

Formation VHDL Vahid MEGHDADI

53

Dans une architecture, toutes les instructions sont exécutées en parallèle : elles sont concurrentes et non pas « séquentielles ».

La partie après "begin" dans une architecture est une zone

concurrente.

Remarque

Formation VHDL Vahid MEGHDADI

54

Décrire des délais

Dans des circuits réels, les portes logiques présentent des délais.

On pourra aussi les décrire.

Formation VHDL Vahid MEGHDADI

55

Délai dans les affectations

- Une affectation sera déclenchée quand un évènement arrive

- Un évènement est un changement de valeur d’un signal

- Pour l’instruction ci-dessous, cet évènement est le passage de A de 0 à 1.

- Cependant, l’affectation se concrétise après 2 ns.

Formation VHDL Vahid MEGHDADI

56

Attention: l’instruction d’affectation retardé est importante en simulation, par contre n’a aucun effet en

synthèse. L‘outil de synthèse ignore « after »:

Pour la synthèse :I1 <= A and B after 2 ns; ≡ I1 <= A and B;

Le circuit qui sera réalisé présentera un délai qui dépendra de la technologie utilisé, longueur des câblage, etc.

TRES IMPORTANT

Formation VHDL Vahid MEGHDADI

58

Exemple

Demi-additionneur

A

B

SUM

C

A B SUM C

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Architecture

A

B

SUM

C

Formation VHDL Vahid MEGHDADI

59

entity DEMI_ADD is

port (A,B: in std_logic;

SUM,C: out std_logic);

end DEMI_ADD;

architecture COMPORT of DEMI_ADD is

begin

SUM <= A xor B; --instruction concurrente

C <= A and B; --instruction concurrente

end COMPORT;

Programme VHDL correspondant

Architecture

Formation VHDL Vahid MEGHDADI

61

Hiérarchie in VHDL

- Un bloc conçu, testé, et fonctionnel peut être réutilisé. On l’appelle component.

- Dans un design qui utilise ce component

- On déclare entité du component

- On instancie un exemplaire de ce component dans la zone concurrente

- On procède au câblage de ce component

Formation VHDL Vahid MEGHDADI

62

Exemple : multiplexeur 2 voies

Si SEL=‘0’, Y <=X1, et si SEL=‘1’, Y<=X2

Formation VHDL Vahid MEGHDADI

67

En VHDL, il existe deux types d’instructions

• Instructions concurrentes

• à écrire dans la zone concurrente de l’architecture

• elles sont exécutées simultanément

• l’ordre de l’écriture n’a pas d’importance

• Instruction séquentielles

• à écrire dans les « process »

• elles sont exécutées dans l’ordre

Instructions concurrentes ou séquentielles

Formation VHDL Vahid MEGHDADI

68

A

B I

CS

I <= A or B;

S <= I and C

S <= I and C

I <= A or B;

Zone concurrente

Exemple

Formation VHDL Vahid MEGHDADI

69

Instruction concurrente conditionnelle

Exemple d’instructions concurrentes:

Affectation conditionnelle: when – else (équivalent de if-then-else dans d’autre langages)

Formation VHDL Vahid MEGHDADI

70

Instruction concurrente sélective

• La condition se fait sur un seul objet (comme le signal sel ci-dessous)

• Le mot clé others doit être utilisé pour couvrir les cas non spécifiés

Formation VHDL Vahid MEGHDADI

71

Remarque

L’affectation sélective produit très souvent un circuit plus simple (par rapport à l’affectation conditionnelle) parce qu’il n’y a pas de priorité dans différentes branches. De plus, la condition est à tester sur un seul objet.

Exemple

Formation VHDL Vahid MEGHDADI

72

with HEX select

LED<= "1111001" when "0001", --1

"0100100" when "0010", --2

"0110000" when "0011", --3

"0011001" when "0100", --4

"0010010" when "0101", --5

"0000010" when "0110", --6

"1111000" when "0111", --7

"0000000" when "1000", --8

"0010000" when "1001", --9

"0001000" when "1010", --A

"0000011" when "1011", --b

"1000110" when "1100", --C

"0100001" when "1101", --d

"0000110" when "1110", --E

"0001110" when "1111", --F

"1000000" when others; --0

Circuitcombinatoire

7

4

Zone concurrente

Exemple instruction « with-select »Codeur sept-segment

Formation VHDL Vahid MEGHDADI

73

entity ADDER is

port (A,B :in std_logic_vector(7 downto 0);

SEL : in std_logic;

S : out std_logic_vector(7 downto 0));

end ADDER;

Exemple ALU

Zone concurrente

architecture COMPORT of ADDER is

Begin

with SEL select

S <= A+B when '0',

A-B when others;

-- ou on peut utiliser when-else

-- S <= A+B when SEL=‘0’ else A-B;

end COMPORT;

Remarque

Formation VHDL Vahid MEGHDADI

75

Process

• Process est une instruction concurrente : donc à écrire dans une architecture (après begin),

• Les différents process d'une architecture s'exécutent tous en parallèle

•Process génère une zone séquentielle

Process

Formation VHDL Vahid MEGHDADI

76

•Syntaxe de process :

label : -- optionnelprocess (liste de sensibilité)

{partie déclarative}begin

suite d’instructions séquentiellesend process;

•Notion très importante : Un process s'exécute (se réveille) quand un des signaux de la liste de sensibilité change de valeur.

•Un fois on arrive à la fin du process, celui-ci rendort jusqu’à l’arrivée d’un évènement sur un des signaux de sa liste de sensibilité,

Syntaxe de process

Process

Formation VHDL Vahid MEGHDADI

77

•Ils s'écrivent uniquement dans une zone séquentielle: après

le « begin » d’un process

• instruction d'attente (wait)

• instruction d'affectation (temporisée)

• instruction conditionnelle (if)

• instruction sélective (case)

Instructions séquentielles

Process

Formation VHDL Vahid MEGHDADI

78

L’exécution des lignes d’un process s’arrête quand on arrive à la commande « wait », on dit que le process est suspendu ! Le processpourra redémarrer suivant une condition.

•Wait

•wait until condition;

•wait until A=‘ 1 ’;•wait until CLK’event and CLK=’1’;

• wait for time expression;

•wait for 5 ns;

• wait on signal;

•wait on A , B

Instructions wait

Process

Formation VHDL Vahid MEGHDADI

79

Remarque

La génération de l’horloge et en même temps d’un signal Reset.

clock_gen: process

begin

CLK_TB <= '1';

wait for 5 ns;

CLK_TB <= '0';

wait for 5 ns;

end process;

---------------------------------------

reset_gen: process

begin

RST_TB <= ‘0’; wait for 5ns;

RST_TB <= ‘1’; wait for 15ns;

RST_TB <= ‘0’;

wait;

end process;

---------------------------------------

inst: counter

port map ( CLK => CLK_TB, RST => RST_TB, Q => DATA_OUT );

Instructions séquentielles

Instructions séquentielles

Instructions concurrentes

Formation VHDL Vahid MEGHDADI

80

if condition then

sequential statements[elsif condition then

sequential statements ][elsif condition then

sequential statements ][else

sequential statements ]end if;

Instructions conditionnelle

Process

Formation VHDL Vahid MEGHDADI

81

Instruction sélective

Permet de sélectionner une suite d’instructions à exécuter en fonction de la valeur d’une expression.

case EXPRESSION iswhen VAL1 => suite d’instructions séquentielleswhen VAL2|VAL3|VAL4 => suite d’instr séquentielleswhen VAL5 to VAL7 => suite d’instr séquentielleswhen others => suite d’instr séquentielles

end case;

•L’ordre des branches n’a pas d’importance (sauf others)•La branche « others » est obligatoire si toutes les valeurs de l’expression ne sont pas énumérées.

Process

Formation VHDL Vahid MEGHDADI

83

entity MUX_4 isport (S1, S0, A, B, C, D: in std_logic;Z: out std_logic);

end MUX_4;

architecture behav_MUX_4 of MUX_4 isbegin

P1: process (S1, S0, A, B, C, D) - - la liste de sensibilitébegin

if (( not S1 and not S0 )=’1’) then Z <= A;elsif (( not S1 and S0) = ‘1’) then Z <=B;elsif ((S1 and not S0) =’1’) then Z <=C;else Z <=D;end if;

end process P1;

end behav_MUX_4;

Exemple (avec if)

Process

Remarque

Formation VHDL Vahid MEGHDADI

84

Exemple (avec case)

entity MUX_4 isport ( S : in std_logic_vector(1 downto 0);

A, B, C, D: in std_logic; Z: out std_logic );end MUX_4;

architecture behav_MUX_4 of MUX_4 isbegin

P1: process (S, A, B, C, D) - - la liste de sensibilitébegin

case S iswhen "00" => Z <= A;when "01" => Z <= B;when "10" => Z <= C;when "11" => Z <= D; -- ou when others => Z <= D;end case;

end process P1;

end behav_MUX_4;Process

Remarque

Formation VHDL Vahid MEGHDADI

85

Affectation séquentielle

Attention : affectation d’une valeur à un signal dans un process n’est pas immédiate !

L’affectation se réalise quand le process est suspendu, ou quand on arrive à la fin du process.

Dans un process tous les signaux sont constants, ils sont actualisés quand le process est suspendu (end de process, ou wait)

Exemple:

process(A)

begin

A <= ‘0’; --ici le signal A ne recevra pas ‘0’

B <= A; --ici donc, B recevra l’ancienne valeur de A mais

--au moment où le process sera suspendu

end process; --c’est ici que A reçoit ‘0’ et B reçoit

--l’ancienne valeur de A

Formation VHDL Vahid MEGHDADI

86

Attention !

Le process ci-dessous ne produira pas le signal ci-contre

SIG

Process (x)begin

SIG <= '0';SIG <= '1';SIG <= '0';

end process;

SIG

Process

Remarque

Formation VHDL Vahid MEGHDADI

87

Circuits séquentiels

Trois types de circuit

• Combinatoire

• Séquentiel

• Synchrone

Formation VHDL Vahid MEGHDADI

88

process combinatoire

Un process n’est plus combinatoire si au moins une des conditions suivantes est vérifiée :

• la liste de sensibilité ne comprend pas tous les signaux lus

• les signaux ne sont pas affectés quelle que soit la branche

• une variable est lue avant d'être affectée

Le circuit généré aura donc quelque part une mémoire !

Circuits séquentiels

Formation VHDL Vahid MEGHDADI

89

Exemple: Verrou ou Latch

Bascule à verrouillage

entity L isport (D,EN : in std_logic;

Q : out std_logic);end L;

architecture A of L isbegin

processbegin

wait on D,EN;if EN='1' then Q <= D;end if;

end process;end A;

architecture A of L isbegin

process (D,EN)begin

if EN='1' thenQ <= D;

end if;end process;

end A;

Circuits séquentiels

Ce

qu

’on

pré

fère

!

Formation VHDL Vahid MEGHDADI

90

Registre (latch synchrone)

process (CLK)begin

if CLK'event and CLK='1' thenQ <= D;

end ifend process;

Circuits séquentiels

Un circuit synchrone sur le front d’un signal (CLK)

process (CLK)begin

if rising_edge(CLK) thenQ <= D;

end ifend process;

D Q

CLK

Bascule D

D Q

CLK

Registre de taille 8 dépendant du type de Q et D

88

Formation VHDL Vahid MEGHDADI

91

Registre avec SET ou RESET

architecture A of R isbegin -- set asynchrone

process (SET,CLK)begin

if SET = '1' then Q <= '1';elsif CLK'event and CLK='1'

then Q <= D;end if;

end process;end A;

entity R isport (D,CLK,SET: in std_logic;

Q: out std_logic);end R;

architecture A of R isbegin -- set synchrone

process (CLK)begin

if CLK'event and CLK='1' thenif SET = '1' then Q <= '1';else Q <= D;end if;

end if;end process;

end A;

Circuits séquentiels

Formation VHDL Vahid MEGHDADI

92

Exemple : compteur

Création d’un compteur 3 bits:

000-001-010-011-100-101-110-111-000-001-…

Supposons que le FPGA reçoit un signal CLK à l’entrée et qu’il sort 3 fils représentant les 3 bits du compteur.

-- signal cmp: std_logic_vector(2 downto 0);

process(CLK)

begin

if CLK’event and CLK=‘1’ then

cmp <= cmp+1;

end if;

end process;

Exercice: tracer les chronogrammes des signaux CLK et cmp.

Formation VHDL Vahid MEGHDADI

93

Exemple

Créer le signal “trig” à partir du signal d’horloge CLK

CLKtrig

-- signal cmp: integer range 0 to ?;

process(CLK)

begin

if CLK’event and CLK=‘1’ then

trig <= ‘0’; cmp <= cmp + 1;

if cmp = ? Then

cmp <= 0; trig <= ‘1’;

end if;

end if;

end process;

����� � ��/4

0 1 2 3 0 1 2 3 0 1 2

Formation VHDL Vahid MEGHDADI

95

En VHDL, il existe 3 classes d’objet pour garder ou représenter des data.

- signal : représente des fils, des bus, des registres

- variable : comme les variables dans d’autres langages

- constant : dont la valeur ne change pas

Tout objet est typé.

Objets en VHDL

Formation VHDL Vahid MEGHDADI

96

Constants

Exemple:

C’est une valeur explicite

constant PIN_CODE: bit_vector(3 downto 0) :="0110";

constant NUMBER_OF_BITS: integer :=0;

Utilisation des constants rend la modification du programme plus simple.

Formation VHDL Vahid MEGHDADI

97

Variable

variable current_bit: std_logic := ‘0’;

Initialisation optionnelle

• Les variables sont utilisées uniquement dans les process.

• Elles sont déclarées dans le process avant le mot clé « begin » (c’est le begin du process).

• Contrairement aux signaux, les variables sont affectées tout de suite, on n’a pas besoin d’attendre la suspension du process.

• Affectation se fait par ":=" et non pas par "<=" :

• current_bit := not current_bit;

Formation VHDL Vahid MEGHDADI

98

Signal

signal carry_out : std_logic := '0';

Initialisation optionnel,

souvent ignoré en synthèse

donc utile seulement pour

simulation

- Les signaux sont comme les câbles (fils) dans un circuit

- Ils sont utilisés pour connecter les éléments concurrents d’un circuit

- L’affectation à un signal peut être retardé (uniquement en simulation, en synthèse le retard est imposé par le circuit !):

carry_out <= '1' after 10ns;

- Les signaux sont déclarés soit dans l’entité (les ports d’entrée –sortie), soit avant « begin » d’une architecture.

Formation VHDL Vahid MEGHDADI

99

Signaux et variables

Les signaux interconnectent les éléments concurrents

Variables peuvent être utilisées à l’intérieur des process et ne sont pas visibles en dehors de process.

Formation VHDL Vahid MEGHDADI

100

Remarque

Variables:

- Peuvent être utilisées dans le process où ils sont déclarées

- Ne peuvent pas apparaitre dans la liste des sensibilités

- Ne peuvent pas être retardées

- affectation immédiate

Signaux

- Peuvent être utilisés pour relier des process

- Peuvent apparaitre dans la liste des sensibilités des process

- Peuvent être retardés

Formation VHDL Vahid MEGHDADI

102

VHDL est un langage très typés.

- Tout élément doit être associé à un type

- Conversion des types est possible moyennant des fonctions explicites

- Il est possible de définir un sous-type qui héritera les contraintes du type d’origine

4 catégories de types

- Type scalaire : integer, reals, physique, énuméré

- Type composite: array, records

- Type accès: comme des pointeurs

- Type File

Types en VHDL

Formation VHDL Vahid MEGHDADI

103

Type scalaire

•énumérétype T_FEU is (ROUGE, ORANGE, VERT);signal FEU : T_FEU;

•entiersignal COMPT : integer range 0 to 15;

•flottantesignal MASSE : REAL; -- de -1e38 à 1e38

•physique qui est un entier avec l'unité correspondanttype TIME is range … to … --64 bitsunits fs; ps=1000 fs; ns=1000 ps; …hr=60 min;end units;T <= 5 ns;

Types en VHDL

Formation VHDL Vahid MEGHDADI

104

Remarque

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483647 to 2147483647units

fs;ps = 1000 fs;ns = 1000 ps;us = 1000 ns;ms = 1000 us;sec = 1000 ms;min = 60 sec;hr = 60 min;

end units;

subtype natural is integer range 0 to integer’high;

subtype positive is integer range 1 to integer’high;

Formation VHDL Vahid MEGHDADI

105

Type énuméré

Les types ci-dessous sont des types prédéfinistype BOOLEAN is (FALSE, TRUE);

type BIT is ('0' , '1');

type severity_level is (note, warning, error, failiure);

type character is (…,’A’,’B’,…);

On peut définir son propre type. On déclare toutes les valeurs qu'un objet de ce type peut prendre.

type T_FEU is (ROUGE, ORANGE, VERT);

signal FEU : T_FEU;

type ETAT is (INIT, LECT, ECR, ATT);

Types en VHDL

Formation VHDL Vahid MEGHDADI

106

Type entier (scalaire)

C'est un type prédéfinitype integer is range

-2_147_483_648 to 2_147_483_647

On peut définir un sous type :subtype nom_de_sous_type is

type_de_base contraintes;

Le type Natural existe dans le library standard:

subtype NATURAL is INTEGER

range 0 to INTEGER'high

Types en VHDL

Formation VHDL Vahid MEGHDADI

107

•Il existe des signaux logiques à plusieurs états:0, 1, mais aussi haute impédance, don’t care, non déterminé, …

•Le type "std_logic" remplace le type "bit" pour permettre d’avoir 9 états différents

•Utilisation de librairie IEEE.std_logic_1164•exemple

library IEEE;use IEEE.STD_LOGIC_1164.ALL;signal SORTIE, Q: std_logic;…SORTIE <= ‘Z’; -- haute impédanceQ <= ‘1’;

Logique à valeurs multiples (scalaire)

Types en VHDL

Formation VHDL Vahid MEGHDADI

108

Le type std_logic :

‘ U ’ non initialisé

‘ X ’ non connu

‘ 0 ’ logique 0

‘ 1 ’ logique 1

‘ Z ’ haute impédance

‘ W ’ non connu

‘ L ’ logique 0

‘ H ’ logique 1

‘ - ’ don’t care

Strong drive

weak drive

Le type std_logic

Types en VHDL

‘0’

‘H’

‘0’

‘1’

‘L’VDD

Formation VHDL Vahid MEGHDADI

109

Haute impédance un type résolu

Les signaux à trois état doivent être résolus. S’il est fixé à ‘0’ par un circuit et à ‘Z’ par un autre, le simulateur ne doit pas s’affoler mais doit savoir que le ‘0’ remporte sur ‘Z’.

Formation VHDL Vahid MEGHDADI

110

Deux types sont considérés : tableau et record

•Un tableau est un ensemble d’éléments du même type

•Pour un ensemble de std_logic, nous avons le type prédéfini std_logic_vector : on définit la taille et l'ordre des éléments

signal BUS1 : std_logic_vector (7 downto 0); -- type prédéfini

signal REG : std_logic_vector (0 to 31);

Type composite

Types en VHDL

Formation VHDL Vahid MEGHDADI

111

Accès aux éléments

•Déclaration:A,B: std_logic_vector(15 downto 0);

•Accès direct :A(3) <= ‘1’;B(15) <= ‘0’;

•Accès par tranchesA(15 downto 12) <= "1011"; B(0 to 2) <= "111" ; -- erreurA(10 downto 2) <= B(15 downto 7);

Types en VHDL

Formation VHDL Vahid MEGHDADI

112

Accès aux éléments de tableaux

• Par agrégat• Notation positionnelle

A(3 downto 1) <= ('0', '1', B(15));B <= ('1','1',others => '0');

• Notation par nommageA <= (1 =>'1', 3 =>'1',others =>'0');

• Par concaténationsignal A,B,C,D : std_logic;signal BYTE : std_logic_vector(7 downto 0);signal Z_BUS,A_BUS : std_logic_vector(3 downto 0);Z_BUS <= A & C & D & B;BYTE <= Z_BUS & A_BUS;

Types en VHDL

Formation VHDL Vahid MEGHDADI

113

SIGNAL a: STD_LOGIC;

SIGNAL b: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL c: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL d: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL e: STD_LOGIC_VECTOR(15 DOWNTO 0);

SIGNAL f: STD_LOGIC_VECTOR(8 DOWNTO 0);

……….

a <= ‘1’;

b <= ”0000”; -- Base Binaire par défaut

c <= B”0000”; -- Base Binaire explicite

d <= ”0110_0111”; -- Utiliser ‘_’ pour augmenter la lisibilité

e <= X”AF67”; -- Base Hexadecimale

f <= O”723”; -- Base Octale

Exemples

Types en VHDL

Remarque

Formation VHDL Vahid MEGHDADI

114

•type MY_WORD is array (15 downto 0) of std_logic;•signal mem_addr : MY_WORD;•mem_addr(10 downto 5) <= "101010";

•type YOUR_WORD is array (0 to 15) of std_logic;•signal data_word : YOUR_WORD := “1101100101010110”;

•type T_VAR is array (0 to 7) of integer;•constant setting : T_VAR := (2,4,6,8,10,12,14,16);

•type T_MATRIX is array (0 to 3, 1 to 2) of natural;•variable data_arr : T_MATRIX :=((0,2), (1,3), (4,6), (5,7));•data_arr(0,2) := 12;

•type array_name is array (type range <>) of element_type;-- taille est-- définie quand on déclare l'objet

•type MATRIX is array (integer range <>) of integer;•variable MATRIX8: MATRIX (2 downto -8) := (3, 5, 1, 4, 7, 9, 12, 14, 20, 18);

Exemples

Types en VHDL

Remarque

Formation VHDL Vahid MEGHDADI

115

•On peut définir un type tableau d’éléments scalairetype real_vect is array (natural range <>) of real;

signal temp : real_vect(0 to 4);

Remarque: le type « real_vect » a été créé par vous.

On peut aussi:type real_vect is array (2 to 7) of real;

signal temp : real_vect;

•On peut définir aussi un tableau de compositestype MEMO is array (0 to 1023) of std_logic_vector(7 downto 0);

signal A,B : MEMO;

Déclaration d’un objet de type array

Formation VHDL Vahid MEGHDADI

116

Enregistrement (record)

Ensemble d'éléments de types différents

type NAME isrecord

identifier : type_indication;:

identifier : type_indication;end record;

type PAQUET isrecord

mot_unique : std_logic_vector (7 downto 0);data : std_logic_vector (23 downto 0);CRC : std_logic_vector( 5 downto 0);num : integer range 0 to 1023;

end record;signal paq_rec : PAQUET;paq_rec.CRC <= "111000";

Types en VHDL

Formation VHDL Vahid MEGHDADI

118

Les opérateurs

Par ordre de priorité croissante

•Opérateur logique : and, or, nand, nor, xor, xnor, sll, srl, sra, rol, ror

•Opérateur de comparaison : =, /=, <, <=, >, >=

•Opérateur d’addition : +, -, &

•Opérateur mathématique : *, /, mod, rem

•Opérateur de signe : -

•Opérateur divers : **, abs, not

Structure du VHDL

Formation VHDL Vahid MEGHDADI

120

Process combinatoire

Un circuit combinatoire donne toujours les mêmes sorties

pour les mêmes entrées

Un process est combinatoire si les conditions suivantes sont toutes respectées :

•le process comporte une liste de sensibilité

•la liste de sensibilité comprend tous les signaux lus

•tous les signaux doivent être affectés quelle que soit les entrées (Attention dans un "if-else" ou dans un "case")

•toutes les variables doivent être affectées avant d'être lues

Formation VHDL Vahid MEGHDADI

121

Circuits combinatoires : équation logique

Architecture COMB1 of NONET is

begin

--équation logique

S <= A nand B;

end COMB1;

Architecture COMB3 of NONET is

begin

--Traduction de la table

--de vérité dans un process

process(A,B)

begin

if A='1' and B='1' then

S <= '0';

else

S <= '1';

end if;

end process;

end COMB3;

Architecture COMB2 of NONET is

begin

--Traduction de la table

--de vérité dans un process

S <= '0' when A='1' and B='1'

else '1';

end COMB2;

Formation VHDL Vahid MEGHDADI

122

Exemple

Transcription d’une table de vérité

A(2) A(1) A(0) S(2) S(1) S(0)0 0 0 0 0 00 0 1 0 0 10 1 0 0 1 10 1 1 0 1 01 0 0 1 1 01 0 1 1 1 11 1 0 1 0 11 1 1 1 0 0

Formation VHDL Vahid MEGHDADI

123

Architecture AVEC_IF of CIRCUIT

signal A,S : std_logic_vector (2 downto 0);

begin

process(A)

begin

if A = "000" then S <= "000";

elsif A ="001" then S <= "001";

elsif ...

end if;

end process;

end AVEC_IF;

Affectation conditionnelle

Dans une zone séquentielle (process)

Formation VHDL Vahid MEGHDADI

124

Affectation sélective séquentielle

Architecture AVEC_CASE of CIRCUIT

signal A,S : std_logic_vector (2 downto 0);

begin

process(A)

begin

case A is

when "000" => S <= "000"

when "001" => S <= "001"

when "011" => S <= "010"

…

end case

end process;

end AVEC_CASE;

Dans une zone séquentielle (process)

Circuits combinatoires

Formation VHDL Vahid MEGHDADI

125

Affectation sélective concurrente

Architecture AVEC_WITH of CIRCUIT

signal A,S : std_logic_vector (2 downto 0);

begin

with A select

S <= "000" when "000" ,

"001" when "001" ,

"011" when "010" ,

"110" when "100" ,

…

"000" when others;

end AVEC_WITH;

Dans une zone concurrente (architecture)

Circuits combinatoires

Remarque

Formation VHDL Vahid MEGHDADI

126

Affectation non conditionnelle

Architecture DIRECT of CIRCUIT

signal A,S : std_logic_vector (2 downto 0);

begin

S(2) <= (A(2) and not A(1) and not A(0))

or (A(2) and not A(1) and A(0))

or (A(2) and A(1) and not A(0))

or (A(2) and A(1) and A(0));

S(1) <= (not A(2) and A(1) and not A(0))

or (not A(2) and A(1) and A(0))

or (A(2) and not A(1) and not A(0))

or (A(2) and not A(1) and A(0));

…

Dans une zone concurrente (architecture)

Circuits combinatoires

Remarque

Formation VHDL Vahid MEGHDADI

127

Affectation conditionnelle concurrente

Architecture AVEC_WHEN of CIRCUIT

signal A,S : std_logic_vector (2 downto 0);

begin

S <= "000" when A= "000"

else "001" when A= "001"

else "011" when A= "010"

else "010" when A= "011"

else "110" when A= "100"

else "111" when A= "101"

else "101" when A= "110"

else "100" when A= "111"

else "000";

end AVEC_WHEN;

Dans une zone concurrente (architecture)

Circuits combinatoires

Remarque

Formation VHDL Vahid MEGHDADI

128

entity ALU is

port(A : in std_logic_vector(7 downto 0);

B : in std_logic_vector(7 downto 0);

Sel: in std_logic_vector(1 downto 0);

Res: out std_logic_vector(7 downto 0));

end ALU;

-- Sel="00" => Addition

-- Sel="01" => Soustraction

-- Sel="00" => et logique bit à bit

-- Sel="00" => ou logique bit à bit

architecture behv of ALU is

begin

process(A,B,Sel)

….

end process;

end behv;

Exemple : ALURemarque

Formation VHDL Vahid MEGHDADI

129

process(A,B,Sel)

begin

case Sel is

when "00" =>

Res <= A + B;

when "01" =>

Res <= A + (not B) + 1; -- ou A - B

when "10" =>

Res <= A and B;

when "11" =>

Res <= A or B;

when others =>

Res <= "--";

end case;

end process;

Exemple : ALU (suite)Remarque

Formation VHDL Vahid MEGHDADI

130

Exemple : Multiplieur

Le but est de réaliser un multiplieur 4 bits fois 4 bits

A 1001

B *1101

---------

0000 1001

+0000 0000

+0010 0100

+0100 1000

----------

0111 0101

res(0)

A

44

0

5

(4 downto 1)

4

res(1)

5

(4 downto 1)

4

res(2)

5

(4 downto 1)

4

B(0)

B(1)

B(2)

B(3)

res(7 downto 3)

0

0

0

0

Remarque

Formation VHDL Vahid MEGHDADI

131

entity main is

Port ( A : in std_logic_vector(3 downto 0);

B : in std_logic_vector(3 downto 0);

RES : out std_logic_vector(7 downto 0));

end main;

architecture Behavioral of main is

begin

process (A,B)

variable result : std_logic_vector(7 downto 0);

begin

result := (others => '0');

for I in 0 to 3 loop

if B(I)='1' then

result(I+4 downto I) := result(I+4 downto I) + ('0' & A);

end if;

end loop;

RES <= result;

end process;

end Behavioral;

Exemple : Multiplieur (suite)Remarque

Formation VHDL Vahid MEGHDADI

132

Chapitre : Machine à états finis

•Toute information du passé est sauvegardée dans l’état actuel du circuit

•L’état interne est préservé dans des registres (bascules). Une machine à �

états comporte au moins log�� bascules.

•L’état prochain dépend de l’état actuel et des entrées

•Le changement d’état se fait sur le front de l’horloge

•Machine de Moore : les sorties ne dépendent que de l’état courant.

•Machine de Mealy : les sorties dépendent de l’état courant mais aussi des

entrées

Machine à états finis

Formation VHDL Vahid MEGHDADI

133

s0

s1s2

E1E2= "1-"

E1E2="0-"

E1E2= "10"

E1E2= "11"

Présentation graphique

•Les cercles présentent les états possibles

d’une machine à états finis

•Les flèches représentent les changements

possible

•Les conditions sont présentées sur les flèches

•Les changements d’état se réalisent sur le

front de l’horloge

•L’horloge est implicite

Formation VHDL Vahid MEGHDADI

134

Dans un automate synchrone il existe

•une logique combinatoire permettant le calcul de l'état suivant

•une logique combinatoire permettant le calcul des sorties

•une partie séquentielle synchrone qui se charge du changement d'état du système au moment voulu.

Deux types de réalisation

•un seul process regroupant les parties combinatoire et séquentielle (adapté aux petites machines)

•un process séquentielle synchrone pour changement d’état et deux process combinatoires (pour calculer l’état prochain et les sorties)

Séparation des logiques

Machine à états finis

Formation VHDL Vahid MEGHDADI

135

type T_ETAT is (E1, E2, E3);signal etat : T_ETAT;. . .Process(CLK)

beginif CLK'event and CLK='1‘ then

case etat iswhen E1 => -- mise à jour des sorties pour état E1

if <cond> then ETAT <= E3; end if;when E2 => -- mise à jour des sorties pour état E2

ETAT <= E3when E3 => -- mise à jour des sorties pour état E3

if <cond> then ETAT <= E1;elsif <cond> then ETAT <= E2;end if;

end case;end if;

end process;

D Q

CLK

Registre d’états

ENTREE

CLK

Implantation par un seul process

Machine à états finis

Logique combinatoire

État courant

• Process n’est pas combinatoire

• Très simple à écrire

• Ne convient pas aux machines complexes

Formation VHDL Vahid MEGHDADI

136

Implantation par des process séparés (plus robuste)

Fonction combin-

atoire

F

Fonction combin-

atoire

G

Registre d'états

S1

S2

E1

E2

H

RAZ

ETAT_FUTURETAT_COUR

Machine à états finis

MealyMoore

Formation VHDL Vahid MEGHDADI

137

•Déclaration des signaux :

signal E1,E2,S1,S2,H,RAZ : std_logic

•Déclaration des états :

type T_ETAT is (ETAT1, ETAT2, ETAT3);

signal ETAT_COUR, ETAT_FUTUR : ETAT;

•Avancement dans l’état (process synchrone)

REG : process (H, RAZ)

begin

if RAZ = ‘0’ then ETAT_COUR <= ETAT1;

elsif H’event and H = ‘1’ then

ETAT_COUR <= ETAT_FUTUR;

end if;

end process;

Programmation logique séparée

Machine à états finis

Formation VHDL Vahid MEGHDADI

138

Programmation de la partie combinatoire G

G : process (E1,E2,ETAT_COUR) -- Tous les signaux

-- d’entrée sont dans la liste de sensibilité

begin

case ETAT_COUR is

when ETAT1 =>

-- suivant la valeur de E1 et E2 on

-- affecte à ETAT_FUTUR une valeur

when ETAT2 =>

-- suivant la valeur de E1 et E2 on

-- affecte à ETAT_FUTUR une valeur

when ETAT3 =>

-- suivant la valeur de E1 et E2 on

-- affecte à ETAT_FUTUR une valeur

end case;

end process;

Machine à états finis

Attention aux conditions nécessaires pour qu’un process soit combinatoire !

Formation VHDL Vahid MEGHDADI

139

Programmation de la partie combinatoire F

F : process (E1,E2,ETAT_COUR) -- Tous les signaux

-- d’entrée sont dans la liste de sensibilité

begin

case ETAT_COUR is

when ETAT1 =>

-- suivant la valeur de E1 et E2 on

-- affecte aux sorties les valeurs correspondantes

when ETAT2 =>

-- suivant la valeur de E1 et E2 on

-- affecte aux sorties les valeurs correspondantes

when ETAT3 =>

-- suivant la valeur de E1 et E2 on

-- affecte aux sorties les valeurs correspondantes

end case;

end process;

Machine à états finis

Peut être intégré dans G !

Formation VHDL Vahid MEGHDADI

140

Rappels généraux (1)

•Les fonctions F et G peuvent être décrites dans le même process

•Si le process est synthétisé par un circuit séquentiel synchronisé sur front d’horloge, il ne doit comporter dans la liste de sensibilité que l’horloge et éventuellement une RAZ synchrone ou asynchrone et rien d'autre :

process(CLK,RESET) -- avec un Reset Asynchrone begin

if RESET='0' then ……………..elsif CLK'event and CLK='1' then……………………….end if;

end process,

Machine à états finis

Remarque

Formation VHDL Vahid MEGHDADI

141

•Si le process est synthétisé pour un circuit

combinatoire, il doit comporter dans la liste de

sensibilité tous les signaux lus.

•S’il y a un test (if ou case) pour un signal dans un

process combinatoire, ce test doit couvrir toues les

possibilités (ne pas oublier le else), et toutes les

sorties doivent être affectées dans toutes les

branches du test.

Rappels généraux (2)

Machine à états finis

Remarque

Formation VHDL Vahid MEGHDADI

142

F : process (E1,E2,ETAT_COUR) -- Tous les signaux -- d’entrée sont dans la liste de sensibilitébegin

case ETAT_COUR iswhen ETAT1 =>

if E1 = '0' and E2 = '0' thenS1 <= ‘0’; S2 <= ‘0’;

elsif E1 = ’1 ’ thenS1 <= ‘1’ ; S2 <= ‘0’;

else S1 <= ‘0’; S2 <= ‘1’;end if;

when ETAT2 => -- S1 et S2 <= …...when ETAT3 => -- S1 et S2 <= …...end case;

end process;

Exemple de la partie combinatoire F

Machine à états finis

Remarque

Formation VHDL Vahid MEGHDADI

144

Ecran VGA: Conception RTL

HS <= '1' when etat_cour = PW else '0';

Remarque

Formation VHDL Vahid MEGHDADI

145

FSM: process(etat_cour, count)begin

case etat_cour iswhen PW =>

if count = 96 thenetat_futur <= BP;

elseetat_futur <= PW;

end if;when BP =>

if count = 144 thenetat_futur <= DISP;

elseetat_futur <= BP;

end if;when DISP =>

if count = 784 thenetat_futur <= FP;

elseetat_futur <= DISP;

end if;

when others =>if count = 0 then

etat_futur <= PW;else

etat_futur <= FP;end if;

end case;end process;

type t_etat is (PW, BP, DISP, FP);

signal etat_cour, etat_futur : t_etat:=PW;

Ecran VGA Programme VHDL

Remarque

Formation VHDL Vahid MEGHDADI

147

Utilisation de « Clock Enable »

• Tous les évènements sont synchronisés sur le front (montant) de l’horloge.

• Pour exécuter une partie du code à des fréquences moins rapides que l’horloge, on utilise les signaux « clock enable ».

• Ce sont des impulsions dont la durée de ‘1’ est exactement une seule période d’horloge.

• La répétition de ces impulsions donne la fréquence d’exécution du code.

CLK

EN

ES

CLK

EN1

process(CLK)

begin

if CLK'event and CLK='1' then

if EN = '1' then

--suite d’instructions

end if;

end if;

end process;

Periodic Clock Enable Generation

T=10 ns

T=80 ns

T=210 ns

CLK

EN1

EN2

Timing

generator

CLKEN1

EN2

process (CLK)

begin

if rising_edge(CLK) then

EN1 <= ‘0’; EN2<=‘0’;

cmp1 <= cmp1 + 1;cmp2 <= cmp2 + 1;

if cmp1 = 7 then EN1 <= ‘1’;

cmp1 <= 0;

end if;

if cmp2 = 20 then EN2 <= ‘1’;

cmp2 <= 0;

end if;

end if;

end process;

Enable usage

To execute some lines at EN rate, use general CLK in conjunction with EN.

T=10 ns

T=80 ns

CLK

EN

A process

repeated every

80 ns

CLK

EN

process (CLK)

begin

if rising_edge(CLK) then

if EN = ‘1’ then

--

-- write the code here

--

end if;

end if;

end process;

Example : Two-digit timer

Create a hexa-decimal two-digit timer counting from 00 to FF

Input CLK frequency = 1 MHz

Timing

generator

CLK en

2-digit

counter

CLK

8

process (CLK)

begin

if rising_edge(CLK) then

en <= '0';

cmp <= cmp + 1;

if cmp = 999_999 then

en <= ‘1’;

cmp <= 0;

end if;

end if;

end process;

CLK

en

Event that should make

the counter to

increment.

process (CLK)

Begin

if rising_edge(CLK) then

if en = '1' then

counter <= counter + 1;

end if;

end if;

end process;

Example : Traffic light

Create a traffic light with Red: 14 sec, Green: 12 sec, and yellow 2 sec.

Input CLK frequency = 1 MHz

For this example we will use a state machine with three states : red, green and yellow.

We use a timer counting from 0 to 27 as below:

0 1 2 13 14 15 25 26 27

Red 14 sec Green 12 sec Yellow

2 sec

red

greenyellow

If timer=13,

next-state = green

If

timer=25

Next_state = yelllow

If timer=27,

Next_state = red process (CLK)

begin

if rising_edge(CLK) then

if en = '1' then

timer <= timer + 1;

if timer = 27 then

timer <= 0;

end if;

end if;

end if;

end process;

Example : Traffic light (continue …)

State machine creation

-- type definition

type traffic_light_T is (red, green, yellow);

Signal state, next_state : traffic_light_T := red;

-- state machine (combinatory)

process(state, timer)

begin

case state is

when red =>

if timer = 13 then next_state = green;

else next_state = red;

end if;

when green =>

if timer = 25 then next_state = yellow;

else next_state = yellow;

end if;

when others =>

if timer = 27 then next_state = red;

else next_state = yellow;

end if;

end case;

end process;

process (CLK)

begin

if rising_edge(CLK) then

if en = '1' then

state <= next_state;

end if;

end if;

end process;

State Register

next_state

EN

CLK

state

Comb

state

Timernext_state

Example : Traffic light, timing diagram

12timer

en

redstate

next_state red

14

green

green

green

green

15

Traffic_light

The entity

CLK

R

Y

G

R <= '1' when state = red else '0';

Y <= '1' when state = yellow else '0';

G <= '1' when state = green else '0';

process(state, timer)

begin

case state is

when red =>

if timer = 13 then next_state = green;

else next_state = red;

end if;

. . .

process (CLK)

begin

if rising_edge(CLK) then

if en = '1' then

state <= next_state;

end if;

end if;

end process;

CLK

13

red

green

Formation VHDL Vahid MEGHDADI

154

Exemples

process(CLK)

begin

if CLK’event and CLK=‘1’ then

REG <= REG(0) & REG(7 downto 1); -- rotate right

REG <= ‘0’ & REG(7 downto 1); -- shift right logical

REG <= REG(7) & REG(7 downto 1);

end if;

end process

Les valeurs signées

Z <= (X(7) & X(7 downto 0)) + (Y(7) & Y(7 downto 0));

Les valeurs non signées

Z <= (‘0’ & X(7 downto 0)) + (‘0’ & Y(7 downto 0));

Formation VHDL Vahid MEGHDADI

156

Préparation de l’horloge

Horloge de la carte est à 100 MHz

Supposons qu’une horloge à approximativement 50 KHz est nécessaire:

Une division par : 100 x 106 / 50 x 103 = 2000

CLK_EN_Gene : Process(CLK)Begin

if CLK’event and CLK=‘1’ thenCLK_EN <= ‘0’;cmp <= cmp + 1;if cmp = 1999 then

CLK_EN <= ‘1’;cmp <= 0;

end if;end if;

End process;

CLK CLK_EN

CLK_EN_Gene

cmp

CLK

CLK_EN

Programme VHDL

Formation VHDL Vahid MEGHDADI

157

Machine à états

type T_ETAT is (SEG1, SEG2, SEG3, SEG4);signal etat : T_ETAT;

process(CLK)begin

if CLK’event and CLK=‘1’ thenif CLK_EN = ‘1’ then

case ETAT iswhen SEG1 => etat <= SEG2;when SEG2 => etat <= SEG3;when SEG3 => etat <= SEG4;when SEG4 => etat <= SEG1;when others => etat <= SEG1;end case;

end if;end if;

end process;

-- une autre alternative

signal etat : integer range 0 to 3;

process(CLK)begin

if CLK’event and CLK=‘1’ thenetat <= etat + 1;

end if;end process;

Formation VHDL Vahid MEGHDADI

158

Circuit complet

with etat select

An <= "0111" when SEG1,

"1011" when SEG2,

"1101" when SEG3,

"1110" when others;

with etat select

HEX <= "0001" when SEG1,

"1001" when SEG2,

"0100" when SEG3,

"0101" when others;

with HEX select

SEG<= "1111001" when "0001", --1

"0100100" when "0010", --2

"0110000" when "0011", --3

"0011001" when "0100", --4

"0010010" when "0101", --5

"0000010" when "0110", --6

"1111000" when "0111", --7

"0000000" when "1000", --8

"0010000" when "1001", --9

"0001000" when "1010", --A

"0000011" when "1011", --b

"1000110" when "1100", --C

"0100001" when "1101", --d

"0000110" when "1110", --E

"0001110" when "1111", --F

"1000000" when others; --0

Formation VHDL Vahid MEGHDADI

159

Exemple 7- CNA AD5541A

Pour que le CNA produise une tension analogique à partir d’une donnée de 16 bits, il faudra respecter le timing donné par le constructeur.

Remarque

Formation VHDL Vahid MEGHDADI

160

Exemple 7- AD5541A Timing Diagram

La donnée est à envoyée en série (MSB d’abord)

Générer une horloge à f=1/t1

Génération de CS

Génération de LDAC

DIN change sur le front

descendant de SCLK

Remarque

Formation VHDL Vahid MEGHDADI

161

Exemple 7- AD5541A contraintes de Timing

Fclk=25MHz

On fixe à 1/25MHz=40ns

Remarque

Formation VHDL Vahid MEGHDADI

162

Le but est de créer l’interface CNA pour simplifier le dialogue avec le CAN. Ainsi, pour dialoguer avec l’interface, on n’aura qu’un bus de 16 bits et un signal STRB (Strobe).

Exemple 7- Interface CNARemarque

Formation VHDL Vahid MEGHDADI

163

Exemple 7- Conception

Une machine à état

- État repos (CS<=‘0’; DIN <= ‘Z’; LDAC <= ‘1’);

- Dès qu’on détecte ‘1’ sur STRB

- on envoie ‘1’ sur CS

- État change en envoie

- On envoie les 16 bits de DATA un par un (MSB d’abord)

- 16 bits envoyés, on attend une période d’horloge (état tempo)

- Etat fin pour finaliser (LDAC <= ‘1’)

Remarque

Formation VHDL Vahid MEGHDADI

164

Exemple 7- Programmation un seul process

signal cmp : integer range 0 to 15;

signal reg : std_logic_vector (15 downto 0);

type T_etat is (repos, envoi, tempo, fin);

signal etat : T_etat := repos;

process(CLK)

begin

if CLK'event and CLK='0' then

case etat is

when repos =>

CS <= '1';

LDAC <= '1';

cmp <= 15;

DIN <= 'Z';

if STRB = '1' then

reg <= DATA;

etat <= envoi;

end if;

when envoi =>

CS <= '0';

DIN <= reg(cmp);

cmp <= cmp - 1;

if cmp = 0 then

etat <= tempo;

end if;

when tempo =>

DIN <= 'Z';

CS <= '1';

etat <= fin;

when others => -- etat = fin

LDAC <= ‘0';

cmp <= 15;

etat <= repos;

end case;

end if;

end process;

Remarque

Formation VHDL Vahid MEGHDADI

166

entity AD5541A isPort ( CLK : in STD_LOGIC;

DATA : in STD_LOGIC_VECTOR (15 downto 0);STRB : in STD_LOGIC;CS : out STD_LOGIC;DIN : out STD_LOGIC;LDAC : out STD_LOGIC;SCLK : out STD_LOGIC);

end AD5541A;

architecture Behavioral of AD5541A istype t_etat is (repos, e_cs, envoie, tempo, e_ldac);signal etat_cour, etat_futur : t_etat:= repos;signal count : integer range 0 to 31:=0;signal raz : std_logic;signal reg : std_logic_vector(15 downto 0);

Begin

SCLK <= not CLK;DIN <= reg(16-count) when etat_cour = envoie else 'Z';CS <= '1' when etat_cour = e_CS else '0';LDAC <= '0' when etat_cour=e_ldac else '1';

process(CLK)begin

if CLK'event and CLK='1' thenif STRB = '1' then

reg <= DATA;end if;

end if;end process;

process(CLK)begin

if CLK'event and CLK='1' thenetat_cour <= etat_futur;

end if;end process;

process(CLK)begin

if CLK'event and CLK='1' thenif raz = '1' then

count <= 0;else

count <= count + 1;end if;

end if;end process;

Exemple 7- ProgrammeRemarque

Formation VHDL Vahid MEGHDADI

167

process(etat_cour, count, STRB)begin

etat_futur <= etat_cour;raz <= '0';case etat_cour iswhen repos =>

raz <= '1';if STRB = '1' then

etat_futur <= e_cs;end if;

when e_cs =>if count = 0 then

etat_futur <= envoie;end if;

when envoie =>if count = 16 then

etat_futur <= tempo;end if;

when tempo =>if count = 17 then

etat_futur <= e_ldac;end if;

when others => -- e_ldacif count = 18 then

etat_futur <= repos;end if;

end case;end process;

end Behavioral;

Exemple 7- ProgrammeRemarque

Formation VHDL Vahid MEGHDADI

170

Attention !

Les instructions suivantes sont interdites dans une zone concurrente

Architecture x of y is

Begin

A <= not A;

CMPT <= CMPT + 1;

REG <= REG (0) & REG(7 downto 1);

…...

end x;

+1

Formation VHDL Vahid MEGHDADI

171

Correction

+1

D Q

CLK

D Q

CLK

On utilise un processsynchronisé sur un frontprocess (CLK)

begin

if rising_edge(CLK) then

A <= not A;

-- CMPT <= CMPT + 1;

-- etc;

end if;

end process;

Attention !Circuits séquentiels

Formation VHDL Vahid MEGHDADI

172

Process synchrones!

Dans un process synchrone il faut respecter un des deux canevas ci-dessous

process(CLK) uniquement CLK dans la liste de sensibilité

begin

if CLK’event and CLK=‘1’ then process ne contient qu’un grand if

-- suite d’instructions qui peut contenir d’autre if

end if; tout de suite après : end process

end process;

process(CLK, RST) CLK et le signal reset dans la liste de sensibilité

begin

if RST = ‘1’ then process ne contient qu’un grand if-else

-- suite d’instructions qui peut contenir d’autre if

elsif CLK’event and CLK=‘1’ then

-- suite d’instruction qui peut contenir d’autre if

end if; tout de suite après : end process

end process;

Formation VHDL Vahid MEGHDADI

173

Les sous-programmes

But des sous-programmes

•Pour écrire des algorithmes réutilisables

•Pour augmenter la lisibilité

Deux classes des sous-programmes

•Les procédures

•Les fonctions

Les sous-programmes

Formation VHDL Vahid MEGHDADI

174

•Mot clé procedure

•L'appel d'une procédure est une instruction concurrente ou séquentielle

•Peut retourner plusieurs valeurs

•Peut agir sur les signaux globaux

•Peut se synchroniser (avec wait dedans)

•Corps d'une procédure est une zone séquentielle

Procédure

Les sous-programmes

Formation VHDL Vahid MEGHDADI

175

Fonction

•Mot clé function

•L'appel est à droite d'une affectation

•L'appel peut se faire dans la zone concurrente ou séquentielle

•Retourne une seule valeur

•Rend immédiatement sa valeur

•Corps d'une fonction est une zone séquentielle

Les sous-programmes

Formation VHDL Vahid MEGHDADI

176

Ecriture des sous-programmes

Un sous-programme est constitué

•D'une déclaration : interface

•D'un corps : algorithme

Syntaxe de la déclaration

•procedure <nom> (liste des paramètre);

•function <nom> (liste des paramètre) return type_du_résultat;

Les sous-programmes

Formation VHDL Vahid MEGHDADI

177

Liste_des_paramètre :{classe_d'objet} PARAM1 :{mode} type{:=valeur_par_défaut}•class_d'objet : signal, variable, constant•mode : in, out, inout

Restriction

•pas de paramètres out ou inout dans la déclaration d'une fonction

•pas de variable transmise à une fonction

•classe d'objet par défaut est "constant" pour les "in" et "variable" pour les "out" et "inout"

Déclaration des sous-programmes

Les sous-programmes

Formation VHDL Vahid MEGHDADI

178

Corps de sous-programme

Entête is -- function ou procedure{zone de déclarations}

begin{partie instruction séquentielle}

end {nom_de_sous-programme}

Exemplefunction MIN (signal A,B : integer) return integer isbegin

if A < B then return Aelse return Bend if;

end MIN;

Les sous-programmes

Formation VHDL Vahid MEGHDADI

179

Appel de sous-programme

Différentes formes d'appel

•Par position (même ordre que la déclaration)

•RESULTAT <= MIN (SIG1, 5);

•Par nom (ordre non important)

•RESULTAT <= MIN (B=> 5, A=> SIG1);

•RESULTAT <= MIN (A=> SIG1, B=> 5);

Les sous-programmes

Formation VHDL Vahid MEGHDADI

180

-- HEX-to-seven-segment decoder

-- HEX: in STD_LOGIC_VECTOR (3 downto 0);

-- LED: out STD_LOGIC_VECTOR (6 downto 0);

--

-- segment encoding

-- 0

-- ---

-- 5 | | 1

-- --- <- 6

-- 4 | | 2

-- ---

-- 3

Exemple

Exemples

Formation VHDL Vahid MEGHDADI

181

with HEX selectLED<= "1111001" when "0001", --1

"0100100" when "0010", --2"0110000" when "0011", --3"0011001" when "0100", --4"0010010" when "0101", --5"0000010" when "0110", --6"1111000" when "0111", --7"0000000" when "1000", --8"0010000" when "1001", --9"0001000" when "1010", --A"0000011" when "1011", --b"1000110" when "1100", --C"0100001" when "1101", --d"0000110" when "1110", --E"0001110" when "1111", --F"1000000" when others; --0

Programmation concurrente

Exemples

Formation VHDL Vahid MEGHDADI

182

function DECODE (signal HEX: std_logic_vector(3 downto 0))return std_logic_vector(6 downto 0) isbegin

case HEX iswhen "0001" => return "1111001"; --1when "0010" => return "0100100"; --2when "0011" => return "0110000"; --3when "0100" => return "0011001"; --4when "0101" => return "0010010"; --5when "0110" => return "0000010"; --6when "0111" => return "1111000"; --7when "1000" => return "0000000"; --8when "1001" => return "0010000"; --9when "1010" => return "0001000"; --A

………...when others => return « 1000000"; -- 0end case;

end;

Utilisation de fonction

Exemples

Formation VHDL Vahid MEGHDADI

183

Paquetage

Il donne la possibilité de

•Regrouper des codes communs dans un travail en équipe

•Déclarer des types et des sous-types

•Déclarer des objets (signaux, constants)

•Déclarer des sous-programmes

•Déclarer des alias

Paquetage

Formation VHDL Vahid MEGHDADI

184

Syntaxe de Paquetage

Package <nom_de_paquetage> is

<suite de déclarations>

end {<nom_de_paquetage>};

Exemple:

package pak_test is

subtype OCTET is std_logic_vector(7 downto 0);subtype MOT is std_logic_vector(15 downto 0);

constant PAQUET_SIZE : integer := 11;

function INT_TO_7SEG (constant CHIFFRE : in std_logic_vector(3 downto 0)) return OCTET;

end pak_test;

Paquetage

Formation VHDL Vahid MEGHDADI

185

Paquetage de composants

Le paquetage permet aussi de grouper la déclaration d'un ensemble de composants.

Exemple :package STANDARD_CELL is

component INVERSEURport (E : in bit; S : out bit);end component;

component PORTE_OUport (A,B : in bit; S : out bit);end component;

….

end STANDARD CELL;

Paquetage

Formation VHDL Vahid MEGHDADI

186

Corps de Paquetage

Décrit l'algorithme des sous-programmes déclarés dans le package.

Syntaxe :package body <nom_de_paquetage> is

{corps de sous-programmes}

end <nom_de_paquetage>;

Paquetage

Formation VHDL Vahid MEGHDADI

187

package body pak_test is

function INT_TO_7SEG (constant CHIFFRE : in std_logic_vector(3 downto 0)) return OCTET is

variable SEG : std_logic_vector(7 downto 0);begin

case CHIFFRE iswhen "0001" => SEG := "01111001" ; --1when "0010" => SEG := "00100100" ; --2

…….when "1111" => SEG := "00001110" ; --Fwhen others => SEG := "01000000" ; --0

end case;return SEG;

end INT_TO_7SEG;

end pak_test;

Exemple de Corps de Paquetage

Paquetage

Formation VHDL Vahid MEGHDADI

188

Utilisation de paquetage

•On crée d'abord une librairie

•Sous ISE, new source --> VHDL library

•Ecrire le paquetage et son corps

•Ajouter à la librairie que l'on souhaite

•Sous ISE, sélectionner le fichier et ensuite--> move to library

•Dans le programme utilisant cette librairie :library <mon_lib>use <mon_lib>.<mon_paquetage>

Paquetage

Formation VHDL Vahid MEGHDADI

189

Configuration

Une entité peut avoir plusieurs architectures

Un rôle de configuration : choisir l'architecture correspondante

Exemple : Pour l'entité additionneur on peut envisager 3 architectures différentes : A, B et C

ADDITIONNEUR(A)ADDITIONNEUR(B)ADDITIONNEUR(C)

A chaque instanciation de l'entité, un seul couple entité/architecture peut être compilé.

Configuration

Formation VHDL Vahid MEGHDADI

190

Deux façons pour relier une architecture précise à une entité :

•Dans une unité de compilation autonome : la configuration

•Dans la partie déclarative d'un bloc ou d'une architecture (configuration "à la volée")

(Par défaut c'est la dernière compilée qui sera prise en compte)

Choix de l'architecture

Configuration

Formation VHDL Vahid MEGHDADI

191

Exemple de Configuration

Entity SIM is end;

architecture ESSAI1 of SIM iscomponent ADD

port (A,B : in integer;S : out integer);

end component;

signal X,Y,SUM : integer;

beginINST1 : ADD port map (X,Y,SUM);

X <= 12, 55 after 100 ns;Y <= 0, 100 after 200 ns;

end ESSAI1;

configuration CONF of SIM is

for ESSAI1for INST1 : ADD

use entity work.ADD(FONCTION)end for;

end for;

end CONF;

Entity ADD isport (A,B : in integer;

S : out integer);end ADD;

architecture FONCTION of ADD isbegin

S <= A+B;end FONCTION;

Configuration

Formation VHDL Vahid MEGHDADI

192

Exemple de Configuration "à la volée"

Entity ADD isport (A,B : in integer;

S : out integer);end ADD;

architecture FONCTION of ADD isbegin

S <= A+B;end FONCTION;

Entity SIM is end;

architecture ESSAI1 of SIM iscomponent ADD

port (A,B : in integer;S : out integer);

end component;for all : ADD

use entity work.ADD(FONCTION);-- ou-- for INST2 : ADD-- use entity work.ADD(FONCTION);

signal X,Y,SUM : integer;

beginINST2 : ADD port map (X,Y,SUM);

X <= 12, 55 after 100 ns;Y <= 0, 100 after 200 ns;

end ESSAI1;

Configuration

Formation VHDL Vahid MEGHDADI

193

•Attribut sur les signaux:•signal_name'attribut•l'attribut synthétisable : event•If CLK'event and CLK='1' then …

•attribut sur le type array•type MYARR is array (-2 to 4) of integer;•MYARR’left returns -2•MYARR’right 4•MYARR’high 4•MYARR'low -2•MYARR’reverse_range 4 downto to -2

Les Attributs

Les Attributs

Formation VHDL Vahid MEGHDADI

194

Alias

Intérêt•Donne un nom différent (plus lisible) à un objet

•l'ancien nom reste utilisableSyntaxe

•alias nouveau_nom : type_ou_sous_type is ancien_nom

Exemple

variable V32 : std_logic_vector (0 to 31);

alias P_8 : std_logic_vector (0 to 7) is V32(0 to 7);alias D_8 : std_logic_vector (0 to 7) is V32(24 to 31);alias SIGNE : std_logic is V32(0);. . .SIGNE := '1'; -- identique que V32(0) <= ‘1’;

Alias

Formation VHDL Vahid MEGHDADI

195

Encodage d'état dans une machine à état

•Encodage d'états peut se faire manuellement :

type t_etat is (S1, S2, S3, S4, S5);-- encodage binaireattribute enum_code : string;attribute enum_code of t_etat : type is "000 001 010 011 100";-- S1 est codé en "000", S2 en "001", S3 en "011" et …signal etat : t_etat;

•On peut laisser le compilateur choisir le codagetype t_etat is (S1, S2, S3, S4, S5);signal etat : t_etat;

Encodage d'état dans une machine à état

Formation VHDL Vahid MEGHDADI

196

Codage one-hot

La méthode préférée pour les circuits énormes est le codage one-hot

type t_etat is (S1, S2, S3, S4, S5);-- encodage binaireattribute enum_code : string;attribute enum_code of t_etat : type is "00001 00010 00100 01000 10000";-- S1 est codé en "00001", S2 en "00010", S3 en "00100" et …signal etat : t_etat;

Remarque:

Ne pas oublier d'initialiser l'état avec un signal RESET

Encodage d'état dans une machine à état

Formation VHDL Vahid MEGHDADI

197

BIT0 : FULL_ADD port map (X(0) , Y(0) , ’0’ , Z(0) , C(0));BIT1 : FULL_ADD port map (X(1) , Y(1) , C(0) , Z(1) , C(1));….BIT7 : FULL_ADD port map (X(7) , Y(7) , C(6) , Z(7) , C(7));

for Generate

for-generate (à utiliser dans la zone concurrente) permet de répéter un circuit plusieurs fois.

Exemple :

LABEL : for i in 1 to 7 generate

ADDITION : FULL_ADD port map (X(i), Y(i), C(i-1), Z(i), C(i);

end generate

BIT0: FULL_ADD port map (X(0) , Y(0) , ’0’ , Z(0) , C(0));

For generate

Formation VHDL Vahid MEGHDADI

198

Généricité

C’est un moyen de transmettre des infos à un component pour le rendre paramétrable.

Exemples : une porte ET à N entrées, un registre à décalage de taille N, un multiplexeur N vers 1, …

Syntaxe : generic (param1 : type de param1 := valeur par défaut;

param2 : type de param2 := valeur par défaut;...);

Généricité

Formation VHDL Vahid MEGHDADI

199

Exemple

Porte ET à N entrées :entity PORTE_ET is

generic(N : integer := 2);port(ENTREE : in std_logic_vector(1 to N);

SORTIE : out std_logic);end entity;…process (ENTREE)

variable V : std_logic;begin

V := '1';for I in 1 to N loop

V := V and ENTREE(I);end loop;SORTIE <= V;

end process;

Généricité

Formation VHDL Vahid MEGHDADI

200

Appel d’un bloc paramétrable

component PORTE_ETgeneric(N :integer := 2);port(ENTREES : in std_logic_vector(1 to N);

SORTIE : out std_logic);end component;…architecture A of B isbegin

INST : PORTE_ET generic map(N => 5)port map(ENTREES => A,

SORTIE => Z);…end A;

Généricité

Formation VHDL Vahid MEGHDADI

201

If Generate

If-generate permet de synthétiser un circuit suivant une condition

Exemple :

architecture A of generate_test issignal clk_r : std_logic:= '1';beginU1: if CLK_DIV generate

process(CLK)begin

if CLK'event and CLK='1' thenclk_r <= not clk_r;

end if; end process;

end generate;

U2: if not CLK_DIV generate clk_r <= clk;end generate;

sortie <= clk_r;

end A;

entity generate_test isgeneric ( CLK_DIV : boolean :=TRUE);Port ( CLK : in std_logic;

sortie : out std_logic);end generate_test;

If generate

Formation VHDL Vahid MEGHDADI

202

Conseils de synthèse

•Utiliser le nom du fichier le même que le nom de l'entité

•Ne pas mettre plus d'un couple entity/architecture dans un fichier

•Les noms des signaux peuvent être jusqu'à 256 caractères. Ne pas hésiter à donner un nom signifiant à des signaux (constantes, variables, types, etc)

•Quand vous appelez un component, utilisez les paramètres de passage par nom :

•U1 : HALF_ADD port map(A =>oper1, B=>oper2, SUM =>somme, C=>retenue);

Conseils de synthèse

Formation VHDL Vahid MEGHDADI

203

Conseils (2)

•Ne jamais utiliser des signaux ou des variables pour des constantes (cela gaspille les ressources énormément),