Counters - University of Texas at...

Transcript of Counters - University of Texas at...

Counters (Class 8.2 – 10/18/12)

CSE 2441 – Introduction to Digital Logic

Fall 2012

Instructor – Bill Carroll, Professor of CSE

Today’s Topics

• Counters

– Generic devices

– Standard 7400-series devices

– Ring counters

– Twisted-ring (Johnson) counters

• Preview of Laboratory 6

Introduction to Counters

• Counters – sequential circuits that tally, or count, in a predetermined code sequence, the number of input pulses received, e.g., 3-bit binary counter.

y2y1y0

Recall How A JK Flip-flop Works

Synchronous Binary Counter

CLR

J

CK

Q

Q

CK

K

CLR

J

CK

Q

KQ

CLR

J

CK

Q

KQ

CLR

J

CK

Q

KQ

...

...

...

Overflow

Xn

X1

X2

X3

Clear

Count

Inhibit(a)

(b)

00000

00001

00110

01010

11001

11000

11000

1

01010

Xn

X1

X2

X3

Recycles

X4 X3 X2 X1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

Figure 7.11

SN74163 Synchronous Binary Counter

Synchronous clearSynchronous load

CountHoldHold

Load

Data A

Data B

Data C

Data D

(a)

(b)

(9)

(3)

(4)

(2)

(5)

(6)

(1)

(7)

Clock

ENP

ENT

Inputs

Mode

(10)

QAJ

K

LHHHH

´LHHH

´´HL´

´´H´L

Q

CK

(14)

QBJ

K

Q

CK

(13)

QCJ

K

Q

CK

(12)

RCO

J

K

Q

CK

(15)

QD(11)

Clear

Load ENPENTClear

Figure 7.12

SN74163 Timing Diagram

(c)

Clear

Load

Outputs

A

B

C

D

Clock

ENP

ENT

RCO

QA

QB

QC

QD

Syncclear

Syncload

Datainputs

12 13 14 15 0 1 2

Count Inhibit

Figure 7.12, con’t

Asynchronous Down Counter

CLR

J

CK

Q

Q

CK

K

CLR

J

CK

Q

KQ

CLR

J

CK

Q

KQ

...

...

...

Xn X1X2

Clear

(a)

(b)

1

0

0

0

0

0

1

0

0

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

...

...

...

...

...

...

Xn X1X2X3...

Clock

Count

0

1

1

1

1

1

0

1

1

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

...

...

...

...

...

...

Xn X1X2X3...

Up count mode Down count mode

Figure 7.16

Synchronous Up/Down Counter

CLR

J

CK

Q

Q

CK

K

...

Xn

Upoverflow

Downoverflow

CLR

J

CK

Q

Q

CK

K

X2

...

...

...

...

...

CLR

J

CK

Q

Q

CK

K

X1

Up/down

Clock

Clear

1

Figure 7.17

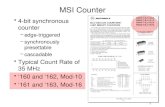

Modulo-N Counters – Counters that count from 0 to N-1 and repeat

• SN74160 Synchronous Decade Counter – counts 0 to 9

M1

Clear

D

VCC

QA

QB

QC

QD

Load

ENT

A

B

ENP

GND

(a)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

(1)

(9)

(10)

(7)

(2)

(3)

(4)

(5)

(6)

(b)

(14)

(13)

(12)

(11)

(1)

(2)

(4)

(8)

(15)

Clock

C

RCO

Clear

D

A

B

ENP

Load

C

Clock

ENT

QA

QB

QC

QD

RCO3CT = 9M2

CT = 0

G4

G5/2,3,4+

G3

CTRDIV 10

'160

1,5D

SN74160 Logic Diagram

Load

Data A

Data B

Data C

Data D

(c)

(9)

(3)

(4)

(2)

(5)

(6)

(1)

(7)

Clock

ENP

ENT(10)

QAJ

K

Q

CK

(14)

QBJ

K

Q

CK

(13)

QCJ

K

Q

CK

(12)

RCO

J

K

Q

CK

(15)

QD(11)

Clear

CLR

CLR

CLR

CLRQ

SN74160 Timing Diagram

(d)

Clear

Load

Outputs

A

B

C

D

Clock

ENP

ENT

RCO

QA

QB

QC

QD

Asyncclear

Syncload

Datainputs

7 8 9 0 1 2 3

Count Inhibit

Digital Timer Block Diagram

Minutes Seconds

Clear

1 Pulse/hour 1 Pulse/minute

1 Pulse/second

Power line

Start/Stop

¸

6

¸

10

¸

6

¸

10

¸

5

¸

12

Pulsegenerator

Figure 7.22

Modulo-N Asynchronous Counter

J

CK

Q

Q

Xn- 1

CK

K

R

J

CK

Q

KQ

X0

Clearcontrol

Countpulse

Countcontrol

J

CK

Q

KQ

X1

S

R

S

R

S

State detectionlogic

Recall D Flip Flop Functionality

Ring Counters

Twisted-Ring (Johnson) Counter

Four-Bit Shift Register Example

D

C

S

R

Q

Q

D

C

S

R

Q

Q

D

C

S

R

Q

Q

D

C

S

R

Q

Q

+5V

O3

IN

SHIFT

CLEAR

O2O1 O4

SHIFT t0 t1 t2 t3 t4 t5 t6 t7 t8

IN 1 1 1 1 0 0 0 0 0

O1 0 1 1 1 1 0 0 0 0

O2 0 0 1 1 1 1 0 0 0

O3 0 0 0 1 1 1 1 0 0

O4 0 0 0 0 1 1 1 1 0

Four-Bit Ring Counter Example

SHIFT t0 t1 t2 t3 t4 t5 t6 t7 t8

O1 1 0 0 0 1 0 0 0 1

O2 0 1 0 0 0 1 0 0 0

O3 0 0 1 0 0 0 1 0 0

O4 0 0 0 1 0 0 0 1 0

Four-Bit Twisted-Ring Counter

SHIFT t0 t1 t2 t3 t4 t5 t6 t7 t8

IN 1 1 1 1 0 0 0 0 1

O1 0 1 1 1 1 0 0 0 0

O2 0 0 1 1 1 1 0 0 0

O3 0 0 0 1 1 1 1 0 0

O4 0 0 0 0 1 1 1 1 0

Preview of Lab 7

• Study flip-flops – SN7474, SN7476

• Implement a basic shift register using SN7474s

• Use the shift register to implement a twisted-ring counter