Coaxial Through-Package-Vias (TPVs) for Enhancing Power Integrity … · 2018-08-13 · Coaxial...

Transcript of Coaxial Through-Package-Vias (TPVs) for Enhancing Power Integrity … · 2018-08-13 · Coaxial...

Coaxial Through-Package-Vias (TPVs) for Enhancing Power Integrity in 3D Double-side Glass Interposers

Gokul Kumar, P. Markondeya Raj , Jounghyun Cho *, Saumya Gand hi, Parthasarathi Chakraborti, Venky Sundaram,

Joungho Kim* and Rao Tummala

3D Systems Packaging Research Center, Georgia Institute of Technology

* Terahertz Laboratory, KAIST, Daejeon, South Korea

Email: [email protected]

ABSTRACT

Double-sided 3D glass interposers and packages, with

through package vias (TPV) at the same pitch as TSVs in Si,

have been proposed to achieve high bandwidth between logic

and memory with benefits in cost, process complexity,

testability and thermal over 3D IC stacks with TSV. However,

such a 3D interposer introduces power distribution network

(PDN) challenges due to increased power delivery path length

and plane resonances. This paper investigates the use of coaxial

through-package-vias (TPVs) with high dielectric constant

liners as an effective method to deliver clean power within a

3D glass package, and provides design and fabrication

guidelines to achieve the PDN target impedance. The Coaxial

TPV structure is simulated using electromagnetic (EM) solvers

and a simplified equivalent circuit model to study via

impedance and parasitics. Test vehicles with anodized tantalum

oxide capacitors were fabricated in ultra-thin, 100µm thick

glass interposers to demonstrate process feasibility, with a

capacitance density of 5 nF/mm2. Self-impedance (Z11) of a

3D glass interposer containing the coaxial TPVs was analyzed

with variations in (a) Via location, (b) Number of coaxial vias,

and (c) Via capacitance and stack-up, to provide optimal PDN

design guidelines. Based on the above parameters, the added

decoupling vias achieved more than 30% impedance

suppression over multiple resonance frequencies between 0.5-

6 GHz, providing an effective and flexible PDN design method

for double-side 3D glass interposers.

I. INTRODUCTION

Logic and memory stacking with through silicon vias

(TSV) to form 3D ICs, with much higher interconnect density

than the current package-on-package (PoP) stacking, has been

proposed and is being developed to meet ultra-high bandwidth

(25-100GB/s) demands of smart mobile systems with lower

power consumption and miniaturization. However, the

adoption of these 3D ICs has been delayed by many challenges

that include thermal issues, testability and high cost. A simpler

approach to achieve this high bandwidth using ultra-thin 3D

glass packages has been proposed and fabricated by Georgia

Tech [1] [2], which results in elimination of complex and costly

TSVs in the logic die, as shown in Figure 1. Such a 3D glass

approach uses an ultra-thin, 30-50µm glass interposer with

stacked memory on one side and logic IC on the other side,

interconnected by through package vias (TPVs) at the same

pitch as TSVs in Si, and SMT mounted onto the printed wiring

board (PWB) through solder ball interconnections [3]. While

this technology offers cost, testability and thermal advantages

over 3D IC stacking, it introduces a new challenge in power

delivery, directly attributable to the long PDN path through

lateral power-ground (P/G) planes. In addition, multi-mode

plane resonances in glass interposers, that are common to high-

resistivity substrates including organic packages, require

careful PDN design.

Figure 1 : Approaches for high bandwidth 3D-integration

Figure 2 : 3D Glass interposer PDN with coaxial Vias as

distributed decoupling capacitors

This paper, for the first time, integrates high-dielectric

constant materials into TPVs in ultra-thin glass interposers to

improve the PDN performance of double sided 3D interposers,

and the techniques presented here can also be applied to single-

chip 2D packages and multi-chip 2.5D interposers. Figure 2

illustrates the major power delivery challenges in 3D glass

interposers and the proposed structure with coaxial TPVs to

address some of these challenges. The coaxial TPVs with high

dielectric constant thin films between the power and ground via

conductors form ultra-miniaturized decoupling capacitors

along the package power path. This distributed capacitance,

placed very close to the active die, acts as charge reservoirs and

presents an improved power delivery solution without ESL

limitations or additional space requirements.

The authors previously reported the PDN characteristics of

3D double-side interposers with reduced power/ground ball

Glass interposer

PCB

Logic

Memory

Memory

Memory

Memory

BGA

TSV

TPVSilicon Interposer or Org. Pkg

PCB

Logic

Memory

Memory

Memory

Memory

BGA

TSV

3D Glass Interposers with TPVs3D ICs with TSVs

Memory Stack

PCB

LogicP/G BGA

Distributed

Coaxial P/G

TPVs as Decap

P/G

planes

Lateral

PDN Path

978-1-4799-2407-3/14/$31.00 ©2014 IEEE 541 2014 Electronic Components & Technology Conference

grid arrays (BGAs) due to the placement of logic die at the

bottom of the substrate [4]. The effects of noise coupling

between signal nets and power/ground planes at resonant

frequencies , including the impact of signal return path

discontinuity were studied [5]. Recent literature compared the

effects of simultaneous switching noise and signal

discontinuity in silicon and glass interposers using M-FDM

methods [6, 7]. Embedded and die-integrated decoupling

schemes have been proposed with glass and silicon interposers

to improve their power delivery profile [8-10]. Recent studies

employed three-dimensional P/G coaxial vias (TSVs) in 3DIC

stacks for added coupling capacitance [11]. However, effect of

via placement and physical geometry in the power and signal

integrity of double-sided flip-chip interposers has not been

investigated. This paper goes beyond published literature to

present a detailed study of the PDN impedance profile in 3D

glass interposers including the effects of via interconnection

capacitances. In addition, it explores and demonstrates the use

of coaxial through-package-vias as an effective design

technique to improve power delivery networks.

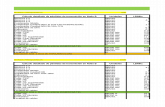

Table 1: 3D interposer system dimensions

Following this introduction, Section II describes the

modeling and design of coaxial vias. Parasitics for different

technologies are examined and extracted using full-wave

electromagnetic (EM) solvers, forming building blocks for the

subsequent analysis. An equivalent circuit model is proposed

to identify the key parameters contributing to the capacitance,

and the results are tabulated. Section III deals with a discussion

of various dielectric options, selection of the front-up materials,

and an initial process demonstration for the TPV with

capacitors in 3D glass interposers. Section IV studies the

benefit of the proposed coaxial vias to address PDN challenge

by modeling the PDN response with and without decoupling

vias from the previous sections. Based on this investigation,

design guidelines for an optimal P/G TPV physical design and

dimensions are provided. Section V summarizes the results

from this study.

II. ELECTRICAL DESIGN OF COAXIAL THROUGH

PACKAGE VIAS

This section examines via parasitics for different coaxial

TPV process methods and stack-up technologies, and presents

a simplified circuit model to analyze coaxial via interconnects.

The parasitic properties of the coaxial vias that are most critical

for PDN design, including the inductance, capacitance and total

via impedance are analyzed first. Both analytical equations and

an electromagnetic solver (Q3D) is used for this study for

parametric analysis. Since the overall resistance of thick

coaxial vias are extremely small, they are not focused in this

section. Integration of high-k thinfilm materials such as

tantalum oxide and barium titanate between the inner conductor

and outer shell of coaxial TPVs in an ultra-thin glass substrate

is studied provide up to 50x higher via decoupling capacitance.

Figure 3 shows the electrical block diagram of the 3D

interposer PDN including coaxial TPVs.

Figure 3: Schematic Diagram of 3D interposer PDN

Figure 4: Co-axial Via Dimensions considered in this

Study - 40nm tantalum oxide liner with (a) 30m Glass

thickness (b) 100m thickness, 15m polymer liner with (c)

30m glass thickness

Table 2: Summary of coaxial via capacitance

Liner

material 𝜀

Glass

Thickness

(µm)

Theoretical

Value (pF)

Q3D (pF)

Tantalum

Oxide 25

30 12.4 12.7

100 117 120

Polymer 3.01 30 0.0117 0.018

Table 3: Summary of coaxial via loop inductance

Glass

Thickness

(µm)

Outer

Radius

(µm)

Inner

Radius

(µm)

Theoretical

Value (pH)

Q3D

(pH)

30 10 9.96 0.028 0.022

100 25 24.96 0.042 0.032

30

(polymer) 25 15 3.63 4.7

Considering current technology and future miniaturization,

three coaxial TPV physical configurations are chosen as shown

in Figure 4. Two variations of total TPV height (71 µm and 180

µm) in ultra-thin glass substrates (including dielectric and glass

sections) is considered with both moderate-K(Tantalum oxide)

and polymer liner configurations. The target metallization

thickness was defined to be 5 µm.

VRM

PCB Traces

Board Decap

On-Chip

Mesh PCB

P/G Planes

PCB Vias

Interposer

P/G Planes

BGA Balls

PackageDecap

Embedded

Decap

Lateral Trace Length C4

Package P/GTrace

Length

Coaxial Cap

Load

On-chip Decap

71µm

30µm

3µm

30 µm

60µm

17.5µm

3µm

17.5µm

Poly

mer 1

0 µ

m

(c)

180µm

100µm

17.5 µm

49.92µm

60µm

22.5µm

17.5µm

22.5µm

Tanta

lum

40 n

m

(b)

71µm

30µm

3µm

19.92µm

30µm

17.5µm

3µm

17.5µm

Tanta

lum

40 n

m

(a)

Polymer

Glass

Polymer

Coaxial TPV Diameter 30-60 µm

Tantalum Liner Thickness 40nm

Ultra-thin Core Thickness 30-100µm

Interposer/Package size 17mm x17mm

PWB size 25mm x25mm

BGA pitch 400 µm

542

From literature, simplified analytical expressions for

capacitance and loop inductance per unit length of a coaxial via

can be given as

𝐶𝐿 =2𝜋𝜀0𝜀𝑟

𝑙𝑛(𝐷

𝑑)

F/m

𝐿𝐿 =μ

2π ln(𝐷/𝑑) H/m

𝐷 is the outer via radius

𝑑 is the radius of the inner via

𝜀0 ,𝜀𝑟 is the permittivity of free space and TPV liner

µ is the permeability

Table 2 presents a summary of various capacitance values

that are extracted for coaxial vias. As expected, it can be seen

that the maximum value of capacitance is achieved with the

100m glass via having the tantalum liner due to the highest

capacitance density and surface area. Table 3 details the loop

inductance of coaxial TPVs. It can be seen that the loop

inductance of the p/g via is extremely small due to the thin

coaxial liner, when compared with the loop inductance of a

polymer based coaxial TPV. These results indicate useful PDN

applications with the proposed P/G TPV configurations. Based

on the extracted values, a simplified equivalent circuit model

for glass TPVs was constructed as shown in Figure 5. It can be

seen that the dominant capacitance is from the thin high-K liner

material that is separated by the power and ground conductors,

and has a theoretical value in several tens of pico farads.

Figure 5: Circuit model for Coaxial P/G Glass TPVs

The impedance profile between the power and ground vias

of a single coaxial TPV from different configurations was

simulated using a full wave EM solver (HFSS) as shown in

Figure 6. The self-impedance is measured between via pads of

the top two metal layers as shown. It was seen that lowest

impedance was observed with 100µm coaxial TPV due to its

large surface area and length of the capacitor, followed by the

ultra-thin 30 µm TPV. The impedance of polymer based

coaxial vias were several orders higher than the other

configurations, with smaller capacitive values due to larger

separation between the metal plates. The effective capacitance

of coaxial vias can be increased by connecting a number of the

coaxial P/G vias in parallel, similar to the configuration present

in interposer applications. The higher capacitance vias exhibit

decoupling at lower frequencies, enabling selective tuning to

meet target impedance.

Figure 6: Self-Impedance profile of single P/G coaxial via

III. POWER-GROUND TPV: MATERIALS AND

PROCESSES

3D interposers need to support low impedance power-

ground coaxial TPVs for efficient power supply. Based on the

simulations shown in the previous section, the power-ground

needs a capacitance in the order of 50-100 pF per via. This

section deals with a discussion on various dielectric options,

selection of the front-up materials, and an initial process

demonstration for the TPV capacitors in 3D glass interposers.

Table 4: Dielectric options for TPV capacitors in 3D

interposers, and their merits and demerits

Dielectrics Film properties

Merits Demerits

Oxides

Oxynitrides 7

t = 20 nm

2.5 nF/mm2

High BDV

allows 30 nm films

Standard

semiconduct

or tools

Expensive

semiconductor tools,

Lower capacitance densities;

Moderate K

paraelectrics

-Tantalum

oxide

t = 40 nm

5 nF/mm2

Simpler

processing

compared to high K films

Moderate

capacitance densities

High K super

paraelectrics

- BST

t = 150 nm

15-20 nF/mm2

Dielectric

constant low

but stable with lower

loss

Conformal dielectric

is a challenge with

standard processes

High K ferroelectrics

- Barium

titanate

t = 1 µm

30 nF/mm2

High density Higher temperature processing,

Lower reliability and

leakage,

Conformal dielectric

is a challenge with standard processes

Dielectric options

Low k films: In silicon trench and TSV capacitors, oxides,

nitrides and oxynitrides of silicon with permittivies of 5-7 are

widely used. The Breakdown Voltages (BDVs) of these films

range from 0.8-1 V/nm which represent the highest BDV of all

materials. Even a 20 nm film can stand voltage of 15 V.

ROuter

LOuter

GDielectric

CDielectric

GLiner

CLiner

GDielectric

CDielectric

RInner

LInner

Power

Top

Ground

Top

Power

Bottom

Ground

Bottom

Frequency (Hz)

Mag

(Z

11)

(c) 25µm Polymer

TPV

(b) 100µm TPV

(a) 30µm TPV

P

G

543

Furthermore, these materials present minimal reliability

concerns because of their intrinsic structure and properties.

This leads to a planar capacitance density of about 2-3 nF/mm2.

Moreover, these technologies are dependent on very standard

front-end semiconductor tools such as Plasma Enhanced

Chemical Vapor Deposition (PECVD), Liquid Phase Chemical

Vapor Deposition (LPCVD). The deposition temperatures are

less than 300 C, and no issues of adhesion and

thermomechanical compatibility arise because of their strong

covalent bonding to the electrode and good CTE match with

glass. However, higher capacitance densities with low-cost

panel processes are sought for 3D glass interposers.

Moderate k films: Oxides of tantalum, hafnium, zirconia,

titania etc. show permittivities of 15-80. Some of these have

breakdown strengths of 500-800 V/micron. They can be

deposited thinner down to 30-50 nm showing capacitance

densities approaching 5-10 nF/mm2. Moderate k films

represent 2-3 X improvement in capacitance density compared

to traditional oxides and nitrides. The most common technique

for depositing these thin films in trenches is Atomic Layer

Deposition (ALD), which also has cost and through-put

limitations.

High k films: Ferroelectrics show permittivities of 1000-

5000 in 1-3 micron thickness, with a capacitance density of

about 30 nF/mm2. Films with these properties require

extremely high temperature processes (~1000 oC). The

permittivity reduces dramatically for thinner films, and

therefore the capacitance density does not improve much. With

glass TPV-compatible processes (<650 oC), using lead-free

dielectrics, films in thicknesses of 100-200 nm and

permittivities of 200-300 are feasible. The capacitance density

is less than 15-20 nF/mm2 with these systems. However,

limitations of high-k film technologies arise from several

reasons:

• Non-conformal deposition processes such as

sputtering. Standard processes result in non-uniform

dielectric thickness as shown in Figure 7a and 7b.

• Higher temperature for crystallization

• Lower BDV requiring thicker films

• Thickness-dependent permittivity which results in

diminishing returns of capacitance density with

thickness reduction

• Intrinsic reliability issues from lattice defects and

interfaces

The capacitance densities achieved with various TPV

dielectrics are compiled in Table 4. Based on this summary,

anodized dielectrics provide the best combination of

capacitance density, process-compatibility with glass, and

scalability to large panels. Hence, anodized tantalum oxide

TPV capacitors are chosen as the front-up option to be

demonstrated.

TPV Capacitor Process:

Silicon trenches and vias are formed from dry-etching

processes using inductive-coupled plasma with fluorine gas,

which then diffuses to the low-pressure etching chamber,

where silicon is directionally etched. The most common

etching is done with Bosch process. In the Bosch process,

sidewall passivation with a polymer is utilized to prevent lateral

etching and give directionality to the etching process.

Figure 7: Sputtered dielectrics with non-uniform thickness (a),

cross-section of sputtered barium titanate (b). Sputtered metal

with conformal and uniform anodized films (c) and cross-

section of anodized tantalum oxide with uniform dielectric

thickness (d).

Figure 8: Leakage current with anodized tantalum dielectrics.

Figure 9: Schematic of fabricated coaxial via in glass

interposers

(a) (b)

(c) (d)

Copper (Top electrode)

Tantalum oxide

dielectric

Glass

Ta/Cu/Ta

544

For the glass TPVs, GT-PRC and its partners have

demonstrated excimer laser-based via formation process with

much lower cost, followed by electroless or sputtered copper

metallization. The process can achieve aspect ratios of 5-10.

To form tantalum oxide dielectrics in TPVs, tantalum is

sputtered with a DC-magnetron. A pressure of 6 mtorr and

power of 350 W is used in the current work, to yield a

sputtering rate of 1-2 A/sec. The coverage with tantalum can be

further improved with an inductively-coupled power supply.

The tantalum film is subsequently anodized in citric acid to

form conformal tantalum oxide films, as shown in Figure 7c

and 7d. The resulting film has a dielectric constant of 21-28.

For anodization at 8 V in potentiostatic mode, this yields a

conformal dielectric of about 30-35 nm, with a capacitance

density of 5-6 nF/mm2. The capacitance densities, though not

as high as that for ferroelectric films, are stable at GHz

frequencies due to paraelectric behavior and can effectively

address broadband decoupling needs. The films show a low

leakage current of 3-5 nA/cm2 at the typical operating voltage

of 2-3 V as shown in Figure 8. A cross-section of the TPV

structure is shown in Figure 9. The top electrode is sputtered

and subtractive-patterned to yield the TPV capacitor test-

structures as shown by the process test-vehicle in Figure 10.

Figure 10: Top View of the fabricated sample

IV. PDN IMPEDANCE ANALYSIS FOR 3D GLASS

INTEROSERS

This section describes the benefits of the proposed coaxial

vias for PDN applications, by modeling the PDN response with

and without decoupling vias from previous sections.

Figure 11: Flow Chart for the segmented PDN approach

Figure 12: PDN Port Locations

System PDN Impedance Modeling

The simulated system configuration consists of a four-metal

layer glass interposer with dimensions as shown in Table 1.

Since modeling the entire PDN including vias and PWB

interconnects is challenging due to simulation time, a

combination of segments from full-wave simulations and spice

integration is used to perform PDN system analysis. This

method, described in detail in [4] and figure 11, was used to

compute the total PDN impedance profile in frequency domain,

through integration of distributed ports across the package and

PWB planes. The PDN impedance of individual package and

PWB planes is modeled using a 3D EM solver (HFSS). The

multi-port P/G plane impedance models are then integrated

with BGA and via lumped parasitics at appropriate ports

depending on the configuration. Figure 12 presents numbered

port locations for BGA and coaxial via group net placement. In

this PDN study, the interposer is considered to be always

connected to the PWB through BGAs and Vias, in order to

model the impact of TPVs and BGA variations. The

assumptions for BGA placement in this study are the same as

[4] and table 6, and the vias are placed from ports 1-20 on both

the interposer and PWB, with the impedance profile studied at

port 19 of the interposer.

Table 5: Dielectric properties of substrate materials

Material Dielectric

Constant, 𝜀@

1MHz

Loss

tangent, tan δ

Borosilicate Glass 5.3 0.004

Polymer Laminate 3.01 0.005

Tantalum oxide 25 0.001

Table 6: BGA Port Configuration

Configuration

No. of

P/G

BGAs

PKG to

PWB port

connections

L(pH) /port

Full BGA array 700 1-16 7.69

3D Interposer 300 1-12 4.7

Cu electrode to access power via

545

PDN impact due to 3D interposers

Previously [4], it was shown that the loop inductance for

this double-side 3D interposer-package was trace-dominated

and the reduction of interposer P/G BGAs due to the bottom

die placement had minimal impact on the system PDN self-

impedance at low frequencies. Figure 13 shows the PDN

profile comparison between glass interposers with fully

populated BGA arrays and centrally depopulated BGA’s with

reduced second level P/G interconnections to represent the 3D

interposer configuration. The 3D interposer PDN generates

high frequency (8-10 GHz) impedance peaks from to parallel

resonance modes. This phenomenon is proposed to occur due

to multi-mode coupling between the additional lateral plane

inductance on the interposer package and the package

capacitance.

PDN impact due to Decoupling Coaxial Vias

A comparison of the PDN profile before and after the

addition of decoupling vias is presented in Figure 14. For the

purpose of this study, and based on the analysis from section II,

decoupling vias with a capacitance of 30pF/via are considered.

Based on the system configuration, 2000 of these coaxial vias

are assumed to be present in parallel, as a part of the interposer

PDN. Both the full-array interposer and 3D interposer PDN

have shifted series resonances occurring at 100 MHz due to the

series coupling between the decoupling capacitance and the

plane capacitance. The addition of decoupling vias completely

suppresses the 3D interposer resonances around 10 GHz and

shifts the resonance to lower frequencies, presenting a clear

benefit in power delivery design.

PDN impact due to Decoupling Coaxial Vias Configuration

Figure 15 presents the comparison of the PDN profile based

on the variation of decoupling vias distribution on the 3D

interposer. For the purpose of this study, we consider three

types of arrangements based on the coaxial via distribution; (a)

uniform distribution across the entire P/G plane, (b) Staggered

distribution at the center and periphery, and (c) coaxial vias on

the periphery only. All the three cases have the same amount of

decoupling vias (2000), but are only different in their

distribution as shown in table 7. It can be seen that the uniform

distribution presents the lowest impedance profile, followed by

staggered and peripheral configurations. This is due to the

minimization of loop inductances due to localized capacitance

action.

Table 7: Coaxial Via Port Configuration

Via Distribution PKG to PWB

port connections

Uniform 1-20

Staggered 1-16

Peripheral 1-12

PDN impact due to Decoupling Coaxial via Capacitance

Figure 16 presents the comparison of the PDN profile based

on the variation of decoupling vias capacitance on the 3D

interposer due to different process and stack-up technologies.

For the purpose of this study, three types of arrangements are

considered, - (a) 30pF/via, representing a high capacitance

density P/G via in glass (b) 3pF/via, representing current

generation P/G capacitance from tantalum deposition on glass,

and (c) 25fF/via, representing a polymer based coaxial vias. It

can be seen that each capacitance technology will provide

decoupling capacitances at specific frequencies based on their

resonance frequencies, and the highest PDN benefit can be

obtained by having the largest capacitance near the chip

probing location.

Figure 13: PDN impact due to 3D interposers

Figure 14: Resonance suppression due to coaxial vias

Figure 15: PDN impact due to via placement variations

1E

8

1E

9

1E

10

1E

7

2E

10

1E-1

1

1E1

1E-2

7E1

Frequency (Hz)M

ag (

Z11

)

PCB+ Interposer

PDN for 2D Full

BGA Glass

Interposer

Parallel Resonance between P/G

Plane capacitance and Lateral

Trace Inductance

PCB+ Interposer

P/G Planes for 3D

Double Side

Interposer

1E

7

1E

8

1E

9

1E

10

1E

6

2E

10

1E-1

1

1E1

1E-2

5E12D

Interposer

3D

Interposer

Resonance Suppressed

due to Coaxial TPVs

for 3D interposer

Frequency (Hz)

Ma

g (

Z11

)

Frequency (Hz)

Ma

g (

Z11

)

Uniform

Staggered

1E

7

1E

8

1E

9

1E

10

1E

6

2E

10

1E-1

1

1E1

1E-2

4E1

Peripheral

546

Figure 16: PDN impact due to decoupling via capacitance

variation

V. SUMMARY AND CONCLUSION

This paper examines the modeling, analysis, design, and

fabrication of coaxial TPVs to improve power integrity of 3D

glass interposers. The addition of co-axial TPVs generated a

decoupling network between the P/G planes, thus reducing the

magnitude of PDN resonances. Based on the proposed

structure, a uniform grid distribution of coaxial vias was found

to have the maximum benefit to suppress 3-D system self-

impedance. Cross-sections from the process test vehicles based

on ultra-thin 100µm glass samples containing coaxial TPVs

were fabricated. Overall, the proposed coaxial method enables

effective PDN design in 3D interposers, offering a simpler and

scalable approach to improve power integrity.

Acknowledgments

The authors would like to acknowledge the LGIP

consortium industry members for their support and Srikrishna

Sitaraman and Vijay Sukumaran for useful discussions.

References

[1] G. Kumar, T. Bandyopadhyay, V. Sukumaran, V.

Sundaram, L. Sung-Kyu, and R. Tummala, "Ultra-

high I/O density glass/silicon interposers for high

bandwidth smart mobile applications," in Electronic

Components and Technology Conference (ECTC),

2011 IEEE 61st, 2011, pp. 217-223.

[2] V. Sukumaran, G. Kumar, K. Ramachandran, Y.

Suzuki, K. Demir, Y. Sato, et al., "Design,

Fabrication, and Characterization of Ultrathin 3-D

Glass Interposers With Through-Package-Vias at

Same Pitch as TSVs in Silicon," Components,

Packaging and Manufacturing Technology, IEEE

Transactions on, vol. PP, pp. 1-1, 2014.

[3] V. Sundaram et al, "“Ultra-thin interposer assembly

with through vias”, May 3 2012.

[4] G. Kumar, S. Sitaraman, C. Jonghyun, K. Sung Jin, V.

Sundaram, K. Joungho, et al., "Power delivery

network analysis of 3D double-side glass interposers

for high bandwidth applications," in Electronic

Components and Technology Conference (ECTC),

2013 IEEE 63rd, 2013, pp. 1100-1108.

[5] C. Jonghyun, K. Youngwoo, K. Joungho, V.

Sundaram, and R. Tummala, "Analysis of glass

interposer PDN and proposal of PDN resonance

suppression methods," in 3D Systems Integration

Conference (3DIC), 2013 IEEE International, 2013,

pp. 1-5.

[6] V. Sridharan, M. Swaminathan, and T.

Bandyopadhyay, "Enhancing Signal and Power

Integrity Using Double Sided Silicon Interposer,"

Microwave and Wireless Components Letters, IEEE,

vol. 21, pp. 598-600, 2011.

[7] X. Biancun and M. Swaminathan, "Modeling and

analysis of SSN in silicon and glass interposers for 3D

systems," in Electrical Performance of Electronic

Packaging and Systems (EPEPS), 2012 IEEE 21st

Conference on, 2012, pp. 268-271.

[8] W. Yushu, X. Shu, M. R. Pulugurtha, H. Sharma, B.

Williams, and R. Tummala, "All-Solution Thin-film

Capacitors and Their Deposition in Trench and

Through-Via Structures," Components, Packaging

and Manufacturing Technology, IEEE Transactions

on, vol. 3, pp. 688-695, 2013.

[9] S. Gandhi, X. Shu, P. M. Raj, V. Sundaram, M.

Swaminathan, and R. Tummala, "A low-cost

approach to high-k thinfilm decoupling capacitors on

silicon and glass interposers," in Electronic

Components and Technology Conference (ECTC),

2012 IEEE 62nd, 2012, pp. 1356-1360.

[10] S. Gandhi, P. M. Raj, V. Sundaram, H. Sharma, M.

Swaminathan, and R. Tummala, "A new approach to

power integrity with thinfilm capacitors in 3D IPAC

functional module," in Electronic Components and

Technology Conference (ECTC), 2013 IEEE 63rd,

2013, pp. 1197-1203.

[11] N. H. Khan, S. M. Alam, and S. Hassoun, "Power

Delivery Design for 3-D ICs Using Different

Through-Silicon Via (TSV) Technologies," Very

Large Scale Integration (VLSI) Systems, IEEE

Transactions on, vol. 19, pp. 647-658, 2011.

Frequency (Hz)

Ma

g (

Z11

)

1E

7

1E

8

1E

9

1E

10

1E

6

2E

10

1E-1

1

1E1

1E2

1E-2

25fF/Via

3pF/Via

30pF/ViaLower capacitance shifts

to higher frequencies

547