Clock Feedthrough in CMOS Analog Transmission Gate …An analysis of clock feedthrough in CMOS...

Transcript of Clock Feedthrough in CMOS Analog Transmission Gate …An analysis of clock feedthrough in CMOS...

Analog Integrated Circuits and Signal Processing, 44, 271–281, 2005c© 2005 Springer Science + Business Media, Inc. Manufactured in The Netherlands.

Clock Feedthrough in CMOS Analog Transmission Gate Switches∗

WEIZE XU AND EBY G. FRIEDMANDepartment of Electrical and Computer Engineering, University of Rochester, Rochester, New York 14627-0231, USA

Received January 19, 2004; Revised April 28, 2004; Accepted May 28, 2004

Abstract. An analysis of clock feedthrough in CMOS analog transmission gate (TG) switches is presented in thispaper. The mechanism for clock feedthrough and a related model of a transmission gate switch are established inthe current-voltage domain. A region map is developed for the TG switch during the period when both devices areturned off. The region map is further divided into zones. From these region and zone maps, the sign and relativemagnitude of the clock feedthrough noise can be efficiently estimated for different signal levels. Placing the inputvoltage near half of the power supply voltage is a useful technique for minimizing clock feedthrough noise. A modelof clock feedthrough noise as compared with SPICE simulations exhibits less than 3% error.

Key Words: CMOS, mixed signal IC, switched capacitor circuit, transmission gate, noise, clock feedthrough

1. Introduction

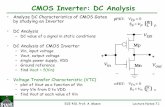

An analog switch is a basic component in integratedcircuits (ICs). The on/off behavior of an analog switchis controlled by the gate voltages that govern the pres-ence of charge in the inversion channel underneath thegates. A CMOS transmission gate switch is shown inFig. 1.

With process scaling and the increasing demand forportable systems, a lower power supply voltage hasbecome common. In order to pass a large analog signal,single MOSFET switches are replaced by transmissiongate switches in many analog circuits. A TG switch hasan approximately uniform on-resistance, and can passwide analog signal swings.

Clock feedthrough is a fundamental problem inanalog ICs. The most commonly accepted clockfeedthrough mechanism (in the charge domain) occurswhen the switch is turned off, dispersing the chargein the inversion channel, forcing current to flow either

∗This research was supported in part by the Semiconductor ResearchCorporation under Contract No. 99-TJ-687, the DARPA/ITO underAFRL Contract F29601-00-K-0182, grants from the New York StateOffice of Science, Technology & Academic Research to the Cen-ter for Advanced Technology—Electronic Imaging Systems and tothe Microelectronics Design Center, and by grants from Xerox Cor-poration, IBM Corporation, Intel Corporation, Lucent TechnologiesCorporation, and Eastman Kodak Company.

into the substrate or the load capacitor at the MOS-FET drain or source. This mechanism produces an er-ror voltage on the load capacitor. This flow of electronswas first called charge feedthrough by Stafford et al.[1]. Sheu and Hu [2], and Shieh et al. [3] publishedanalytical models of strong inversion channel injec-tion and gate-to-drain overlap capacitive coupling inNMOS switches. Wegmann used the continuity equa-tion to model clock feedthrough for a single MOSFETswitch [4]. More recently, Gu and Chen described acharge injection model that includes weak inversion in-jection [5]. All of these papers, however, only considera single NMOS switch. In this paper, clock feedthroughin a TG switch is modeled as coupling from the tran-sistor gate and overlap capacitors. A clock feedthroughmechanism for an analog TG switch is also presentedin the current-voltage domain. This clock feedthroughmechanism is applicable for both TG switches and forsingle PMOS or NMOS analog switches.

In Section 2, the mechanism of clock feedthroughin TG switches is discussed. Clock feedthrough in thefull conduction region is considered in Section 3. Clockfeedthrough noise generated in the half conduction re-gion is analyzed for a TG switch in Section 4. Clockfeedthrough in the subthreshold/cutoff region is de-scribed in Section 5. A discussion of these results ispresented in Section 6. Some conclusions are providedin Section 7.

272 Xu and Friedman

Fig. 1. CMOS TG analog switch: (a) device cross section, (b) circuitsymbol.

Fig. 2. Current flow in a MOSFET.

2. Mechanism of Clock Feedthroughin TG Switches

Three currents flow in a MOSFET at the time the switchis turned off (see Fig. 2). These currents are the MOS-FET drain current ID , the coupling current Igd throughthe overlap capacitor Cgd, and the coupling current Icox

through the gate capacitor Cox.Clock feedthrough error is due to capacitive coupling

from the overlap capacitor Cgd and the gate capacitorCox to the sample and hold (S/H) capacitor CL . TheMOSFET drain current ID supplies charge to compen-sate for the error voltage (generated from the coupling)until the MOSFETs are completely cut-off. The clockfeedthrough error voltage �Verror on a S/H capacitorCL is determined by the difference between the coupledcharge and the charge injected by the transistor current.A slower gate voltage signal provides the MOSFETdrain current with additional time to compensate forthe coupling error.

�Verror = �Q

CL= 1

CL·(

�Qcoupling −∫ t

0ID(t) dt

).

(1)

2.1. Clock Feedthrough in TG Switches

The circuit depicted in Fig. 3 is a CMOS TG switch.An input voltage Vin is sampled onto the S/H capacitorCL by applying a low voltage at the gate of the PMOS

Fig. 3. An analog TG switch with S/H capacitor, CL .

transistor and a high voltage at the gate of the NMOStransistor. Due to coupling from capacitors Cox and Cgd,an error voltage is generated on CL when the switch isturned off (called switch-off). Switch-off in this paperis defined as the time period when the gate voltage onan NMOS transistor changes from Vdd to 0 and the gatevoltage on a PMOS transistor changes from 0 to Vdd.

Three pairs of current flow in a TG switch duringthe period of switch off. These current pairs are dividedinto noise generating pairs and noise reducing pairs. Asshown in Fig. 3, the first noise generating current pair,Igdn and Igdp, couples currents from the gates to the loadcapacitor through the MOSFETs gate-to-drain overlapcapacitors. The second noise generating pair is Icoxn

and Icoxp. Current in the noise generating pairs flowin opposite direction and compensate each other. Forperfectly matched current pairs, noise generated fromthese pairs is zero when both transistors conduct (thefull conduction region as discussed later). The noisereducing current pair, IDN and IDP, are currents suppliedby the MOSFETs in the TG switch.

2.2. Modeling Clock Feedthrough in TG Switches

The transmission gate switching process is modeled inthis subsection and shown in Fig. 4. The MOSFETs aremodeled as voltage controlled resistors. Coupling fromthe gate capacitors and the gate-to-drain overlap capac-itors are represented by currents Icoxn, Icoxp, Igdn, andIgdp. The MOSFETs are assumed to operate in the linearregion and produce the MOSFET currents, IDN and IDP.

Current and voltage differential equations can be es-tablished from the circuit shown in Fig. 4. These equa-tions are solved in Sections 3, 4 and 5, permitting theclock feedthrough noise voltage generated within eachregion to be analytically determined.

Clock Feedthrough in CMOS Analog Transmission Gate Switches 273

Fig. 4. Model of an analog TG switch during switch off.

Fig. 5. Region map when turning off the TG switch (Wn = Wp , Ln = L p , and VTN = |VTP| = Vth).

2.3. The Region Map

The voltages applied at the gates of the PMOS andNMOS transistors are modeled as a ramp signal asshown in Fig. 5. The operation of the TG switch duringswitch off is divided into three regions based on thestates of the two transistors. When the ramp input volt-age Vg is applied at the gate of the PMOS transistor andV̄ g is applied at the gate of the NMOS transistor, theTG operates in one of three regions: full conduction,half conduction, and subthreshold/cutoff. During fullconduction, both of the PMOS and NMOS transistorsconduct. The half conduction region occurs when onlyone of the two transistors conducts current and the othertransistor is off. The subthreshold/cutoff region occurswhen both of the PMOS and NMOS transistors areoff. The voltages applied on the gates of the transistorsare

Vg = Vdd · t/τs, (2)

V̄ g = (1 − t/τs) · Vdd. (3)

In the region map as shown in Fig. 5, two boundarylines divide the operation of the analog TG switch intothree regions. The two boundary lines are the P-line(the solid line shown in Fig. 5) and the N -line (thedotted line shown in Fig. 5).

The PMOS transistor is off when the operating point(vin, t) of the switch is under the P-line as shown inFig. 5. Similarly, the NMOS transistor is off whenthe operating point (vin, t) of the switch is above theN -line.

The P boundary line is described as

{Vin = Vdd · t/τs, Vin > |Vth| (4)

Vin = |Vth|, Vin < |Vth| (5)

and the N boundary line is described as

{Vin = Vdd(1 − t/τs), Vin < Vdd − Vth (6)

Vin = Vdd − Vth, Vin > Vdd − Vth. (7)

274 Xu and Friedman

The times ta , tb and tc, shown in Fig. 5, are, respec-tively,

ta = τs Vin/Vdd, Vin > Vdd − Vth (8)

tb = τs(1 − Vin/Vdd), Vin < Vdd − Vth (9)

tc = τs Vin/Vdd, Vin = Vth. (10)

As described in the following sections, clockfeedthrough noise can be estimated from the valuesof ta , tb, and tc.

The absolute value of the clock feedthrough in eachregion is directly proportional to the length of timethe TG switch remains in that region. For example, asshown in Fig. 5, for an input voltage Vin (the sampledvoltage), the length of time the switch operates in thefull conduction region is ta , tb−ta in the half conductionregion, and τ s − tb in the subthreshold/cutoff region.The relationship between the region map and clockfeedthrough noise is used to explain the results pre-sented in the following sections. The region map shownin Fig. 5 is generated from a symmetric TG switch. Theregion map shown in Fig. 5, however, is general andis applicable for both symmetric and asymmetric TGswitches.

3. Clock Feedthrough in the FullConduction Region

As shown in Fig. 3, seven currents flow in a TG switchduring the switch off process. IL is the current sourcingor sinking capacitor CL , IDN and IDP are the NMOS andPMOS drain currents, respectively, and Igdn and Igdp arethe coupling currents flowing through the MOS tran-sistor gate-to-drain overlap capacitors. Icoxp and Icoxn

are the coupling currents flowing through the gate ca-pacitors. During the full conduction region, all sevencurrents exist. From the current conservation law ap-plied at the output node of Fig. 3, a system equation isobtained,

IL = Igdn + Igdp − (IDN − Icoxn) + (IDP − Icoxp),

(11)

CLeffdVe

dt

= − Ve

Rsw−

(Cgdn − Cgdp + Coxn + Coxp

2

)· Vdd

τs,

(12)

where Rsw is the TG switch “on” resistance.

1

Rsw= 1

RN+ 1

RP= kn · (V̄ G − Vin − VTN)

+ kp · (Vin − |VTP| − VG), (13)

CLeff = CL + Cgdn + Cgdp, (14)

kn = µnCoxN(W/L)N , (15)

kp = −|µp|CoxP(W/L)P , (16)

where kn , kp, VTN, VTP, (W/L)N , and (W/L)P

are the current factor, threshold voltage, and thewidth/length ratio of the NMOS and PMOS transistors,respectively.

An expression for the error voltage on the hold ca-pacitor CL during the full conduction region is solvedfrom the differential equation characterized by (12) andis

Ve1(t) = −√

πVddCLeff

2τs(kn − |kp|)

·(

2Cgdn − 2Cgdp + CoxN − CoxP

2CLeff

)

· exp

{(kn − |kp|)Vdd

2τsCLeff

(t − A1τs

Vdd

)2}

·{

erf

[√τs(kn − |kp|)

2VddCLeff· A1

]

− erf

[√τs(kn − |kp|)

2VddCLeff·(

A1 − Vdd

τs· t

)]}.

(17)

A1 = kn Vdd − (kn + |kp|) · Vin − kn VTN + |kp| · |VTP|kn − |kp| .

(18)

The error (noise) voltage generated during the fullconduction region as shown in (17) is a function ofthe input voltage, gate voltage transition time, S/H ca-pacitance, and the size of the MOSFET transistors.The resulting clock feedthrough error is graphically de-picted in Fig. 6. The error voltage generated by clockfeedthrough within the TG switch during the full con-duction region is due to coupling of the gate voltagesthrough Coxn, Coxp, Cgdn, and Cgdp. Coupling from thegate capacitors of the NMOS and PMOS transistorshas opposite polarity which compensate each other.The same phenomenon occurs in coupling from the

Clock Feedthrough in CMOS Analog Transmission Gate Switches 275

Fig. 6. Clock feedthrough error of an analog TG switch generated during the full conduction region (Wn = Wp = 10 µm, Ln = L p = 0.35 µm,kn = 40 mA/V2, |kP | = 10 mA/V2, CL = 1 pF, and COXN = COXP = 3 fF/µm2).

overlap capacitor. Equation (17) also shows that clockfeedthrough in the full conduction region is zero ifCoxn equals Coxp and Cgdn equals Cgdp. Due to cur-rent cancellation in the two noise generating pairs,clock feedthrough during the full conduction regionis small. Clock feedthrough in the full conduction re-gion is determined from (17). These results are illus-trated in Fig. 6. The three-dimensional characteristicsof clock feedthrough in the full conduction region canbe explained based on the region map described in theprevious section.

When the input voltage is below Vth, the PMOS tran-sistor is off. Full conduction does not occur (the TGswitch is in the half conduction region) and the errorvoltage in full conduction is zero as shown in Fig. 6.

Once Vin exceeds the PMOS threshold voltage Vth,the TG switch enters the full conduction region. In-creasing the input voltage, the TG switch resistanceRSW increases, and less MOS current is supplied tocompensate the coupling error voltage. Because theMOSFETs are equally sized, the coupling currentsfrom the gate capacitors are completely canceled. Onlycoupling through the gate-to-drain overlap capacitorsgenerates noise. Capacitive coupling between Cgd andCL is larger due to a smaller gate voltage at the endof the full conduction region. The error, therefore, in-

creases with higher input voltage. As shown in the re-gion map, when the input voltage increases above Vth,the length of time in the full conduction region be-comes greater. The clock feedthrough noise generatedin this region therefore increases (clock feedthroughnoise in any region is proportional to the length oftime the switch remains in that region) (see Figs. 5 and8–10).

When the input voltage is approximately half thepower supply voltage (assuming VTN = |VTP| andkn = kp), the switch resistance RSW is greatest, thefull conduction region is widest (Fig. 5), and the errorvoltage on the capacitor CL reaches a maximum. Theregion map shows that the length of time the TG switchoperates in this region reaches a maximum when theinput voltage is at half of the power supply voltage. Asdescribed by the region map, the noise generated in thefull conduction region is maximum.

As shown in Fig. 5, the width of the full conduc-tion region decreases as the input signal increases to-ward Vdd from half of the power supply voltage. Theerror voltage, therefore, decreases with increasing in-put voltage due to weaker capacitive coupling and alarger MOSFET current flowing through the switch.A slower gate ramp voltage (larger τs in Fig. 5) per-mits the transistor to source current for a longer time,

276 Xu and Friedman

thereby compensating the error on the load capacitorCL , resulting in a smaller error voltage. The region mapshows the decreasing length of the full conduction re-gion. The clock feedthrough noise decreases. The TGswitch exits the full conduction region when the inputvoltage passes Vdd − Vth (the NMOS transistor is off)and the clock feedthrough noise returns to zero.

4. Half Conduction

In the half conduction region, one transistor operates inthe linear region while the other transistor is off. The du-ration of the half conduction region is |tb−ta|, as shownin Fig. 5. The clock feedthrough noise generated dur-ing the half conduction region is directly proportionalto the time within the region |tb−ta|. Clock feedthroughin this region is due to coupling through the gate ca-pacitor of the conducting MOSFET and coupling fromthe overlap capacitors of both of the MOSFETs. Asin the full conduction region, the drain current of theconducting MOSFET compensates the coupling error.The current in the off transistor is much smaller and istherefore ignored. In the half conduction region, onenoise generating current in the gate current pair is zeroso that current compensation in this current pair doesnot exist. The noise generated in this region is thereforehigher. The other current pair generating noise is due tothe overlap capacitors of both of the NMOS and PMOStransistors which contribute to the error voltage.

Two cases can exist during the half conduction re-gion. With one case, the NMOS transistor conductsand the PMOS transistor is off. In the other case, thePMOS transistor conducts and the NMOS transistor isoff. The first case shown in the region map is defined aszone A of the half conduction region, and the secondcase is defined as zone B of the half conduction re-gion. Depending upon the input sampled voltage level,the TG switch operates in one of the two zones dur-ing the half conduction region. The clock feedthroughnoise voltage generated in Zone A is negative, andpositive in zone B. The PMOS transistor is off withinzone A.

The PMOS drain current IDP and coupling currentIcoxp shown in Fig. 3 are zero. The error voltage in thehalf conduction region is obtained by solving the differ-ential equations, (12) and (13). The clock feedthroughnoise in zone A is

Ve2(t) = −βN · fN (t) + Ve1(ta) ta < t < tb, (19)

where Ve1(ta) is the error voltage generated during thefull conduction region and determined from (17),

βN =√

πVddCLeff

2τskn·(

Cgdn − Cgdp + CoxN

2

)/CLeff,

(20)

and

fN (t)

= exp

{kn · Vdd

2τsCLeff

(t − ta − Vdd − Vin − VTN

Vdd· τs

)2}

·{

erf

[√kn · τs

2VddCLeff· (Vdd − Vin − VTN)

]

− erf

[√kn · τs

2VddCLeff·(

Vdd − Vin − VTN − Vdd

τst

)]}.

(21)

For those input voltage levels that maintain the TGswitch within zone B during the half conduction region,the NMOS transistor is off so that kn and Coxn can beremoved from the system Eq. (12). Solving (12) and(13), the clock feedthrough noise generated in zone Bis

Ve2(t) = −βP · fP (t) + Ve1(tb) ta < t < tb, (22)

βP = −√

πVddCLeff

2τs |kp|

·(

Cgdn − Cgdp + CoxP

2

)/CLeff, (23)

and

fP (t) = exp

{ |kp| · Vdd

2τsCLeff

(t − tb − Vin − |VTP|

Vdd· τs

)2}

·{

erf

[√|kp| · τs

2VddCLeff· (Vin − |VTP|)

]

− erf

[√|kp| · τs

2VddCLeff·(

Vin − |VTP| − Vdd

τst

)]}.

(24)

The clock feedthrough error generated during zones Aand B is determined from (19) and (22) [without theterm Ve1(ta)] and illustrated in Fig. 8.

Clock Feedthrough in CMOS Analog Transmission Gate Switches 277

Fig. 7. Zones in the half conduction region for a symmetric TG switch (VTN = |VTP| = Vth, Wn = Wp , and Ln = L p).

The error waveform illustrated in Fig. 8 can be ex-plained from the zone map shown in Fig. 7. When theinput signal voltage ranges from 0 to Vth, the TG switchoperates in the half conduction zone A. Due to cou-pling between the NMOS gate capacitor and the S/H

Fig. 8. Clock feedthrough error of a TG switch during the half conduction region (Vdd = 3.3 volts, Wn = Wp , and Ln = L p).

capacitor, the total clock feedthrough error is negative(see Fig. 8). The length of time tb − ta is a maximum.

Increasing the input voltage makes tb − ta shorter,and the absolute value of the clock feedthrough noiseslowly decreases. Increasing the input voltage above

278 Xu and Friedman

Vth, tb − ta decreases two times faster than when theinput voltage is between 0 to Vth. As a result, the ab-solute value of the clock feedthrough noise decreasestwice as fast as shown in Fig. 8. When the input signalis half of the power supply, half conduction does notexist (for symmetric TG switches) and the error volt-age generated during the half conduction region is zero(see Fig. 8).

Increasing the input voltage from VDD/2, assumingVTN = VTP = Vth, the TG switches into zone B. Clockfeedthrough is primarily caused by coupling of the gatevoltage between the PMOS transistor gate capacitorCOXP and the S/H capacitor CL . The clock feedthroughvoltage becomes positive (see Fig. 7). A larger inputvoltage makes the TG switch remain in zone B longer(see Fig. 7). The error voltage, therefore, increases witha larger input signal when the input voltage is greaterthan VDD/2, as shown in Fig. 8.

When the input voltage level reaches Vdd − Vth, thelength of time tb − ta increases at half the speed ascompared to when the input voltage is between Vdd/2and Vdd/2 − Vth. The clock feedthrough noise voltageincreases slowly with increasing input voltage.

Increasing the ramp constant τs provides a longertime for the MOS transistor drain current to compensatethe coupling error voltage on CL . The error is smallerfor larger τs . Comparing Fig. 8 with Fig. 6, the clockfeedthrough noise generated in the half conduction re-gion is much larger than the clock feedthrough noisegenerated in the full conduction region. Ensuring thatthe TG switch operates in the half conduction regionfor a short amount of time is important for reducingthe clock feedthrough noise voltage. Level shifting theinput voltage to approximately half of the power sup-ply voltage will therefore minimize clock feedthroughnoise in a TG switch.

5. Subthreshold/Cutoff Region

The error voltage generated in the subthreshold/cutoffregion is due to coupling of the gate voltage through thegate-to-drain overlap capacitors Cgd of the two transis-tors to the S/H (load) capacitor CL . Because both ofthe NMOS and PMOS transistors are off, there is nochannel generated under the gates.

The channel resistance in the proposed clockfeedthrough model is large, therefore, the noise gen-erating current pair, the gate capacitor coupling cur-rents Icoxn and Icoxp, can be ignored. The subthresh-

old currents in the NMOS and PMOS transistors areon the order of 10−15 to 10−17 A/µm and are there-fore ignored. Due to the low charge density as com-pared to the charge density of the induced channel,currents from discharging the PMOS and NMOS tran-sistor depletion layers can also be ignored. The clockfeedthrough noise generated in the subthreshold/cutoffregion (for symmetric TG switches) is thereforenegligible.

The clock feedthrough voltage generated during thesubthreshold/cutoff region is shown in Fig. 9. Thethree-dimensional curve can also be explained by theregion map. As shown in Fig. 9, clock feedthroughduring the subthreshold/cutoff region is small as com-pared to the clock feedthrough noise generated in thehalf conduction region. The region map shown in Fig. 5describes, for a symmetric TG switch, the shape of thesubthreshold/cutoff region which is symmetric with thefull conduction region. The clock feedthrough noisevoltage generated in the subthreshold/cutoff region istherefore a mirror image of the clock feedthrough noisegenerated in the full conduction region, as shown inFigs. 6 and 9, except during the time when the sampledinput voltages are near the ground and power supplyvoltages.

6. Simulation Results

Based on the physical mechanisms described in theprevious sections, clock feedthrough in a TG switchis shown in Fig. 10 to be a function of the transistorsize, load capacitor, input voltage, and the gate voltagetime constant τs . The total clock feedthrough is thesum of the error voltage generated in the three regionsduring the time required to turn off the transistors. Froman analysis of clock feedthrough for a symmetric TGswitch (the NMOS and PMOS transistors have the samegeometric dimensions and magnitude of the thresholdvoltages), the clock feedthrough error generated in thehalf conduction region is shown to be dominant. ASPICE simulation of clock feedthrough within the sameTG switch is illustrated in Fig. 10(b).

As shown in Fig. 10(a) and (b), results from the pro-posed model and SPICE simulation are in close agree-ment. The error from the proposed model is less than3% for most of the sampled voltages as compared toSPICE simulations, and the error is less than about9% when the sampled input voltage is near the powersupply voltage.

Clock Feedthrough in CMOS Analog Transmission Gate Switches 279

Fig. 9. Clock feedthrough error of a TG switch during the subthreshold/cutoff region (Vdd = 3.3 volts, Wn = Wp , and Ln = L p).

Fig. 10. Clock feedthrough voltage of a TG switch (a) analytically determined, (b) SPICE simulation (Vdd = 3.3 volts, VTN = |VTP| = 0.6volts, Wn = Wp = 10 µm, L N = L P = 0.35 µm, kn = 40 mA/V2, |kP | = 10 mA/V2, CL = 1 pF, and COXN = COXP = 3 fF/µm2).

7. Conclusions

Clock feedthrough in a TG switch is due to couplingof the gate voltage between the MOSFET overlap ca-pacitors Cgd and the gate capacitors COX and the S/Hcapacitor CL . The MOSFETs in a TG switch supply

currents that compensate the coupling error on an S/Hload capacitor. A region map of the TG switch duringswitch off can be used to efficiently estimate the clockfeedthrough noise. For a specific input voltage, thepolarity and relative magnitude of the clockfeedthrough noise can also be determined. For a

280 Xu and Friedman

symmetric TG switch, the input sampled voltageis chosen to be around half of the power supplyin order to minimize clock feedthrough noise. Thischoice of bias condition can significantly reduce clockfeedthrough noise. The input sampled voltages canalso be shifted to make the clock feedthrough noisealways positive or negative which is preferable to othernoise reduction techniques. In a TG switch, clockfeedthrough generated during the half conduction re-gion causes most of the error on the S/H capaci-tor. Clock feedthrough during the subthreshold/cutoffregion is small and can be ignored. A slower gateinput voltage signal provides a longer time for theMOSFET currents to compensate the coupling volt-age, thereby reducing the clock feedthrough error volt-age. An error of less than 3% is noted in the ana-lytic expressions as compared to SPICE simulations.

References

1. K.R. Stafford, P.R. Gary, and R.A. Blanchard, “A com-plete monolithic sample/hold amplifier.” IEEE Journalof Solid-State Circuits, vol. SC-9, no. 3, pp. 381–387,1974.

2. B. Sheu and C. Hu, “Switch-induced error voltage on a switchedcapacitor.” IEEE Journal of Solid-State Circuits, vol. SC-19, no. 4,pp. 519–525, 1984.

3. J.H. Shieh, M. Patil, and B.J. Sheu, “Modeling charge in-jection in MOS analog switches.” IEEE Transactions onCircuits and Systems, vol. CAS-34, no. 2, pp. 214–216,1987.

4. G. Wagmann and E. Vittoz, “Charge injection in analog MOSswitches.” IEEE Journal of Solid-State Circuits, vol. SC-22, no. 6,pp. 1091–1097, 1987.

5. Y.B. Gu and M.J. Chen, “A new quantitative model for weakinversion charge injection in MOSFET analog switches.” IEEETransactions on Electron Devices, vol. 43, no. 2, pp. 295–301,1996.

Weize Xu received the B.S. degree from NanjingUniversity of Posts and Telecommunications, Chinain 1982, and the M.S. degrees from the University ofRhode Island in 1993, both in electrical engineering.

Since 1997, he has been a senor research engineer andanalog IC design specialist at Eastman Kodak Com-pany. His research interests include high speed ana-log IC designs, pipelined A/D converter, low powerswitched capacitor circuit analysis and design, CMOSimage sensor design, and analysis of noise in mixedsignal ICs. He currently is a Ph.D candidate at the Uni-versity of Rochester.

Eby G. Friedman (S’78-M’79-SM’90-F’00) re-ceived the B.S. degree from Lafayette College in 1979,and the M.S. and Ph.D. degrees from the University ofCalifornia, Irvine, in 1981 and 1989, respectively, allin electrical engineering.

From 1979 to 1991, he was with Hughes AircraftCompany, rising to the position of manager of the Sig-nal Processing Design and Test Department, responsi-ble for the design and test of high performance digi-tal and analog IC’s. He has been with the Departmentof Electrical and Computer Engineering at the Uni-versity of Rochester since 1991, where he is a Dis-tinguished Professor, the Director of the High Perfor-mance VLSI/IC Design and Analysis Laboratory, andthe Director of the Center for Electronic Imaging Sys-tems. He also enjoyed a sabbatical at the Technion—Israel Institute of Technology during the 2000/2001academic year. His current research and teaching inter-ests are in high performance synchronous digital andmixed-signal microelectronic design and analysis withapplication to high speed portable processors and lowpower wireless communications.

He is the author of more than 250 papers and bookchapters, several patents, and the author or editor ofseven books in the fields of high speed and low powerCMOS design techniques, high speed interconnect,and the theory and application of synchronous clock

Clock Feedthrough in CMOS Analog Transmission Gate Switches 281

distribution networks. Dr. Friedman is the Regional Ed-itor of the Journal of Circuits, Systems, and Computers,a Member of the editorial boards of the Proceedings ofthe IEEE, Analog Integrated Circuits and Signal Pro-cessing microelectronics Journal, and Journal of VLSISignal Processing, a Member of the Circuits and Sys-tems (CAS) Society Board of Governors, and a Mem-ber of the technical program committee of a numberof conferences. He previously was the past Editor-in-Chief of the IEEE Transactions on VLSI Systems, aMember of the editorial board of the IEEE Transactionson Circuits and Systems II: Analog and Digital SignalProcessing, Chair of the IEEE Transactions on VLSI

Systems steering committee, CAS liaison to the Solid-State Circuits Society, Chair of the VLSI Systems andApplications CAS Technical Committee, Chair of theElectron Devices Chapter of the IEEE Rochester Sec-tion, Program or Technical chair of several IEEE con-ferences, Guest Editor of several special issues in a va-riety of journals, and a recipient of the Howard HughesMasters and Doctoral Fellowships, an IBM Univer-sity Research Award, an Outstanding IEEE Chap-ter Chairman Award, and a University of RochesterCollege of Engineering Teaching Excellence Award.Dr. Friedman is a Senior Fulbright Fellow and an IEEEFellow.