CCB021M12FM3 VDS Six-Pack Module RDS(on)

Transcript of CCB021M12FM3 VDS Six-Pack Module RDS(on)

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

1Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

CCB021M12FM31200 V, 21 mΩ All-Silicon Carbide Six-Pack Module

Technical Features

• Ultra-Low Loss• High Frequency Operation• Zero Turn-Off Tail Current from MOSFET• Normally-Off, Fail-Safe Device Operation

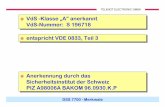

VDS 1200 V

RDS(on) 21 mΩ

System Benefits

• Enables Compact, Lightweight Systems• Increased System Efficiency due to Low Switching & Conduction Losses of SiC• Reduced Thermal Requirements and System Cost

Applications

• EV Chargers• Solar• High-Efficiency Converters / Inverters• Motor & Traction Drives• Smart-Grid / Grid-Tied Distributed Generation

Package

Maximum Parameters (Verified by Design)

Symbol Parameter Min. Typ. Max. Unit Test Conditions Note

VDS max Drain-Source Voltage 1200

VVGS max Gate-Source Voltage, Maximum Value -8 +19 Transient, <100 nsFig. 33

VGS opGate-Source Voltage, Recommended Op. Value -4 +15 Static

IDDC Continuous Drain Current (TVJ ≤ 150 ˚C) 51

A

VGS = 15 V, TH= 50 ˚C, TVJ ≤ 150 ˚C Fig. 20Note 1DC Continuous Drain Current (TVJ ≤ 175 ˚C) 53 VGS = 15 V, TH= 50 ˚C, TVJ ≤ 175 ˚C

ISD BD DC Source-Drain Current (Body Diode) 23 VGS = - 4 V, TH = 50 C, TVJ ≤ 175 C

ID (pulsed) Maximum Pulsed Drain Current 106 tPmax limited by Tjmax

VGS = 15 V, TH = 50 ˚C

TVJ opMaximum Virtual Junction Temperature under Switching Conditions

-40 150 °C Operation

-40 175 °C Intermittent with Reduced Life

Note 1. DC continuous drain current rating, ID, limited to 30 A by the press-fit pins.

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

2Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

MOSFET Characteristics (Per Position) (TVJ = 25˚C unless otherwise specified)

Symbol Parameter Min. Typ. Max. Unit Test Conditions Note

V(BR)DSS Drain-Source Breakdown Voltage 1200V

VGS = 0 V, TVJ = -40 °C

VGS(th) Gate Threshold Voltage 1.8 2.5 3.6 VDS = VGS, ID = 17.7 mA

IDSS Zero Gate Voltage Drain Current 1 25 μA VGS = 0 V, VDS = 1200 V

IGSS Gate-Source Leakage Current 10 250 nA VGS = 15 V, VDS = 0 V

RDS(on)Drain-Source On-State Resistance (Devices Only)

21.0 27.9

mΩ

VGS = 15 V, ID = 30 AFig. 2Fig. 332.6 VGS = 15 V, ID = 30 A, TVJ = 150 °C

38.0 VGS = 15 V, ID = 30 A, TVJ = 175 °C

gfs Transconductance26.1

SVDS= 20 V, IDS= 30 A

Fig. 425.9 VDS= 20 V, IDS= 30 A, TVJ = 150 °C

EOn

Turn-On Switching Energy, TJ = 25 °CTVJ = 125 °CTVJ = 150 °C

0.500.550.62

mJ

VDS = 600 V, ID = 30 A,VGS = -4 V/15 V, RG(OFF) = 0.0 Ω, RG(ON) = 0.0 ΩL= 45.1 μH

Fig. 11Fig. 13

EOff

Turn-Off Switching Energy, TJ = 25 °CTVJ = 125 °CTVJ = 150 °C

0.0200.0350.044

RG(int) Internal Gate Resistance 3.3 Ω TVJ = 25 °C, f = 100 kHz, VAC = 25 mV

Ciss Input Capacitance 4.9 nFVGS = 0 V, VDS = 800 V,

VAC = 25 mV, f = 100 kHzFig. 9Coss Output Capacitance 209

pFCrss Reverse Transfer Capacitance 16

QGS Gate to Source Charge 49

nCVDS = 800 V, VGS = -4 V/15 VID = 40 APer IEC60747-8-4 pg 21

QGD Gate to Drain Charge 50

QG Total Gate Charge 162

Rth JHFET Thermal Resistance, Junction to Heatsink 1.16 °C/W Fig. 17

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

3Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Module Physical Characteristics

Symbol Parameter Min. Typ. Max. Unit Test Conditions

RHS Package Resistance, M1, M3, M5 (High-Side)5.3

mΩ

TC = 25 °C, ID = 30 A, Note 2

5.9 TC = 125 °C, ID = 30 A, Note 2

RLS Package Resistance, M2, M4, M6 (Low-Side)7.4 TC = 25 °C, ID = 30 A, Note 2

8.1 TC = 125 °C, ID = 30 A, Note 2

LStray Stray Inductance 17.4 nH Between Terminals DC+ and DC-

TC Case Temperature -40 125 °C

W Weight 21 g

MS Mounting Torque 2.0 2.3 N-m M4 bolts

Visol Case Isolation Voltage 3 kV AC, 50 Hz, 1 min

CTI Comparative Tracking Index 200

Clearance Distance5.0

mm

Terminal to Terminal

10.0 Terminal to Heatsink

Creepage Distance6.3 Terminal to Terminal

11.5 Terminal to Heatsink Note 2. Total Effective Resistance (Per Switch Position) = MOSFET RDS(on) + Switch Position Package Resistance.

Symbol Parameter Min. Typ. Max. Unit Test Conditions Note

VSD Body Diode Forward Voltage5.3

VVGS = -4 V, ISD = 30 A

Fig. 74.8 VGS = -4 V, ISD = 30 A, TVJ = 150 °C

trr Reverse Recovery Time 16 ns VGS = -4 V, ISD = 30 A, VR = 600 Vdi/dt = 16 A/ns, RG(ON) = 0.0 Ω,TJ = 150 °C

Fig. 32QRR Reverse Recovery Charge 1.3 μC

IRRM Peak Reverse Recovery Current 135 A

ERR

Reverse Recovery Energy TJ = 25 °CTJ = 125 °CTJ = 150 °C

0.140.200.25

mJVDS = 600 V, ID = 30 A,VGS = -4 V/15 V, RG(ON) = 0.0 Ω, L= 45.1 μH

Fig. 14

Diode Characteristics (Per Position) (TVJ = 25˚C unless otherwise specified)

Symbol Parameter Min. Typ. Max. Unit Test Conditions Note

RNTC Rated Resistance 5.0 kΩ TNTC = 25 °C Fig. 23

∆R/R Resistance Tolerance at 25°C -5 5 %

β25/50 Beta Value (T2 = 50°C) 3380 K

β25/80 Beta Value (T2 = 80°C) 3468 K

β25/100 Beta Value (T2 = 100°C) 3523 K

PMax Power Dissipation 10 mW TNTC = 25 °C

NTC Thermistor Characterization

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

4Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Figure 2. Normalized On-State Resistance vs. Drain Current for Various Junction Temperatures

Typical Performance

Figure 5. 3rd Quadrant Characteristic vs. Junction Temperatures at VGS = 15 V

Figure 1. Output Characteristics for Various Junction Temperatures

Figure 3. Normalized On-State Resistance vs. Junction Temperature

Figure 4. Transfer Characteristic for Various JunctionTemperatures

Figure 6. 3rd Quadrant Characteristic vs. Junction Temperatures at

VGS = 0 V (Body Diode)

0

10

20

30

40

50

60

70

80

90

100

0 0.5 1 1.5 2 2.5 3 3.5 4

Drai

n-So

urce

Cur

rent

, IDS

(A)

Drain-Source Voltage, VDS (V)

150 °C125 °C

-40 °C

100 °C

tp < 300 μsVGS = 15 V

25°C

175 °C

0.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

1.8

-50 -25 0 25 50 75 100 125 150 175 200

Nor

mal

ized

On-

resis

tanc

e (p

.u.)

Virtual Junction Temperature, TVJ (°C)

tp < 300 μsVGS = 15 VID = 50 A

0

10

20

30

40

50

60

70

80

90

100

0 2 4 6 8 10

Drai

n-So

urce

Cur

rent

, IDS

(A)

Gate-Source Voltage, VGS (V)

-25 °C-40 °C

0 °C25 °C

100 °C125 °C

150 °C175 °C

tp < 300 μsVDS = 20 V

0

10

20

30

40

50

60

70

80

90

100

0 0.5 1 1.5 2 2.5 3 3.5

Sour

ce-D

rain

Cur

rent

, ISD

(A)

Source-Drain Voltage, VSD (V)

150 °C125 °C

-40 °C

100 °C

tp < 300 μsVGS = 15 V

25 °C

175 °C

0

10

20

30

40

50

60

70

80

90

100

0 1 2 3 4 5 6 7

Sour

ce-D

rain

Cur

rent

, ISD

(A)

Source-Drain Voltage, VSD (V)

-40 °C

100 °C

tp < 300 μsVGS = 0 V

25 °C0 °C-25 °C

175 °C125 °C

150 °C

0.8

1.0

1.2

1.4

1.6

1.8

2.0

0 20 40 60 80 100

Nor

mal

ized

On-

resis

tanc

e (p

.u.)

Drain-Source Current, IDS (A)

tp < 300 μsVGS = 15 V

25 °C

100 °C

125 °C

150 °C

175 °C

-40 °C

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

5Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Figure 8. Typical Capacitances vs. Drain to Source Voltage(0 - 200V)

Typical Performance

Figure 11. Switching Energy vs. Drain Current(VDS = 600 V)

Figure 7. 3rd Quadrant Characteristic vs. Junction Temperatures at

VGS = - 4 V (Body Diode)

Figure 9. Typical Capacitances vs. Drain to Source Voltage (0 - 1200V) Figure 10. Threshold Voltage vs. Junction Temperature

Figure 12. Switching Energy vs. Drain Current (VDS = 800 V)

0

10

20

30

40

50

60

70

80

90

100

0 2 4 6 8

Sour

ce-D

rain

Cur

rent

, ISD

(A)

Source-Drain Voltage, VSD (V)

150 °C125 °C

-40 °C

100 °C

tp < 300 μsVGS = -4 V

25 °C0 °C-25 °C

175 °C

EOff

EOn

ERR

0.0

0.2

0.4

0.6

0.8

1.0

1.2

0 20 40 60 80 100 120

Switc

hing

Ene

rgy

(mJ)

Source Current, IS (A)

Conditions:TVJ = 25°CVDD = 600 VRG(ext) = 0.0 ΩVGS = -4/+15 VL = 45.1 µH

EOff

EOn

ERR

0.0

0.4

0.8

1.2

1.6

2.0

0 20 40 60 80 100 120

Switc

hing

Ene

rgy

(mJ)

Source Current, IS (A)

Conditions:TVJ = 25°CVDD = 800 VRG(ext) = 0.0 ΩVGS = -4/+15 VL = 45.1 µH

0.0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

-50 -25 0 25 50 75 100 125 150 175 200

Thre

shol

d Vo

ltage

, Vth

(V)

Virtual Junction Temperature, TVJ (°C)

Conditions:VGS = VDSIDS = 18 mA

0.01

0.1

1

10

100

0 200 400 600 800 1,000 1,200

Capa

cita

nce

(nF)

Drain-Source Voltage, VDS (V)

Coss

TJ = 25 °CVAC = 25 mVf = 100 kHz

Crss

Ciss

0.01

0.1

1

10

100

0 50 100 150 200

Capa

cita

nce

(nF)

Drain-Source Voltage, VDS (V)

Coss

TJ = 25 °CVAC = 25 mVf = 100 kHz

Crss

Ciss

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

6Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Figure 14. Reverse Recovery Energy vs. Junction Temperature

Typical Performance

Figure 17. MOSFET Junction to Case Transient Thermal Impedance, Zth JC (°C/W)

Figure 13. MOSFET Switching Energy vs. Junction Temperature

Figure 15. MOSFET Switching Energy vs. External Gate Resistance Figure 16. Reserve Recovery Energy vs. External Gate Resistance

Figure 18. Forward Bias Safe Operating Area (FBSOA)

0.001

0.01

0.1

1

10

1E-6 10E-6 100E-6 1E-3 10E-3 100E-3 1 10

Junc

tion-

to-H

eats

ink I

mpe

d., Z

thjh

s(°

C/W

)

Time, tp (s)

Single Pulse

0.010.02

0.050.1

0.30.5

0.01

0.1

1

10

100

0.1 1 10 100 1000

Drai

n-So

urce

Cur

rent

, IDS

(A)

Drain-Source Voltage, VDS (V)

Limited by RDS(on)

Conditions:Tc = 25 °C D=0 Parameter: tp

EOff

EOn

0.0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0 25 50 75 100 125 150 175

Switc

hing

Ene

rgy

(mJ)

Junction Temperature, TVJ (°C)

Conditions:IS = 30 VDD = 600 VRG(ext) = 0.0 Ω, VGS = -4/+15 VL = 45.1 µH

EOff

EOn

EOff + EOn

ERR0.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

0 2 4 6 8 10 12 14 16

Switc

hing

Ene

rgy

(mJ)

External Gate Resistor, RG(ext) (Ω)

Conditions:TVJ = 25°CIS = 30 AVDD = 600 VVGS = -4/+15 VL = 45.1 µH

ERR (VDD = 600 V)

ERR (VDD = 800 V)

0.00

0.05

0.10

0.15

0.20

0.25

0.30

0.35

0.40

0 25 50 75 100 125 150 175

Reve

rse

Reco

very

Ene

rgy

(mJ)

Junction Temperature, TVJ (°C)

Conditions:IS = 30 ARG(ext) = 0.0 ΩVGS = -4/+15 VL = 45.1 µH

ERR (VDD = 600 V)

0.00

0.02

0.04

0.06

0.08

0.10

0.12

0.14

0 2 4 6 8 10 12 14 16

Reve

rse

Reco

very

Ene

rgy

(mJ)

External Gate Resistor, RG(ext) (Ω)

Conditions:TVJ = 25°CIS = 30 AVDD = 600 VVGS = -4/+15 VL = 45.1 µH

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

7Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Figure 20. Continuous Drain Current Derating vs. Case Temperature

Typical Performance

Figure 19. Reverse Bias Safe Operating Area (RBSOA)

Figure 21. Maximum Power Dissipation Derating vs. Case Temperature

Figure 22. Typical Output Current Capability vs. Switching Frequency (Inverter Application)

0

25

50

75

100

125

-50 -25 0 25 50 75 100 125 150

FET

Pow

er D

issip

atio

n, P

D(W

)

Case Temperature, TC (°C)

Conditions:TVJ ≤ 150 °C

0

10

20

30

40

50

60

-50 -25 0 25 50 75 100 125 150

Drai

n-So

urce

DC

Curr

ent,

I DS

(DC)

(A)

Case Temperature, TC (°C)

Conditions:TVJ ≤ 150 °C

Press-Fit Pin Limit

0

10

20

30

40

50

60

70

80

0 20 40 60 80 100 120 140

Out

put C

urre

nt, I

Out

(Arm

s)

Switching Frequency, FS (kHz)

VDS = 800 VTHS = 50 °CTVJ = 150 °CMF = 1RG-EXT = 0 Ω

Press-Fit Pin Limit

0

20

40

60

80

100

120

0 200 400 600 800 1000 1200

Drai

n-So

urce

Cur

rent

, IDS

(A)

Drain-Source Voltage, VDS (V)

Chip

Module (RG = 0.0)

Module (RG = 2.0)

Conditions:TVJ = 150 °C LStray-Bussing = 8.9 nHLStray-Module = 17.4 nH

Figure 23. Nominal NTC Resistance vs. NTC Temperature

10

100

1000

10000

100000

-50 -25 0 25 50 75 100 125 150 175 200

Nom

inal

NTC

Res

istan

ce (Ω

)

NTC Temperature (°C)

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

8Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Figure 25. dv/dt and di/dt vs. Source Current

Timing Characteristics

Figure 24. Timing vs. Source Current

Figure 26. Timing vs. Junction Temperature Figure 27. dv/dt and di/dt vs. Junction Temperature

tdoff

tf

tdon

tr05

10152025303540455055606570

0 25 50 75 100 125 150 175

Tim

e (n

s)

Junction Temperature, TVJ (°C)

Conditions:IS = 30 A, VDD = 600 VRG(ext) = 0.0 Ω, VGS = -4/+15 V

dv/dtOFF

dv/dtON

di/dtOFF

di/dtON

0

10

20

30

40

50

60

70

80

90

0 25 50 75 100 125 150 175

di/d

t (A/

ns) a

nd d

v/dt

(V/n

s)

Junction Temperature, TVJ (°C)

Conditions:IS = 30 AVDD = 600 VRG(ext) = 0.0 ΩVGS = -4/+15 V

tdoff

tf

tdon

tr

0

10

20

30

40

50

60

70

0 10 20 30 40 50 60 70 80 90 100 110

Tim

e (n

s)

Source Current, IS (A)

Conditions:TVJ = 25°CVDD = 600 VRG(ext) = 0.0 ΩVGS = -4/+15 V

Figure 28. Timing vs. External Gate Resistance Figure 29. dv/dt and di/dt vs. External Gate Resistance

tdoff

tf

tdon

tr

0

25

50

75

100

125

150

175

0 2 4 6 8 10 12 14 16

Tim

e (n

s)

External Gate Resistor, RG(ext) (Ω)

Conditions:TVJ = 25°CIS = 30 AVDD = 600 VVGS = -4/+15 V

dv/dtOFF

dv/dtON

di/dtOFF

di/dtON

0

10

20

30

40

50

60

70

80

90

0 2 4 6 8 10 12 14 16

di/d

t (A/

ns) a

nd d

v/dt

(V/n

s)

External Gate Resistor, RG(ext) (Ω)

Conditions:TVJ = 25°CIS = 30 AVDD = 600 VVGS = -4/+15 V

dv/dtOFF

dv/dtON

di/dtOFF

di/dtON

0

20

40

60

80

100

120

140

0 10 20 30 40 50 60 70 80 90 100 110

di/d

t (A/

ns) a

nd d

v/dt

(V/n

s)

Source Current, IS (A)

Conditions:TVJ = 25°CVDD = 600 VRG(ext) = 0.0 ΩVGS = -4/+15 V

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

9Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Figure 31. Turn-on Transient Definitions

Definitions

Figure 30. Turn-off Transient Definitions

Figure 32. Reverse Recovery Definitions Figure 33. VGS Transient Definitions

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

10Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Schematic and Pin Out

Package Dimension (mm)

Copyright ©2021 Cree, Inc. All rights reserved. The information in this document is subject to change without notice. Cree®, the Cree logo, Wolfspeed®, and the Wolfspeed logo are registered trademarks of Cree, Inc.

11Rev. 1, 2021-01-25 CCB021M12FM3 4600 Silicon Dr., Durham, NC 27703

Notes

• This product has not been designed or tested for use in, and is not intended for use in, applications implanted into the human body nor in applications in which failure of the product could lead to death, personal injury or property damage, including but not limited to equipment used in the operation of nuclear facilities, life-support machines, cardiac defibrillators or similar emergency medical equipment, aircraft navigation or communication or control systems, or air traffic control systems.

• The SiC MOSFET module switches at speeds beyond what is customarily associated with IGBT-based modules. Therefore, special precautions are required to realize optimal performance. The interconnection between the gate driver and module housing needs to be as short as possible. This will afford optimal switching time and avoid the potential for device oscillation. Also, great care is required to insure minimum inductance between the module and DC link capacitors to avoid excessive VDS overshoot.

Supporting Documents & Tools

Evaluation Tools• KIT-CRD-CIL12N-FMA: Dynamic Evaluation Board for Half-Bridge FM3 Modules• KIT-CRD-CIL12N-FMC: Dynamic Evaluation Board for Six-Pack FM3 Modules• CRD25AD12N-FMC: 25 kW SiC Active Front End (AFE)• CCB021M12FM3 PLECS Model • SpeedFit 2.0 Design Simulator™

Dual-Channel Companion Gate Driver Boards• EVAL-ADUM4146WHB1Z: Analog Devices® Gate Driver Board• Si823H-AxWA-KIT: Silicon Labs® Gate Driver Board• CGD1700HB2M-UNA: Wolfspeed Gate Driver Board• CGD12HB00D: Differential Transceiver Daughter Board Companion Tool for Differential Gate Drivers

Application Notes• CPWR-AN41: Mounting Instructions and PCB Requirements• CPWR-AN42: Thermal Interface Material Application Note• CPWR-AN45: Dynamic Performance Application Note

![[MS-VDS]: Virtual Disk Service (VDS) Protocol... · [MS-VDS]: Virtual Disk Service (VDS) Protocol Intellectual Property Rights Notice for Open Specifications Documentation](https://static.fdocuments.net/doc/165x107/5ece0e4751b19024473b3e8c/ms-vds-virtual-disk-service-vds-protocol-ms-vds-virtual-disk-service.jpg)

![RDS 323 Restorative Dental Sciences [ RDS]](https://static.fdocuments.net/doc/165x107/6235ee36aafa9c66c73cc0cf/rds-323-restorative-dental-sciences-rds.jpg)