CAPÍTULO 2 PROCESADORES SUPERESCALARES · coma flotante –1 multiplicacio nes en coma flotante ....

Transcript of CAPÍTULO 2 PROCESADORES SUPERESCALARES · coma flotante –1 multiplicacio nes en coma flotante ....

CAPÍTULO 2 PROCESADORES SUPERESCALARES

• INTRODUCCIÓN • Características de los procesadores superescalares

• Paralelismo • Diversificación • Dinamismo

• Arquitectura de un procesador superescalar genérico

Características de los procesadores superescalares

Características de los procesadores superescalares

NI

)frecuencia(IPC

ciclo de tiempo

1

ciclo

nesinstruccio

nesinstruccio de nº

1oRendimient

Los procesadores segmentados usan el paralelismo de máquina

temporal.

Un procesador superescalar usa paralelismo de máquina temporal y

espacial

SEGMENTACIONES PARALELAS

Esquema de segmentación de profundidad 5 y anchura 4

SEGMENTACIONES DIVERSIFICADAS

DIVERSIFICACIÓN-> Alpha 21264

• 6 unidades funcionales

– 2 enteros

– 2 cálculo de direcciones

– 1 sumas, divisiones y raíces cuadradas en coma flotante

– 1 multiplicaciones en coma flotante

DIVERSIFICACIÓN-> PowerPC 970

• 12 unidades funcionales

– 2 enteros

– 2 coma flotante

– 2 carga/almacenamiento

– 4 unidades especiales para instrucciones vectoriales SIMD

– 1 resolución de saltos

– 1 registros de condición o estado

• 12 unidades de ejecución 8 (se envían un máximo de 8 instrucciones)

Dinamismo en la segmentación • Permiten la ejecución fuera de orden, aprovechando

mejor los recursos. La emisión y finalización en las

distintas unidades funcionales puede ser en un orden

diferente al establecido por el programa.

• En una segmentación paralela rígida las etapas se

separan con buffers mutientrada o multipuerto

• Una segmentación dinámica paralela utiliza buffers

multientrada permite que las instrucciones entren y

salgan fuera de orden.

– Una instrucciones pueden adelantar a otras

(dependencias WAW y WAR)

– Reducción de los ciclos de detención por

dependencias RAW

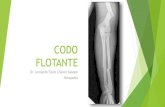

Esquema por bloques de un procesador superescalar

En el front-end y

el back-end las

instrucciones

avanzan en orden

El núcleo de

ejecución

dinámica ejecuta

fuera de orden.

Es normal

“especular”, para

realizar

predicciones sobre

que instrucciones

se ejecutarían tras

una instrucción

de salto

Arquitectura de un procesador superescalar genérico Etapa de lectura de

instrucciones (IF)

Lee hasta 4 instrucciones

Etapa de decodificación (ID)

Se decodifican en

paralelo

Etapa de

distribución/emisión (II)

Según tipo y

disponibilidad de

operandos quedan en la

estación de reserva

centralizada

Etapa de ejecución (EX)

Fuera de orden

Etapa de terminación (WR)

Escritura de resultados en

registros

Etapa de retirada (RI)

Las instrucciones de

almacenamiento

proceden a la escritura

ordenada en memoria

Procesador Superescalar Genérico

• 7 unidades funcionales

– 2 enteros

– 1 sumas/restas coma flotante

– 1 mult/división coma flotante

– 1 instrucciones almacenamiento

– 1 instrucciones de carga desde memoria

– 1 instrucciones salto

• Ancho de segmentación 4

Procesador Superescalar Genérico Estados de una

instrucción en una segmentación superescalar

• Distribuida (enviada a una estación de reserva)

• Emitida (cuando sale de la estación de reserva a una unidad funcional)

• Finalizada (abandona la unidad funcional y pasa al buffer de reordanamiento)

• Terminada (ha realizado la escritura de los resultados a los registros y actualiza estado del procesador)

• Retirada (ha realizado la escritura en memoria)

Ejemplo 1 Ciclo 1 (Para ver problemática arquitectura superescalar) Riesgo

estructural

unidad

funcional de

carga

Adelantamiento entre etapas

Ejemplo 1 Ciclo 2 (Para ver problemática arquitectura superescalar)

La operación de

almacenamiento

hace uso de la

retirada para

escribir en memoria

y mantenerla

actualizada

Ejemplo 1 Ciclo 3 (Para ver problemática arquitectura superescalar)

Resultado de la política

de predicción de saltos

que implemente el

procesador

Ejemplo 2 (Para ver problemática arquitectura superescalar)

La finalización de las instrucciones de forma desordenada puede producir la violación de

dependencias WAR. Violación WAR en i3 e i4 si R1 coincide con R2

Evitar riesgos WAW y WAR impidiendo que una instrucción posterior a otra en la secuencia

de código escriba antes. INCLUSIÓN DE CICLOS DE DETENCIÓN (pérdida rendimiento)