Block Diagram of TMS320C6000

-

Upload

akash-sethi -

Category

Documents

-

view

244 -

download

1

Transcript of Block Diagram of TMS320C6000

-

8/6/2019 Block Diagram of TMS320C6000

1/17

Block Diagram of TMS320C6000

Presented by:-

Akash Sethi102004

M-Tech (ECE 1ST Year)

-

8/6/2019 Block Diagram of TMS320C6000

2/17

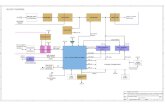

Block Diagram TMS320C6000

2

-

8/6/2019 Block Diagram of TMS320C6000

3/17

TMS320C6000 Parts

Three Main Parts:

CPU Peripherals

DMA controller

Power Management EMIF

Serial ports

Expansion bus or Host port Timers

Memory

3

-

8/6/2019 Block Diagram of TMS320C6000

4/17

Central Processing Unit

CPU contains:

Program fetch unit

Instruction dispatch unit

Instruction decode unit

Two Registers Files

Two Data paths, each with four functional units

Control registers

Interrupt logic

4

-

8/6/2019 Block Diagram of TMS320C6000

5/17

TMS320C62x CPU Data Paths

5

-

8/6/2019 Block Diagram of TMS320C6000

6/17

TMS320C67x CPU Data Paths

6

-

8/6/2019 Block Diagram of TMS320C6000

7/17

-

8/6/2019 Block Diagram of TMS320C6000

8/17

General Purpose Register Files

Two General purpose register files:

A and B Each of these files contains sixteen 32-bit registers

A0-A15

B0-B15

It can be used for data/data-address pointers.

A1,A2,B0,B1 and B2 can be used for condition

registers. A4A7 and B4B7 can be used for circular

addressing.

8

-

8/6/2019 Block Diagram of TMS320C6000

9/17

-

8/6/2019 Block Diagram of TMS320C6000

10/17

Functional Unit

Each Register files has 4 functional units:

.L, .S, .M, .D Each functional unit has its own 32-bit write port

into a general-purpose register file.

Each functional unit has two 32-bit read ports. .L unit (.L1,.L2):

It have extra 8-bit wide port for 40-bit long writes as

well as an 8-bit input for 40-bit long reads. It performs 32/40 bit arithmetic and compare

operations.

10

-

8/6/2019 Block Diagram of TMS320C6000

11/17

Contd

.S unit (.S1,.S2):

It also have extra 8-bits.

Perform 32-bit arithmetic operations, 32/40 bit shifts and logical

operation. Responsible for branching operations.

Register transfers to/from the control register file (.S2 only)

.M unit (.M1,.M2):

Performs 16 x 16 bit multiply operations. 32 x 32 bit multiply operation in case of floating-point multiply

operations

.D unit (.D1,.D2):

Responsible for all data transfers between the register files andmemory.

Performs address calculation

Loads and Stores the word or double word.

11

-

8/6/2019 Block Diagram of TMS320C6000

12/17

Control Registers

Only one unit (.S2) can read from and write to the

control register file. Some of Control Registers are:

AMR

CSR

IFR

Control Register Extension: for TMS320C67x FADCR

FAUCR FMCR

12

-

8/6/2019 Block Diagram of TMS320C6000

13/17

-

8/6/2019 Block Diagram of TMS320C6000

14/17

Memory, Load, and Store Paths

Two 32-bit paths for loading data from memory

to the register file: LD1 for register file A and LD2 for register file B. TMS320C67x also has a second 32-bit load path,

which allows the LDDW instruction to simultaneously

load two 32-bit registers. Also two 32-bit paths for storing register values to

memory:

ST1 for register file A and ST2 for register file B. The store paths are shared with the .L and .S long read

paths.

14

-

8/6/2019 Block Diagram of TMS320C6000

15/17

Data-Address Paths

The data-address paths (DA1 and DA2) coming

out of the .D units allow data addresses tosupport loads and stores to memory from the

other register file.

Loads and Stores executed in parallel must

load to and from the same register file or both

use a cross-path to the opposite register.

15

-

8/6/2019 Block Diagram of TMS320C6000

16/17

References

http://focus.ti.com

http://articles.studytemple.com

16

-

8/6/2019 Block Diagram of TMS320C6000

17/17

Queries..??

THANK YOU

16