BE/BI Technical board on Electronics choices for Fast (BLM) electronics

description

Transcript of BE/BI Technical board on Electronics choices for Fast (BLM) electronics

BE/BI Technical board BE/BI Technical board onon

Electronics choices for Electronics choices for Fast (BLM) electronicsFast (BLM) electronics

Ewald Effinger, Bernd Dehning20.03.2014

OutlineOutline• Detector overview

o Diamond Detector with Cascade Schemes (Cividec detector with copper cable)

o Optical diamond detector from CMS & DESY (BCM1F4LHC)o BLMED Installation Overview

• Motivation for a new Fast DAQo Technical Specification of Fast DAQo System propositions

• Solution CERN made or outside companyo FMC based system (BI development)o Tender System 1 – System 5

• System Compare

New Diamond Detector Cascade New Diamond Detector Cascade

SchemesSchemes

• Detector signal split in two signal paths (direct and 40dB amplified)

• Monitoring of complete dynamic range possible

• No need to access tunnel to exchange amplifier for different users

Optical diamond detector Optical diamond detector

(BCM1F4LHC) (BCM1F4LHC)

• All detector signal arrive on the same position

• Easy access of data acquisition system

• Lower dynamic range

BLMED Installation Overview BLMED Installation Overview

Acc IP Position Detector

LHC 2 BLMED.04L2.B1I10_TCTVB.4L2 CIVIDEC

LHC 3 BLMED.06L3.B1I10_TCP.6L3.B1 CIVIDEC

LHC 3 BLMED.06R3.B2E10_TCP.6R3.B2 CIVIDEC

LHC 6 BLMED.04L6.B2I10_TCSG.4L6.B2 CIVIDEC

LHC 6 BLMED.04R6.B1E10_TCSG.4R6.B1 CIVIDEC

LHC 7 BLMED.06L7.B1E10_TCHSS.6L7 CIVIDEC

LHC 7 BLMED.06R7.B2I10_TCHSS.6R7 CIVIDEC

LHC 8 BLMED.04R8.B2C10_TCTVB.4R8 CIVIDEC

SPS 4 MSE 41876 CIVIDEC

SPS 6 TPSG 61773 CIVIDEC

LHC 2 BLMED.04L2.B1C10_TDI.4L2.B1 BCM1F4LHC

LHC 8 BLMED.04R8.B2C10_TDI.4R8.B2 BCM1F4LHC

LHC 4 BLMED.05L4.B1C10_BGI BCM1F4LHC

LHC 4 BLMED.05R4.B2C10_BGI BCM1F4LHC

LHC 5 BLMED.04L5.B1I10_TCTVA.4L5.B1 BCM1F4LHC

LHC 5 BLMED.04R5.B2I10_TCTVA.4R5.B2 BCM1F4LHC

• Following detectors are foreseen to be installed while LS1 and LS2• 1 detector for Fast Servospill in the SPS TT20 (LS1)• 1 detector for HiLumi in the LHC (LS1)• 8 detectors for Booster dump (LS2)• 12 (?) detectors for PS (LS2)

Motivation for a new Fast DAQMotivation for a new Fast DAQ

• More reliability of data acquisition in compare with windows based LeCroy Scope

• Decrease rental cost for scopeso (450CHF per month and scope)

• Less complicated set up for BCM1F detectoro Supported and maintained by DESY o Complex data treatment structure

• Single data acquisition system for both detector types

• Equal readout and data treatment for both detectors

Technical Specification of Fast DAQTechnical Specification of Fast DAQ

Analogue bandwidth DC – 500 MHz V In min 10 mVpp V In max 10 Vpp 7V RMSAcquisition: Resolution 8/10/12 bit Solution specificSampling rate 1Gs/s (2.5ns – 1ns)Sampling length 10ms -1.0s @ 1Gs/s per channel selectable

Buffer @ 8 bit10k – 1G (points) = 240kbit – 24Gbit (4Gbyte) 4 Channels

Buffer@ 12 bit 10k – 1G (points) = 360kbit – 36Gbit ( 3 Channels Trigger system: Signal input Edge (Threshold set with 10bit DAC) Min. 5mVExt. Input 2 Edge TTL signalSoftware trigger On event via data transmissionHistogram: Resolution 1.55671875ns (57024 bins) Bunch length / 16Trigger threshold min. 5mV 10 bit DACCounter 20-24 bit per bin Update rate 1s Scaler: Trigger threshold min. 5mV 10 bit DACCounter 20-24 bit Update rate 1s Controller or FPGA software: Source code User accessible for modifications Preferable Drivers & Control software Driver Open source Linux PreferableControl Linux Preferable

System propositions System propositions • 8 - 10 - 12 bit

solution possible

• 3 – 4 channel per system needed

• Splitter and/or optical input

• can be separated form DAQ

• In case of a modular system more than 4 channel possible

• Parallel processing of Histogram and Loss versus time mode preferable

FMC based system (BI development)FMC based system (BI development)

• System based on BI VFC board

• Digitizer FMC board, 8/10/12 ADC 1GSPS, no memory on the board.

• VME 64 create and Linux CPU needed per system

• Not compatible with dead lines of projecto Series production of VFC (start end of 2014)o Tender for FMC card

• FPGA and CPU Software form BI needed

Tender System 1Tender System 1• Custom made MTCA 4 Channel 1.25GSPS 10bit

ADC

• Virtex 6 FPAG and DDR3 memory interface

• FPGA software done by vendor

• Create and single board computer and MCH not included (not included in the offer)

• Offer not compatible with dead line

• CPU software not mentioned

Tender System 2Tender System 2• 3 * 1 Channel 1.6GSPS 12bit ADC

• FPGA board with Kintex -7 and 2 Gbit RAM

• 2.3 GHz Quad-Core PXI Express Controller

• 8-Slot 3U PXI Express Chassis with AC - Up to 7 GB/s

• Modular system, stand alone

• Compatible with dead line

• CPU and FPGA Software consulted by vendor

Tender System 3Tender System 3• 1 * 4 Channel 1.25 GSPS 8bit ADC with Xilinx Virtex 5,

16 GB compact flash card

• 1 * 2 Channel 2.5 GSPS 8 bit ADC with Xilinx Virtex 5

• Mother board NANO-PV-D5251with Intel Atom D525 1.8 GHz and 4GB RAM, Linux based software.

• 5 Gbit/s connection between ADC and CPU .

• Compatible with dead lines

• CPU and FPGA Software included in the offer

Tender System 4Tender System 4• No specified description given in the offer

• New custom made development all requirements should be fulfilled

• Compatible with dead lines

Tender System 5Tender System 5• 1 * 4 Channel 1GSPS 12bit ADC with Virtex 6 and

1 Gbit RAM

• Analogue frontend with selectable gain

• Linux based CPU to connected to ADC and data treatment.

• 19 “ chassis, stand alone system

• CPU and FPGA Software included in the offer

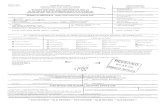

System CompareSystem Compare

SystemImportant Technical Aspects BI/BL Man power Dead

lineComments

Storage per Ch

Resolution Rate FPGA CPU

Production

BI/BL 8 MByte 10 bit 1 GSPS Yes Yes Yes No Tender for FMC neededTender

1 1.25 GByte 10 bit1.25 GSPS No Yes No No Offer is without chassis and CPU

Tender 2 2 GByte 12 bit

1.6 GSPS Yes Yes No Yes

Modular system, Onsight consualtion

Tender 3 4 GByte 8 bit

1.25 GSPS No No No Yes QT GUI exist, Future option 12 bit

Tender 4 1.5 GByte 12 bit 1 GSPS No No No Yes Completely new development

Tender 5 250 MByte 12 bit 1 GSPS No No No Yes Future option 8 Gbyte

Values in grey correspond to specified values !