Arquitecturas AvanzadasCurso 10/11 1INTRODUCCIÓN 2CONECTIVIDAD 3MÁQUINAS MIMD 4MÁQUINAS SIMD...

-

Upload

asuncion-bega -

Category

Documents

-

view

13 -

download

2

Transcript of Arquitecturas AvanzadasCurso 10/11 1INTRODUCCIÓN 2CONECTIVIDAD 3MÁQUINAS MIMD 4MÁQUINAS SIMD...

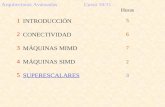

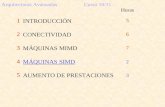

Arquitecturas Avanzadas Curso 10/11

1 INTRODUCCIÓN

2 CONECTIVIDAD

3 MÁQUINAS MIMD

4 MÁQUINAS SIMD

5 SUPERESCALARES

Horas

5

5

7

2

4

arqAva Clasificación de Flynn Ampliada MIMD-2

Arquitecturas Paralelas

SISD SIMD MISD MIMD

Multi-procesadores

Multi-computadores

MPP COW

Von Neumann

ProcesadoresVectoriales

Array de Procesadores

Sistólicos

UMA NUMACOMA

Distintas formas de organizar la memoria común

??

Beowulf

Symetric

Multi

Processor

Distributed Shared Memory

arqAva Temario MIMD-3

3 MÁQUINAS MIMD

1 Multiprocesadores• Modelos UMA, NUMA y COMA• Coherencia de cachés

• Husmeo (snoopy)• Directorios

2 Multicomputadores• Modelos MPP, COW, Beowulf

3 Procesadores multinúcleo

Bibliografía:“Advanded Computer Architecture...” Kai Hwang-1993 [19..23, 348..363]“Structured Computer Organization” A.S. Tanenbaum-1999 [564..586]“Parallel Computer Architecture …” Culler y Singh-1999 [269..301, 553..571]

arqAva Multiprocesadores MIMD-4

Un único espacio de direcciones de memoria visible a todos los µPs

50move #50,$20

P1

P2

Pn

Memoria$0000000

$FFFFFFF

100

move #100,$1000000

move $1000000,R5

25

move #25,$4000000

Pi

move

Existen distintas formas de implementar este espacio de memoria

arqAva Multiprocesadores (UMA) MIMD-5

Acceso Uniforme a Memoria: Cada Pi mismo tiempo de acceso a todas y cada una de las posiciones de memoria

Puede complicarse algo para aumentar las prestaciones

P1 P2 Pn

C1 C2 Cn

M1 M2 Mk

Bus Común

¿Coherencia?

A

A’ A

Symetric Multi Processor

• ¿Límites?• ¿Ventajas?

arqAva Multiprocesadores (UMA) MIMD-6

Ejemplo: Sun Enterprise 10000 (1998)

Crossbar de 16x16 (Gigaplane-XB) => 19,87GB*seg

0 1 15

UltraSPARC 333MHz

1 GB de memoria

coherencia cachés

Mantiene modelo UMA ¿Al límite (64µP)?

Tarjetas de40x50 cm.

¿ 2010 ?

arqAva Multiprocesadores (UMA) MIMD-7

arqAva Multiprocesadores (UMA) MIMD-8

Evolución servidores gama alta de SUN con UltraSPARC

..12 ..24

..52

..106

..36 ..72† Hasta

8/01/2009

arqAva Multiprocesadores (UMA) MIMD-9

Evolución servidores gama alta de SUN con SPARC64 VI y VII

M4000 ..16 M5000 ..32 M8000 ..64 M9000 ..256

arqAva Multiprocesadores (UMA) MIMD-10

Ejemplo: SPARC Enterprise M9000 => 64 SPARC64 VII

¿Coste?

368,5GB/s 368,5GB/s

8 Placas4 CPU’s4 núcleos2 Threads

Hasta 2TB

2,52GHz64KB L1 I64KB L1 D

6MB L2

arqAva Multiprocesadores (UMA) MIMD-11

Ejemplo: SPARC M9000 Con descuentos => 3.298.483$www.tpc.org/tpch Oct/2010 #2 3.000GB Results

Latencias (Sun Fire E25K)Misma placa => 180..207 nsegOtra Placa => 333 , 440 nseg

¿UMA?

2009..2010 Compra SUN

2.841.219$

32 SPARC64 VII

512GB memoria

963.234$

78TB

1.416.010$

Mantenimiento 1.376.503$

arqAva Multiprocesadores (NUMA) MIMD-12

Acceso No Uniforme a Memoria: El acceso a memoria remota es más lento que el acceso a memoria local

1. Tlocal (P1,M1)

M1 P1

Mn Pn

M2 P2

R

e

d

2. Tremoto (Pn,M2)

Red Global

M1

M2

Mn

Red

P1

P2

Pn

M1

M2

Mn

Red

P1

P2

Pn

MG1 MG2 MGk

1. Tlocal 2. Tglobal 3. TremotoMás procesadoresDistributed Shared Memory

arqAva Multiprocesadores (NUMA) MIMD-13

Todavía dentro de NUMA, se contemplan dos modelos

M1 P1

Mn Pn

M2 P2

R

e

d

NC-NUMA

Sistemas sin cachés

CC-NUMA

P1

C1 M1

Pn

Cn Mn

P2

C2 M2

Red de interconexión

Sistemas con Cachés Coherentes

A AA’

IBM Power 795

arqAva Multiprocesadores (CC-NUMA) MIMD-14

Ejemplo: Sequent NUMA-Q 2000

Tarjetas con4 Pentium Pros

y hasta 4GB

Anillo SCIHasta 64K nodos

El más grande (199?):

63 nodos (252µP)

238Bytes (256GB)

CoherenciaCachés

arqAva Multiprocesadores (COMA) MIMD-15

Acceso sOlo a Memoria Caché: Es un submodelo de NUMA, donde la memoria principal de cada procesador, se trata como una caché.

NUMA => Un dato está asignado de forma estática a una memoria local determinada => Muchos accesos remotos (lentos)

A

Memoria Virtual

Una solución: Los datos se ubican dinámicamente en las memorias de los procesadores que los demandan

A A

¿Dónde está A?

¿Expulsar A? ACnC1 C2

RED

P1 P2 Pn

arqAva Coherencia de CachésMIMD-16

Conceptos que se presupone conocidos:

•Concepto de caché y su ubicación en la jerarquía de memoria

•Distintos modelos:AsociativaCorrespondencia directaAsociativa por conjuntos

•Políticas de reemplazo (Azar, LRU, ...)

•Políticas de escritura:

Acierto: Escritura Inmediata “Write Through”Escritura Diferida “Write Back”

Fallo: No ubicar al escribirUbicar al escribir

MP 4GBL2 2*4MBLínea 64 Bytes

arqAva Coherencia de CachésMIMD-17

XX ------------------------ XXXX ------------------------ XXXX ------------------------ XXXX ------------------------ XX

YY --------- D3BC ------- YY

XX ------------------------ XXXX ------------------------ XXXX ------------------------ XXXX ------------------------ XX

012 --------- 4567 ------------ F 2222 3

00000000

00000040

00000080

000000C0

00400800

FFFFFFC0

FFFFFF80

FFFFFF40

FFFFFF00

ld $00400824, R5

Bloque Desp

26 6 2222 3012 --------- 4567 ------------ F

YY --------- D3BC ------- YY00400800

Etiqueta Desp 26 6

• Asociativa 004008 00 10 4

26

0000

0001

0020

2222 3012 --------- 4567 ------------ F

0001

• Correspondencia directa

YY --------- D3BC ------- YY

Eti Desp 10 16 6

Líneald $00400824, R5

FFFF

00 008 00 10 400 01

10

arqAva Coherencia de CachésMIMD-18

Problemática con: Datos compartidos

Problemática con: Migración de procesos

P1

X’

P2

X

cachés

MP

P1

X’

P2

X

P1

X’

P2

X

X

WriteBack

P1

X

P2

X

X

cachés

MP

P1

X’

P2

X

X

Write Back

Write Through

P1

X’

P2

X

X’

P1.W

¡P2.R!¡P3.R!

¡P2.W!

¿Write Through?

arqAva Coherencia de CachésMIMD-19

Problemática con: Entrada / Salida

P1

X

P2

X

X

cachés

MP E/S

P1

X

P2

XWrite

Through

XX’

P1

X’

P2

X

X

Write Back

X’ input X output

¿Solución?:

Snoopy: Para sistemas basados en busCotillear, espiar la actividad del bus

Directorios: Para redes estáticas, multietapa, etc.Directorios cachés que indican en

qué cachés hay copias de los datos

BUS

arqAva Coherencia de Cachés (Snoopy) MIMD-20

El espionaje no debe retardar el ciclo de bus (Hw adicional)

P1

C1

VTD

BUS

P2

C2

VTD

Pn

Cn

VTD

M.P. E/S

3FA4548ABC3FA45

100

Válida Tag Línea de Datos

$3FA456

VTEspía

VTEspía

VTEspía

Actualización

P1 P2 Pi Pn

X’ XX Y

X Y

P1 P2 Pi Pn

X’ XX Y

X Y

Invalidaci

ón

arqAva Coherencia de Cachés (Snoopy) MIMD-21

Para conseguir coherencia, básicamente hay dos políticas:

P1 P2 Pi Pn

X XX Y

X Y

X’ Y

CachésWriteThrough

X’ Y

X’X’

¿Mejor?

W* => 1 Inv.

Inv. Línea 64BAct. Dato (1..8)B

WriteBack

arqAva Coherencia de Cachés (Snoopy) MIMD-22

Protocolo 1: Caché de escritura inmediata e invalidación

•Cada bloque en uno de dos estados (Inválido, Válido)

•Cuando Pi va a escribir, se adueña del bus y:•Manda señal de invalidar•Escribe en M.P.

Diagrama de Estados

Ri/j => Pi/j lee bloqueWi/j => Pi/j escribe bloqueZi/j => Pi/j reemplaza bloque

INV VALRj,ZiWj,Zj

Zi,Wj

Ri,Wi

Ri,WiRj,Zj

Idea => La M.P. siempre coherente con las copias válidas en caché

Pega => Mucho tráfico en el bus (Cada W en caché => W en M.P.)

Ubicar en escritura

arqAva Coherencia de Cachés (Snoopy) MIMD-23

Protocolo 1: Comportamiento ante (Read/Write)+(Hit/Miss)

C1 C2 C3

MPA

RM: La MP suministra el bloque

C1

AC3

A

RH: La caché suministra el dato

C1

A’C2 C3

A

MPA

WH: W en MP e Invalidar

MPA’

WM: Como WH o puede que:RM + WH (ubicar en W)

C2

A’C2

A’’

MPA’’

P1RP3R

(P1R | P3R)*

P1W

P2W

arqAva Coherencia de Cachés (Snoopy) MIMD-24

Protocolo 2: Caché de escritura diferida e invalidación (propietaria)

•Conseguir que W* => Una única Invalidación•El estado VAL se desdobla en dos:

ReadOnly (Shared) ReadWrite (Modified)

C1

A

MPA

C2 C3

•Escritura => Invalidar y pasar a RW

•¿Read/Write miss?

P2W

¿Señales Bus?

A A

•Copia/s en cachés y MP coherentes•Lecturas locales sin tráfico de bus

MP propie-taria de A

Read H

it

C1

A

MPA

C2

A’C3

A

Write

Hit

•Copia única en la caché

MC propie-taria de A’

•R/W locales sin tráfico bus

arqAva Coherencia de Cachés (Snoopy) MIMD-25

Protocolo 2: Comportamiento ante fallo de lectura o escritura

C1

AC2 C3

MPA

RO: La MP suministra el bloque

ReadMiss

C2

A

: La C2 suministra el bloque RW

C2

A’

Se regresa a RO (W en MP)

C3

A’

MPA’

WriteMiss

C2

A’C3

A’

MPA’

C1

RO: La MP suministra el bloque

C1

A’

RW

C1

A’’

: La C1 escribe en MP La C3 toma la propiedad

C3

A’’’

MPA’’

P2RP2WP3R

P1WP3W

arqAva Coherencia de Cachés (Snoopy) MIMD-26

Protocolo 2: Diagrama de transición de estados

INV

RW RORi,Wi

Zj

Wi

Rj

Rj,WjZi,Zj

Wi

Ri,RjZj

Ri

Wj,ZiWj,Zi

Idea => Consistencia con el modelo de caché de escritura diferida

Pega => Tráfico innecesario en el busPrimer W en caché => INV siempre (¿No hay copias?)

arqAva Coherencia de Cachés (Snoopy) MIMD-27

Protocolo 3: MESI (Pentium, PowerPC, ...) ¿Goodman 1983?

•Como Protocolo 2, pero sin invalidar si no hay más copias

•El estado RO se desdobla en dos: “E” sólo una copia o “S” varias

Modificado:Bloque en caché modificado y única copia

Exclusivo: La única copia en caché, consistente con MP

Shared: Hay una o más copias en otras cachés y en MP

Inválido: El bloque no tiene datos válidos en la caché•El comportamiento es el siguiente:

C1

AC2 MP

AC3

P1 lee bloque A (P1R)

E

P2R C1

AC2

AMPA

C3

S S

arqAva Coherencia de Cachés (Snoopy) MIMD-28

Protocolo 3: MESI (Seguimiento de su comportamiento)

P2WC1

AC2

AMPA

C3

S S

C1

AC2

A1

MPA

C3

MI

P3R

C1

AC2

A1

MPA1

C3

A1

SI S

C1

AC2

A2

MPA1

C3

A1

MI I

P2W

P1W

C1

A3

C2

A2

MPA2

C3

A1

IM I

arqAva Coherencia de Cachés (Snoopy) MIMD-29

Protocolo 3: Diagrama de transición de estados MESI

M

S

I

E

Rj,Wj

WjRj

Wi

Wi

Ri,Wi

Ri

Ri,Rj

Wj

WiRi

WjRi Rj

¿ Mereció la pena ?

Intel QuickPath Interconnect

Source Snoop MESIFF: Cache to Cache

arqAva Coherencia de Cachés (Directorios) MIMD-30

Con decenas/cientos de procesadores, no hay bus común

•¿Aplicable coherencia por husmeo?

•Si N = 36, lo normal es que nohaya 35 copias en 35 cachés (2..5)

Solución => Informar (comando/mensaje) sólo a los nodos cuyascachés contengan una copia del dato accedido (R/W)

CM

=> Difusión (inviable con N grande)

centralizado

1976 Tang

distribuido

1978 Censier ...

limitados encadenadoscompletos1990 Chaiken ...

Directorio

arqAva Coherencia de Cachés (Directorios limitados)MIMD-31

Mtotal = 232 => 4GB Mlocal = 224 => 16MBMcache = 220 => 1MB con líneas de 64B Nodo Bloque Offdr =>

8 18 6

Limitación => Sólo una copia (bien en ML o bien en una caché)

Red de interconexión

P0 M0

Nodo 0

P1 M1

Nodo 1

P255 M255

Nodo 255

Nodo 1 desea leer dato A en $FF000504 => Nodo 255, bloque 20, off 4

En caché 1 En Nodo 255 (C | M) En Nodo i (C)

Nodo 1 le pide el dato al Nodo 255

arqAva Coherencia de Cachés (Directorios limitados)MIMD-32

Red de interconexión

P0 M0

Nodo 0

P1 M1

Nodo 1

P255 M255

Nodo 255

Nodo 1 Nodo 255A(255:20:4) A

M255

C255

Ci

directorio

1 255 1 0

A AA

Tamaño directorio:

218 * 9 = 288KB

1,76% de 16MB

Anfitrión

0

0

218-1

C Nodo

20

1 8

P0 M0

Nodo 0

P1 M1

Nodo 1

P255 M255

Nodo 255

arqAva Coherencia de Cachés (Directorios limitados)MIMD-33

N1 lee A(255:20:4):

•N1 no la ve en su caché

AA

•N1 pide A a N255

•N255 consulta directorio

0

•N255 actualiza directorioy suministra A desde M255

N1 escribe A’(255:20:8)

A’

N0 lee A’(255:20:4):

•N0 no la ve en su caché•N0 pide A’ a N255

•N255 consulta directorio

1 1

•N255 actualiza directorioy redirige petición a N1

1 0

•N1 suministra A’ desde C1

A’

1 11 0

Coherencia trivial (Sólo una copia en el sistema)

Atómico

arqAva Coherencia de Cachés (Directorios completos)MIMD-34

Para permitir más de una copia en caché (sean 3), ¿Directorio?:

Tamaño directorio (supuestos 255 nodos):

218 * (2+3*8) = 832KB

5,08% de 16MB

Para permitir copia en cualquier caché, ¿Directorio?:

E 1 2 3 4 5 255

S 0 1 0 1 0 1------------ => 8MB 50%

Se complica el mantenimiento de la coherencia

USMS

20352

3

255 4

E Nodos Estado => Necesario para coherencia:

Uncached, Shared y Modified

2 8 8 8

0

218-1

No es escalable en cuanto a ocupación adicional de memoria

arqAva Coherencia de Cachés (Directorios completos)MIMD-35

C1

A

C2

A

C3

AM255P255

Nodo 255

S 1 1 1 0 0 ------- 0 A

N3 desea escribir A’:

S SS

•N3 ve que no tiene la propiedad•N3 pide exclusividad a N255

•N255 enviará mensajes parainvalidar copias en N1 y N2

U U

•N1 y N2 responderán a N255que invalidaron sus copias

•N255 envía permiso W a N3

y actualiza directorio

M 0 0 1 0 0 ------- 0

•N3 recibe permiso, escribe y

envía confirmación a N255

A

•N255 da por finalizada latransacción

M 0 0 1 0 0 ------ 0

M

A’

¿ N1.R => A’ ?

arqAva Coherencia de Cachés (Directorios completos)MIMD-36

Ejemplo: DASH Univ. Standford, 1992 => SGI Origin 2000 $$$$

0 1 32

7654

111098

12 13 14 15

MemCPUcaché

Cluster

Snooping

directorio E: U,S,M

S0 1 0 0 0 1 0 0 0 1 0 1 0 0 0 1

0 1 2 15 Interclusterinterface

¿ Escalable ?

arqAva Coherencia de Cachés (Directorios completos)MIMD-37

• Los directorios completos no son escalables:

E 1 2 3 4 5 255

S 0 1 0 1 0 1------------ 8MB 50%

N1

P1 M1

N7

P7 M7

E 1 2 3 4 5 63

S 0 1 0 1 0 1------------ 2MB 12,5%

=> 288KB 1,8%

E 1 2 3 4 5 6 7

S 0 1 0 1 0 0 0

N63

P63 M63

N255

P255 M255

Cada nuevo nodo: ensanchar un bit

todos los directorios

arqAva Coherencia de Cachés (Directorios encadenados)MIMD-38

• Los directorios completos llenos de ceros:

2 6405 8 255

1

• ¿Cómo implementar esta visión del directorio?:

• Ahorrar memoria• Normalmente pocas copias de un dato• Ocasionalmente un dato puede estar en todas las cachés

1 2 3

45

7

254255

6

CabeceraDirectorio

Encadenado

0 1 0 0 0 1 0 0 0 ..........0 0 0 1 0 0 0 0 0 ..........0 0 0 0 0 0 0 0 0 ..........0 0 0 0 1 0 0 1 0 .........1

1 0 0 0 0 0 0 0 0 ..........

1 2 3 4 5 6 7 8 9 255EN35

1 1 1 1 1 1 1 1 1 .........1

arqAva Coherencia de Cachés (Directorios encadenados)MIMD-39

1ª aproximación: Cabecera y directorio centralizados en cada nodo

2 6405 8 255

1

1 2 3

45

7

254255

6

N35

M35

N35

P35

A

N2

M2P2 P6

A

N6

M6

A

2

Cab

●6Dir

B

5

8

255 ●

nodo bloque off

8 18 6

35:0:4A : $23000004

Cache de 218 entradas: una por bloque

Cache de ¿? entradas: ¿3 por bloque?

B : $230000BA 35:3:A

Gestión libre y

punteros

Mtotal = 232 => 4GB Mlocal = 224 => 16MB Mcache = 220 => 1MB con líneas de 64B

arqAva Coherencia de Cachés (Directorios encadenados)MIMD-40

Una solución: Cabecera centralizada y directorio distribuído

• ¿Tamaño del directorio? Número de líneas en las caches

Mtotal = 232 => 4GB Mlocal = 224 => 16MB Mcache = 220 => 1MB con líneas de 64B

• ¿Cómo formar las listas?

35:16404:4

C 2 6 35

C : $23100504

nodo bloque off 8 18 6

tag línea off 12 14 6

Cabecera 218

2

N35 P35M35

C

N2 P2 M2

C

N6 P6 M6

CC

16404

Directorio Encadenado Distribuído 214

561:20:4

206 35200

20

?

arqAva Coherencia de Cachés (Directorios encadenados)MIMD-41

Veamos el funcionamiento:

C 2 6 35

C:$23100504 35:16404:4 561:20:4nodobloque

taglínea

S 2

E Cab

561 6

Tag Sig

561 35

Tag Sig

561 0

Tag Sig

N35 N2 N6

¿N1 lee C? Miss + Pedir C a N35 + Inclusión por cabecera

561 2

Tag Sig

N1

1

arqAva Coherencia de Cachés (Directorios encadenados)MIMD-42

Veamos el funcionamiento: C:$23100504 35:16404:4 561:20:4nodobloque

taglínea

S 2

E Cab

561 6

Tag Sig

561 35

Tag Sig

561 0

Tag Sig

N35 N2 N6

¿N1 lee D:$23200510

561 2

Tag Sig

N1

1

35:32788:16562:20:16

¡ Por la misma entrada compiten

212 bloques !

1S

?

arqAva Coherencia de Cachés (Directorios encadenados)MIMD-43

Veamos el funcionamiento: C:$23100504 35:16404:4 561:20:4nodobloque

taglínea

S 2

E Cab

561 6

Tag Sig

561 35

Tag Sig

561 0

Tag Sig

N35 N2 N6

D : $23200510

562 0

Tag Sig

N1

2

1S

¿N35 escribe en C? Tamaño Cab+Dir

360K => 2,20%¡ Invalidar copias existentes !

Cab

A E Tag S A E Tag S A E Tag S

6 7 13 6

arqAva Coherencia de cachés (Directorios Encadenados)MIMD-44

Ejemplo: Sequent NUMA-Q 2000Tarjetas con

4 Pentium Prosy hasta 4GB

Anillo SCIHasta 64K nodos

Cabecera

Caché 32MB

Dir. Enc.

226 entradas4GB

219 entradas32MB

Estadosestables y

transitorios

Snoopy

Intel QuickPath Interconnect

Home Snoop MESIF

arqAva Multicomputadores MIMD-45

Cada Pi con memoria privada inaccesible a los demás (load/store)

M. Distribuida (Multicomputador)

M P M P M P

M P M P

M P M P M P

Red

Los Pi se comunican mediante el envío y recepción de mensajes

Hace atractivo a losmultiprocesadores

Hace más escalable a losmulticomputadores

64 Sun E 10000

256 Sun M9000

30.508 Cray XT4

224.162 Jaguar Cray XT5

arqAva Multicomputadores (MPP) MIMD-46

MPP => Procesadores Masivamente Paralelos

Red localDiscos y E/S

Red de interconexión de altas prestaciones

Red localDiscos y E/S

UCPs Memoria Nodos

ProcesadorComunicación

•µP comerciales: Intel EM64T, IBM Power, AMD x86_64

•Red de interconexión propietaria y de altas prestaciones

•Baja latencia y elevado ancho de banda

•Gran capacidad de E/S (Terabytes..Petabytes)

•Tolerancia a fallos (Probable que falle un µP a la semana)

¡Cambios acelerados!

arqAva Multicomputadores (MPP) MIMD-47

Ejemplo: Iniciativa ASCI => ASC

arqAva Multicomputadores (MPP) MIMD-48

Ejemplo: Intel/Sandia Red (Dic/1996..Sep/2005)

4608 procesadores:4536 cómputo32 servicios32 discos6 red2 bootstrap

3238

2

PentPro

64MB

PentPro

E/S NIC

PentPro

64MB

PentPro

E/S NIC

Kestrel board

Otro plano

Kestrelboard

•6 enlaces paralelosa 400MB/seg

•Nodos de E/S con640 discos (1TB)

ASCI-Q

arqAva Multicomputadores (COW) MIMD-49

COW/NOW => Cluster / Network Of Workstations

•Estaciones de trabajo (PC’s, iMac’s, etc...) conectadas en redcomercial (Ethernet (Fast, Giga), FDDI, ATM, etc...)

•Aprovechar los tiempos muertos decientos de máquinas de una organización

•Coste prácticamente cero

•Software para distribuir aplicaciones:PVM, MPI

•Rendimiento moderado y uso limitado

distribuídos centralizados

•Máquinas dedicadaspara aplicacionesespecíficas

www.beowulf.org

arqAva Multicomputadores (COW) MIMD-50

Beowulf => Conjunto de nodos minimalistas aglutinados en red

•Verano de 1994 en el CESDIS (16DX4 con Ethernet)

•Todos sus componentes son de costes mínimos:Micros, Placas Base, Discos y Tarjetas de red

y se ensamblan en uno o varios armarios (racks)

•Software de libre distribución (Linux, GNU, PVM, MPI)

•Latencia de comunicación acotada y baja (MPPs..COWs-Distri.)

•Hágaselo usted mismo

•Afinamiento del S.O. para incremetar la eficiencia

arqAva Multicomputadores (MPP vs Beowulf) MIMD-51

84,8%

14,8%

arqAva Multicomputadores (MPP vs Beowulf) MIMD-52

ASCI Q (Febrero/2002) McKenzie (Enero/2003)www.cita.utoronto.ca/webpages/mckenzie/index.htmlwww.lanl.gov/projects/asci

256 nodos Xeon 2,4 GHz * 2Linux RedHat 7.3, GigaEthernet

1,2 Teraflops * 100 mPts

2048 nodos AlphaServer * 4 => 819213,9 Teraflops

29.000 millones de pesetas

arqAva Multicomputadores (MPP vs Beowulf) MIMD-53

Advanced School for Computing and Imaging

5 Universidades holandesas:

• Andy Tanenbaum (DAS1)

• 92..340 792 núcleos

• AMD Opteron 2,2..2,6GHz

• 3..10 33TB RAM

• 130TB disco

• Myri-10G y 1-10GigaEthernet

• Scientific Linux 5

www.cs.vu.nl/das3/ Distributed ASCI Supercomputer

2007 †

Medalla IEEE 2007

arqAva Multicomputadores (MPP vs Beowulf) MIMD-54

Red Hat Enterprise Linux 5, …10Gigabit Ethernet, InfiniBand

Hasta 1024 nodos (4 | 6 procesadores)

Intelligent Cluster

http://www-03.ibm.com/systems/x/hardware/rack/x3650m3/index.html

1 / 2 Intel Xeon Six Core ..3,33 GHz

1x2,26GHz + 4GB + 500GB => 5.483$

arqAva Multicomputadores (MPP vs Beowulf) MIMD-55

www.microway.com www.hp.com www.penguincomputing.com

2....20 Xeon 4Hasta 16 Itaniumx2..84 Intel Xeon 4 | 6

arqAva Multicomputadores (MPP vs Beowulf) MIMD-56

21 servidores SupermicroIntel Core 2 Q6600

2,4GHz + 4GB

84 núcleos + 84GB

20.600€ 21 servidores1.000€ armario

Sep/2008

arqAva Multicomputadores (Alta disponibilidad) MIMD-57

www-1.ibm.com/servers/esdd/tutorials/clustering

Tipo de negocio Impacto por hora de caída

Centro de reservas aéreas 89.500$

Operaciones bursátiles 6,45 millones $

Venta por catálogo 90.000$

Autorización tarjetas de crédito 2,6 millones $

Canales de venta de hogar 113.750$

Servicio de paquetería 150.250$

¿Regla de los cinco nueves?

9 90% sin fallos

99 99%

999 99,9%

99999 5,39’ caído al año

?

www.intel.com/pressroom/kits/quadcore

arqAva Procesadores Multinúcleo (Intel) MIMD-58

• ¿Por qué varios núcleos?

∆ F

• ConsumoDin = C * A * V2 * F

arqAva Procesadores Multinúcleo (Intel) MIMD-59

• Trabajar con frecuencias más bajas y …

? + rendimiento

arqAva Procesadores Multinúcleo (Intel) MIMD-60

• Multinúcleo Mejores rendimientos esperados

2006 cumpliéndose espectativas

?

arqAva Procesadores Multinúcleo (Intel) MIMD-61

• Dos pequeños mejor que uno grande

arqAva Procesadores Multinúcleo (Intel) MIMD-62

• ¿Qué procesadores están en marcha?

2010

arqAva Procesadores Multinúcleo (Intel) MIMD-63

• ¿Qué procesadores están en marcha [roadmap]?

11 Marzo 2010Core i7-980X 999$

arqAva Procesadores Multinúcleo (Intel) MIMD-64

• ¿Qué aspecto tienen?

Caches independientes

Sm

art C

ache

arqAva Procesadores Multinúcleo (Intel) MIMD-65

• Cache compartida vs independiente

arqAva Procesadores Multinúcleo (Intel) MIMD-66

• Intel Core 2 Extreme QX6700 (4 núcleos a 2,66 GHz)

Smart Cache

4MB

Smart Cache

4MB

399€Core 2 Quad Q8300 + 4GB + 500GB

arqAva Procesadores Multinúcleo (Intel) MIMD-67

• Intel Core i7

962 €Mayo/2009: Core i7 920 + 6GB + 500GB

arqAva Procesadores Multinúcleo (Intel) MIMD-68

• Intel Core i7-980X

arqAva Procesadores Multinúcleo (Intel) MIMD-69

• Intel Core i7-980X

arqAva Procesadores Multinúcleo (AMD) MIMD-70

• AMD Quad-Core Phenom X4

arqAva Procesadores Multinúcleo (AMD) MIMD-71

• AMD Quad-Core Phenom (Jerarquía de caches)

L1I 64KBL1D 64KB

arqAva Procesadores Multinúcleo (AMD) MIMD-72

• AMD Quad-Core Phenom ¿Bueno, bonito y barato?

Consumo

Phenom AMD Quad 9850 + 4GB + 1TB 680 €

arqAva Procesadores Multinúcleo (AMD) MIMD-73

• AMD Six-Core Istanbul [server] y ¿desktop Thuban 2010?

arqAva Procesadores Multinúcleo (AMD) MIMD-74

• AMD Six-Core: Thuban Phenom II X6

arqAva Procesadores Multinúcleo (AMD) MIMD-75

• Roadmap

arqAva Procesadores Multinúcleo (IBM) MIMD-76

• Agosto/2009: IBM presenta el POWER 7 [8 núcleos]

256KB L2 * núcleo + 32MB L3 compartida

CELLSPARC T3

arqAva Procesadores Multinúcleo (Oracle) MIMD-77

• 20/Sep/2010: Oracle presenta el SPARC T3 [16 núcleos: 128Threads]

6MB L2

18.639$

arqAva Procesadores Multinúcleo (Tilera) MIMD-78

• 26/10/2009 => Tilera [TileGx]: www.tilera.com

16, 36, 64, 100 cores – 1..1,5 GHz - 32K L1I , 32K L1D . 256K L2

arqAva Procesadores Multinúcleo (Coherencia) MIMD-79

• Cache compartida: Bus vs Red

UMA UCA NUMA NUCA

arqAva Procesadores Many-core (Intel) MIMD-80

• Mayo 2010: Intel lanza de forma selectiva el SCC [prototipo]

48 IA-32núcleos

Memoria común sin coherencia Sw

http://techresearch.intel.com/spaw2/uploads/files/SCC_Platform_Overview.pdf

arqAva Procesadores Multinúcleo (Pegas) MIMD-81

• Multicore Is Bad News for Supercomputers. Samuel K. Moore – IEEE SPECTRUM Nov-2008

arqAva Procesadores Multinúcleo (¿Solución?) MIMD-82

• Intel Technology Journal, Volume 11, Issue 3, 2007

FIN