A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

-

Upload

maheshmahe -

Category

Documents

-

view

223 -

download

1

Transcript of A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

1/11

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 49, NO. 4, APRIL 2014 961

A Time-Based Pipelined ADC Using Both

Voltage and Time Domain InformationTaehwan Oh, Member, IEEE, Hariprasath Venkatram, Member, IEEE, and Un-Ku Moon, Fellow, IEEE

AbstractIn this paper, a Nyquist ADC with a time-basedpipelined TDC is proposed. In the proposed ADC, the firstpipeline stage incorporates both residue amplification and a V-Tconversion with high accuracy, efficiently realized by a low gainamplifier with only 24 dB dc gain. Furthermore, adding to power

efficiency, a hybrid time-domain pipeline stage based on simplecharge pump and capacitor DAC in its backend stages is alsoproposed. Using the right combination of voltage and time do-main information, the proposed ADC architecture benefits from

improved resolution and power efficiency, with MSBs resolved involtage domain and LSBs in time domain. The measured results of

the prototype ADC implemented in a 0.13 m CMOS demonstratepeak SNDR of 69.3 dB at 6.38 mW power and 70 MHz sampling

frequency. The FOM based on peak SNDR is 38.2 fJ/conver-sion-step.

Index TermsPipelined analog-to-digital converters, time do-main, time-to-digital converters, voltage domain, voltage-to-timeconversion.

I. INTRODUCTION

H IGH resolution and wide signal bandwidth with lowpower consumption are preferred specifications ofADCs used in a variety of applications. For high resolution

and wide bandwidth, the pipelined ADCs, which employ a

residue amplifier with high open loop gain in a conventional

voltage domain, have been widely used for many decades.

However, it is more challenging to design a pipelined ADC in

the advanced deep sub-micron processes due to the reduced

supply voltage and intrinsic gain of the device. It is difficult to

reduce the power consumption of the pipelined ADC due to the

need for an accurate amplifier, which consumes large power in

general. The SAR architecture is a good alternative to achieve

a better power efficiency, but it still needs a power hungry

Manuscript received August 17, 2013; revised October 21, 2013; accepted

November 19, 2013. Date of publication December 18, 2013; date of currentversion March 24, 2014. This paper was approved by Guest Editor Hideyuki

Kabuo. This work is supported by CDADIC and partly by SRC.

T. Oh was with the School of Electrical Engineering and Computer Science,Oregon State University, Corvallis, OR 97331 USA, and is now with Tektronix,

Inc., Beaverton, OR 97077 USA.H. Venkatram was with the School of Electrical Engineering and Computer

Science, Oregon State University, Corvallis, OR 97331 USA, and is now withIntel Corporation, Hillsboro, OR 97124 USA.

U. Moon is with the School of Electrical Engineering and Computer Science,

Oregon State University, Corvallis, OR 97331 USA.Color versions of one or more of the figures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2013.2293019

residue amplifier to achieve high resolution (in a multi-stage

architecture) [1], which is less power efficient and difficult to

design in reduced supply voltage. While there are many ways

to reduce power consumption of the ADC by using a simple

low gain amplifier with relatively low power consumption, it

is not easy to correct nonlinear amplifier errors. Furthermore,

the nonlinear error becomes worse with process scaling, due to

the difficulty in maintaining a moderate signal swing at lower

supply voltage.

Recently, time-domain quantizers have drawn attention in

advanced CMOS processes as a viable candidate for power

efficient ADC architecture [2][4]. In order to increase the

resolution in time domain, a time amplifier is employed in

multi-stage architectures [5][7]. However, these approaches

need complex calibration to correct the time amplifier nonlin-

earity. Other approaches using a linear current source for the

time amplification have been reported in [8][10]. Although

these designs show power-efficient data conversion utilizing

time-domain signal processing without an expensive residue

amplifier, they are restricted in performance, offering either

low bandwidth [8] or limited resolution [9], [10]. The accuracy

of the TDC can be improved with time amplification, but the

resolution solely in time domain is limited in general and not

comparable to the resolution of the state of the art ADC involtage domain.

In this paper, a hybridpipelined ADC which uses both voltage

and time domain information is proposed [11]. The proposed

ADC employs a new voltage-to-time conversion scheme using a

scalable, power efficient, residue amplifier with minimal dc gain

in its first stage while maintaining high linearity. This scheme

not only reduces the power consumption of the ADC but also

relaxes the design trade-off of the amplifier in a low supply

voltage deep sub-micron process without sacrificing bandwidth.

Also, the power efficiency and linearity of the proposed ADC

are further improved by the hybrid time-domain pipeline stage,

which employs a simple charge pump and capacitor DAC forthe time residue amplification and quantization in the backend

pipeline stages.

This paper is organized as follows. In Section II, utilization

of time domain information in a high resolution pipelined ADC

is briefly discussed. Section III presents the proposed pipelined

ADC incorporating a new - conversion scheme and a hybrid

time-based pipeline stage. The implementation details and de-

sign considerations of non-idealities are followed in Sections IV

and V, respectively. Finally, measurement results are provided

in Section VI, followed by conclusions in Section VII.

0018-9200 2013 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications_standards/publications/rights/index.html for more information.

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

2/11

962 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 49, NO. 4, APRIL 2014

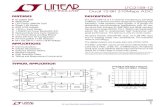

Fig. 1. Example of the time amplification and quantization using charge pump.

II. UTILIZING TIME DOMAIN INFORMATION

FORHIGHRESOLUTION ADC

Efficiently resolving bits and pipelining the quantization error

requires robust and accurate residue amplification in time do-

main. Fig. 1 shows one possible way to achieve such residue

amplification similar to the time amplification in [8]. Based on

a simple charge pump design, the time input can be amplifiedby

using different slopes applied for charging and discharging. By

measuring the discharging time for the zero-crossing, utilizing

current sources with different ratio, the input time can be ampli-

fied. In this example, the amplified output time with the gain of

4 is calculated as the following equation:

(1)

The amplified time input signal is quantized based on a time ref-

erence and the time-domain quantization error can be generated.

Similar to a conventional pipelined ADCin a voltagedomain,

this amplifi

cation scheme can be applied to process a time-do-main signal in a pipelined architecture as shown in Fig. 2. After

the reset phase, the time input ( ) is quantized by the sub-

TDC,which generates the digital outputand DAC pulse ( )

for residue generation. As shown in Fig. 3, is gener-

ated according to from the time reference ( ) during

the quantization. Then, the time-domain residue ( - ) is

amplified by 4 with a different current ratio of 4:1 for charging

and discharging in this example. After the zero-crossing com-

parison, the time-domain residue output ( ) is generated

for further quantization in the next pipeline stage. With time-do-

main residue amplification and its simple open loop configura-

tion, further quantization is possible to extract higher resolution

with relatively low power consumption.

Fig. 2. Pipelined TDC example with time-domain pipeline stage.

Fig. 3. Time residue amplification and quantization of the time-domainpipeline stage.

III. PROPOSED HYBRIDVOLTAGE AND TIME DOMAIN

PIPELINED ADC

A. Proposed ADC Architecture

Shown in Fig. 4 is the proposed hybrid voltage and time-

based pipelined ADC. It consists of a conventional 4 bit MDAC

and a FLASH in voltage domain, a zero-crossing comparator

for - conversion, four time-domain pipeline stages (TSTGs)

and a 2.5 bit TDC for backend pipelined stage, and other sup-

porting blocks. With a 1 bit redundancy between the pipeline

stages, the ADC generates a 14 bit digital output. - tracking

block, which provides a coarse current reference to the - con-

verter in the MDAC and TSTGs, tracks the relation between

the voltage and time domain gain. - gain is also tuned ex-

ternally in analog domain and the finite gain error in each stage

is corrected by a simple off-chip radix calibration in digital do-

main. It is instructive to note that the linear gain error correction

is enabled by the proposed - converter despite the use of a

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

3/11

OHet al.: A TIME-BASED PIPELINED ADC USING BOTH VOLTAGE AND TIME DOMAIN INFORMATION 963

Fig. 4. Proposed time-based pipelined ADC.

Fig. 5. Conventional - conversion employed in noise-shaped two-step integration quantizer in [12].

low gain nonlinear amplifier. For sub-TDCs time reference, a

voltage controlled delay line (VCDL) is employed.

The key features of the proposed ADC are as follows: First, a

high resolution and wide signal bandwidth can be attained with

the pipelined Nyquist ADC architecture. Second, a low gain

power-efficient and nonlinear amplifier can be used for linear

- conversion in thefirst stage based on the proposed -

conversion. Third, a simple charge pump based pipelined ar-

chitecture is employed for low power consumption. Finally, the

accuracy requirement of the backend pipelined TDC in time do-

main is significantly relaxed by the resolution of the first stagein voltage domain, where high accuracy is easier to achieve than

a conventional TDC only architecture in time domain. As a re-

sult, this architecture takes advantage of the unique benefits of

utilizing both the voltage and the time domains, by processing

MSBs in voltage domain and LSBs in time domain with this

proposed architecture.

B. - Conversion

To process the signal in time domain, the initial input to the

first stage of the ADC in voltage should be converted to a time-

domain signal. An example of a conventional - conversion

employed in a two-step quantizer is shown in Fig. 5 [12]. Since

the transferred residue charge on the feedback capacitor

is used for measuring the discharging time, the accuracy of

this charge transfer affects this - conversion process (charge

transfer is based on the amplifier characteristic). The residue

output in voltage domain after the amplification phase is given

by the following equation:

(2)

where is a nonlinear open loop dc gain of the ampli-

fier which is affected by the signal swing and is the feed-

back factor. Therefore, the time-domain output at zero-crossing

is given by (3):

(3)

As a result, any nonlinear error from the amplifier directly af-

fects the time-domain output in this - conversion. Therefore,

a high gain and linear amplifier is required and output swing is

limited in this case.

Fig. 6 shows the proposed - conversion, which allevi-

ates the stringent amplifier requirements on gain, output swing,

and linearity. In the proposed solution, which operates in three

phases, the charge stored in both sampling and feedback ca-

pacitors is discharged together. Because there is no charge loss

on both capacitors and discharged together to measure the time

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

4/11

964 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 49, NO. 4, APRIL 2014

Fig. 6. Proposed - conversion which operates in three phases.

for zero-crossing, the time-domain output at zero-crossing is al-

ways linear regardless of the amplifier non-idealities, as long as

the current source meets linearity requirement [13]. The residue

output after the amplification phase in this case is derived in the

following equation:

(4)

As reflected in (4), the residue output in voltage domain is still

affected by the amplifier characteristics. However, the time-do-

main output at zero-crossing in the discharging phase is inde-

pendent of the amplifier characteristics as shown in (5):

(5)

As a result, the output is linear regardless of the amplifi

ercharacteristics in the proposed - conversion. An intuitive

way to understand (5) is to realize that the zero-crossing detec-

tion by the comparator is always detected at the same voltage

(for the differential zero). There is no signal dependent ampli-

fier error in the time-domain output at the zero-crossing detec-

tion. Therefore, a low gain nonlinear amplifier can be used in

the proposed - conversion. The bandwidth of the amplifier

affects the time delay during the discharging phase, which is

largely signal independent in a relatively high bandwidth am-

plifier. Despite being a three phase operation, the time required

for the voltage domain residue amplification can be minimized.

The amplification phase does not require a fully settled residue

output in voltage domain. Fig. 7 shows the linearity simulation

of the proposed - conversion which compares the linearity

Fig. 7. Linearity simulation of the proposed - conversion using a residue

amplifier with 24 dB open loop dc gain (time domain output is converted to

voltage domain signal with an ideal time-to-voltage converter for measuringthe spectrum using FFT simulation).

of the residue output in voltage domain and time domain. In

this transistor level simulation with a 1.2 signal at 1.2-V

supply, a single stage common source amplifier, which has an

open loop dc gain of 24 dB, is used. As shown in Fig. 7, the

time-domain output after the discharging phase shows a supe-

rior linearity compared to the voltage output of the amplifier

after amplification (prior to discharging) with a simple nonlinear

amplifier with minimal gain.

This simple method for a - conversion provides signifi-

cant advantages as follows. First, the output swing of the am-

plifier (input swing of comparator) can be maximized, which

makes it easy to design the zero-crossing comparator for low

power. This provides scalability of design and portability in

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

5/11

OHet al.: A TIME-BASED PIPELINED ADC USING BOTH VOLTAGE AND TIME DOMAIN INFORMATION 965

Fig. 8. Examples for time reference generation.

the recent CMOS processes with low supply voltage. Second,a simple (small area and low power) amplifier with very low

gain could be employed for - conversion. Even though the

amplifier sees a reduced feedback factor in this case and less

time for settling because of three-phase operation (needs more

bandwidth), it benefits from a significant net improvement from

being able to use much simpler amplifier architecture. Thanks to

the proposed - conversion, the most power hungry block of

the residue amplifier in the first pipeline stage can be designed

without the conventional stringent requirements such as gain,

linearity, and power. This results in a scalable, low voltage, low

power ADC architecture amenable towards deep sub-micron

process.

C. Hybrid Time Domain Stage

Even though the pipelined TDC example based on the time-

domain pipeline stage in the previous section is a suitable candi-

date forlow power consumption, it also hasseveral error sources

such as the nonlinearity of the current source, the noise of the

comparator, and the jitter of the time reference. In particular,

jitter of the time reference will be the limiting factor for a given

process, speed, resolution and power of the pipelined TDC. The

linearity of the DAC pulse in the time-domain quantization is

also critical in achieving high accuracy, similar to DAC linearityin a conventional pipelined ADC.

Fig. 8 shows two possible methods to generate the time ref-

erence. Either a high frequency clock from an oscillator or a

delay line from DLL is typically employed as a time reference.

However both methods require high accuracy, which adds to

complexity. In general, the high frequency clock suffers from

the jitter and can consume a large amount of power. In order to

achieve -bit SNR, the required jitter tolerance in the time ref-

erence is less than 1 of the -bit TDC resolution, which is

not easy to achieve in high resolution cases with fine time refer-

ence [14]. Also DLL has a limited linearity due to its delay cell

mismatch [15]. Even though the jitter induced error or nonlin-

earity from the time reference can be calibrated, it requires com-

plex calibration algorithm and extra power consumption [16].

Fig. 9. Proposed hybrid time-domain stage.

Fig. 10. Basic operation of the proposed hybrid time-domain stage.

To solve the problem efficiently, a hybrid time-domain quan-tization stage is proposed as shown in Fig. 9. The proposed hy-

brid stage employs a capacitor DAC for charge subtraction in-

stead of using a time-domain DAC pulse. The linearity of DAC

in this architecture only depends on capacitor matching, which

is not difficult to achieve. Time-domain error sources such as

jitter or delay cell mismatch now only affect the linearity of

sub-TDC and it is relaxed with the given redundancy between

stages. With a conventional error correction scheme which usu-

ally is employed to correct comparator error in a pipelined ADC,

the time reference error up to can be corrected by

the 1 bit redundancy between the pipeline stages [17]. Fig. 10

illustrates the operation of the proposed stage. Initially, all ca-pacitors are reset to the positive reference. In charging phase,

capacitors are charged by a fixed current (4I) based on the time

input. At the same time, sub-TDC quantizes the time input and

generates a corresponding thermometer code for the DAC op-

eration, sequentially. In next phase, the stored charge on the ca-

pacitors (which represents the residue) is discharged by a dif-

ferent current ratio (I) for residue amplification. After the zero-

crossing, the amplified time residue output is passed on to the

next pipelined stage.

The comparison of two different time amplification methods

is shown in Fig. 11. In case of the amplification using a dual

slope (charging and discharging), the linearity of the current

source is limited (or signal swing is reduced) and the residue

gain is not well defined due to the different type of current

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

6/11

966 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 49, NO. 4, APRIL 2014

Fig. 11. Comparison of two different implementations of the time amplifica-tion: dual slope (charging and discharging) vs. single slope (two charging).

sources (PMOS and NMOS type) for the amplification. How-

ever in a single slope case (using two charging slopes) similar

to [8], the same type of current source is used for amplification.

As a result, the residue gain only depends on the matching of the

same type of current sources which is well defined with careful

layout. In this case, the linearity of the current source can be

maximized with a proper control of the output common mode.

Although twice the capacitors are required in the single slope

case, it provides many advantages in real implementation which

uses a low supply voltage. In case of the amplification using a

dual slope, it is difficult to get a required signal swing with high

linearity, which results in an increased capacitance for the sameSNR with a smaller signal swing. Therefore, the amplification

method using the single slope is employed in this work.

IV. CIRCUIT IMPLEMENTATION

A. Multiplying Digital-to-Analog Converter (MDAC)

Fig. 12 shows the first stage MDAC in the proposed ADC.

The proposed MDAC is similar to the conventional MDAC ex-

cept the additional blocks employed for discharging and -

conversion. It consists of capacitors and switches for sampling

and DAC operation, a residue amplifi

er, a discharging currentsource, and a zero-crossing comparator. In this implementation,

the number of sampling capacitors for DAC operation is re-

duced by half, based on the merged capacitor switching tech-

nique (8 capacitors for 4 bit operation) [18]. Note that there is

an additional path providing a fixed offset up to half of MDAC

output swing, which guarantees that the MDAC output is always

larger than zero for the uni-directional discharging, similar to

the MDAC in the two-step quantizer in [12].

Thanks to the proposed - conversion scheme a simple

switched amplifier which has only 24 dB dc gain is employed

as shown in Fig. 13. The proposed amplifier only operates in

amplifying/discharging phase based on switched operation for

low power consumption. Also, it drives only a small load capac-

itance (zero-crossing comparator) in the proposed architecture.

Fig. 12. Multiplying digital-to-analog converter (MDAC) incorporating the

proposed - conversion (drawn as single-ended for simplicity).

Fig. 13. Switched residue amplifier with a dc gain of 24 dB in MDAC.

Fig. 14. Implementation of the time-domain pipeline stage (TSTG).

Because the first stage residue amplifier is the most power con-

suming block in conventional pipelined architecture, this simple

amplifier structure incorporating small load capacitance reduces

ADC power consumption significantly.The power consumption

of the amplifier is further reduced by turning it off asynchro-

nously after zero-crossing.

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

7/11

OHet al.: A TIME-BASED PIPELINED ADC USING BOTH VOLTAGE AND TIME DOMAIN INFORMATION 967

Fig. 15. Switched charge pump (drawn PMOS current sources only for simplicity).

Fig. 16. Switched zero-crossing comparator.

B. Time Domain Pipeline Stage (TSTG)

Fig. 14 shows the implemented hybrid time-domain stage,

which adopts a pseudo differential configuration for better

supply noise immunity. It consists of capacitors and switches

for charging and DAC operation, current sources for two

charging slopes, sub-TDC with 2.5 bits, and a zero-crossing

comparator. Note that the comparator with four inputs is em-

ployed for a pseudo differential operation. The common mode

levels of current sources and comparator input are controlled

separately using the coupling capacitor, , to maximize thelinearity of current source. Therefore, the current variation

of the current source, due to the switching operation of the

capacitor DAC during the first charging phase with , is

minimized in this implementation. Because the parasitic ca-

pacitances on the output node of the current source and on the

input node of comparator are signal dependent, the linearity of

the proposed stage is mainly limited by these parasitic capaci-

tances. Although the linearity can be improved by using a larger

charging capacitance over the parasitic capacitance, it would

consume more power. Therefore, it would be quite difficult to

attain a very high accuracy if we were to incorporate only such

TDC stages. In the proposed ADC architecture, the accuracy

requirement of this TDC stage is relaxed by the resolution of

the first stage processed in voltage domain.

C. Switched Charge Pump

The detailed schematic of the charge pump in TSTG is illus-

trated in Fig. 15. The time residue gain is simply defined by the

device ratio of two PMOS transistors as current sources. In the

proposed charge pump, the dedicated reset phase, and ,

allows the current source to be settled to the bias point from

the turned-off condition before the actual charging. The current

source is switched-off completely after the charging to reduce

power consumption. Therefore, only the charge during the two

charging phases is used for the operation, without any static

charge in the charge pump. The power consumption is reducedfurther by switching off asynchronously after zero-crossing.

D. Switched Zero-Crossing Comparator

Fig. 16 shows the proposed zero-crossing comparator em-

ployed in TSTG. Similar to the charge pump, the comparator

is completely turned off asynchronously after the zero-crossing

detection to minimize power consumption. In the proposed

time-domain pipeline stage, the linearity is limited by the signal

dependant parasitic capacitance on the comparator input node.

During the first charging phase, the comparator is turned-off

because the comparator is not used for comparison. However,

any voltage change on the floating node from the turned-off

transistor causes the parasitic capacitance to change, which

results in a nonlinear error during the charging operation. This

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

8/11

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

9/11

OHet al.: A TIME-BASED PIPELINED ADC USING BOTH VOLTAGE AND TIME DOMAIN INFORMATION 969

Fig. 19. Residue plot of TSTG (a) with comparator delay and (b) with delay

correction by injecting time offset in time reference.

B. Delay From Zero-Crossing Comparator

The dynamic range of the proposed time-domain stage is

mainly limited by the delay from zero-crossing comparator.Fig. 19(a) shows the residue plot of TSTG with a 2.5 bit

resolution (6 time comparators). With a conventional error

correction scheme based on 1 bit redundancy, the decision

error up to from the sub-TDC can be corrected

in the proposed architecture. The error correction range is

in ideal case. However, the error correction range

is reduced due to the delay from the zero-crossing comparator

(in red curve). If this delay is larger than , the residue

output will saturate the following pipeline stage, which could

be problematic in the proposed architecture. Only the delay

from the comparator is considered here for simplification,

which is the largest contributor in the proposed architecture.

Therefore the delay should be minimized compared to the time

reference or should be properly corrected (to maximize error

correction range). Fig. 19(b) compares two residue plots with

and without a delay correction, which compensate the delay

from the zero-crossing comparator. With the delay correction,

the delay can be corrected by subtracting the same amount of

delay from the time reference as a time offset (in blue curve).

By shifting the decision point of the sub-TDC, the time residue

output can be located in the nominal range, which allows the

same error correction range as the ideal case. As a result, the

entire error correction range (up to ) is used for

the error correction of the sub-TDC. In this implementation,

another adjustable delay cell is added to the time reference (in

Fig. 20. Chip photo of the prototype ADC in 0.13 m CMOS process

( mm m by 460 m).

Fig. 21. Measured DNL and INL.

VCDL) for this purpose. This time offset is adjusted externally

by monitoring the digital output code from the sub-TDC.

VI. MEASUREMENT RESULTS

The prototype ADC was implemented in a 0.13 m CMOS

process. Fig. 20 shows the chip photograph of the fabricated

prototype [11]. The active area is 0.5 mm (1095 m by

460 m). Fig. 21 shows the measured DNL and INL. In this

measurement, 11 bit MSBs are used for DNL and INL calcu-

lation. In this prototype, an adjustable delay cell is employed

in the time reference, which corrects each comparator delay

globally. However due to the limited delay correction range andmatching accuracy of the blocks in actual implementation, this

global delay correction does not completely correct the delay

in the LSB stage (TSTG3). This results in input saturation of

the next stage (TSTG4). Due to this saturation, the prototype

ADC still has a few missing codes even at 12 bit resolution.

Therefore, DNL and INL of the prototype ADC are measured

at 11 bit resolution, while the entire 14 bit output is used for

SNDR and SFDR measurements. The measured DNL and

INL at 11 bit accuracy are and ,

respectively. Fig. 22 shows the measured output spectrum at

70 MS/s sampling rate and 1 MHz input frequency. The mea-

sured SNDR and SFDR are 69.3 dB and 80.6 dB, respectively,

while consuming 6.38 mW under 1.3-V supply. Due to the

proposed - conversion in the first stage of the pipelined

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

10/11

970 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 49, NO. 4, APRIL 2014

Fig. 22. Measured output spectrum ( , downsampled by afactor of 4).

Fig. 23. Measured SNDR vs. input frequency.

Fig. 24. Dynamic range of the proposed ADC.

ADC, the input range is maximized up to near rail-to-rail of

2.4 for the maximum SNR performance while achieving

high linearity of more than 80 dB SFDR at the same time.

The measured SNDR and SFDR with 20 MHz input frequency

are 65.2 dB and 75.9 dB, respectively. The measured SNDR

versus different input frequencies is shown in Fig. 23. The

measured dynamic range with 1 MHz input signal is shown

in Fig. 24, which is 72.6 dB with a of the full scale

input. The calculated best FOM with a 1 MHz input frequency

Fig. 25. Power breakdown of the prototype ADC.

TABLE IPERFORMANCE COMPARISON.

TABLE IIPERFORMANCE SUMMARY OF THE PROTOTYPE ADC.

is 38.2 fJ/conversion-step. Table I compares the recently pub-lished state of the art Nyquist ADC with maximum SNDR

above 65 dB, sampling rate above 50 MHz, and Walden FOM

below 100 fJ/C-S [20][24]. As shown in Table I, the proposed

ADC shows a competitive FOM among the recently published

ADCs with similar specifications. The FOM of the proposed

ADC can be improved further with a more advanced CMOS

process. Fig. 25 shows the power breakdown and Table II

summarizes the measured performance of the prototype ADC,

respectively.

VII. CONCLUSION

A pipelined ADC incorporating a time-based pipeline archi-

tecture is presented in this paper. The proposed ADC uses both

-

8/9/2019 A Time-Based Pipelined ADC Using Both Voltage and Time Domain Information

11/11

OHet al.: A TIME-BASED PIPELINED ADC USING BOTH VOLTAGE AND TIME DOMAIN INFORMATION 971

time domain and voltage domain information in analog-to-dig-

ital conversion. By using the pipelined TDC as a backend stage

of the ADC, as well as a pipeline stage in voltage domain as

the first stage, the proposed architecture achieves power effi-

ciency and the linearity. The proposed ADC is amenable to

process scaling and uses a scaling-friendly amplifier with min-

imum dc gain and maximum signal swing (in the first stage

MDAC for - conversion). The power efficiency and lin-

earity of the ADC are further improved by the proposed hybrid

time-domain pipeline stage which uses a simple charge pump

and capacitor DAC for the time residue generation.

ACKNOWLEDGMENT

The authors would like to thank Texas Instruments for the

chip fabrication.

REFERENCES

[1] C. P. Hurrell, C. Lyden, D. Laing, D. Hummerston, and M. Vickery,

An 18 b 12.5 MS/s ADC with 93 dB SNR, IEEE J. Solid-State Cir-

cuits, vol. 45, no. 12, pp. 26472654, Dec. 2010.[2] S. Naraghi, M. Courcy, and M. P. Flynn, A 9-bit 14 and 0.06

mm pulse position modulation ADC in 90 nm digital CMOS,IEEE

J. So lid-State Circuits, vol. 45, no. 9, pp. 18701880, Sep. 2010.

[3] C. S. Taillefer and G. W. Roberts, Delta-Sigma A/D conversion via

time-mode signal processing,IEEE Trans. Circuits Syst. I, vol. 56, no.

9, pp. 19081920, Sep. 2009.

[4] M. Z. Straayer and M. H. Perrott, A 12-bit 10 MHz bandwidth, con-

tinuous-time ADC with a 5-Bit, 950-MS/s VCO-based quantizer,

IEEE J. Solid -State C ircuits, vol. 43, no. 4, pp. 805814, Apr. 2008.

[5] A. M. Abaset al., Time difference amplifier,Electron. Lett., vol. 38,

no. 23, pp. 14371438, Nov. 2002.

[6] M. Lee and A. A. Abidi, A 9 b 1.25 ps resolution coarse-fine time-to-

digital converter in 90 nm CMOS that amplifies a time residue,IEEE

J. S olid-State Circuits,vol. 43, no. 4, pp. 769777, Apr. 2008.

[7] Y. Seo, J. Kim, H. Park,and J. Sim, A 0.63 ps resolution,11 b pipeline

TDC in 0.13 m CMOS, in IEEE Symp. VLSI Circuits Dig. Tech.Papers, 2011, pp. 152153.

[8] H. Yang and R. Sarpeshkar, A time-based energy-efficient

analog-to-digital converter, IEEE J. Solid-State Circuits, vol.

40, no. 8, pp. 15901601, Aug. 2005.

[9] P. Chen, C.-C. Chen, and Y.-S. Shen, A low-cost low-power CMOS

time-to-digital converter based on pulse stretching,IEEE Trans. Nucl.

Sci., vol. 53, no. 4, pp. 22152220, Aug. 2006.

[10] J. Shen and P. R. Kinget, Current-charge-pump residue amplification

for ultra-low-power pipelined ADCs,IEEE Trans. Circuits Syst. II,

vol. 58, no. 7, pp. 412416, Jul. 2011.

[11] T. Oh, H. Venkatram, and U. Moon, A 70 MS/s 69.3 dB SNDR 38.2

fJ/conversion-step time-based pipelined ADC, in IEEE Symp. VLSI

Circuits Dig. Tech. Papers, 2013, pp. C96C97.

[12] T. Oh, N. Maghari, and U. Moon, A second-order ADC using

noise-shaped two-step integrating quantizer, IEEE J. Solid-State Cir-

cuits, vol. 48, no. 6, pp. 14651474, Jun. 2013.

[13] G. Smarandoiuet al., An All-MOS analog-to-digital converter usinga constant slope approach,IEEE J. Solid-State Circuits, vol. SSC-11,

no. 3, pp. 408410, Jun. 1976.

[14] A. Hajimiri, S. Limotyrakis, and T. H. Lee, Jitter and phase noise

in ring oscillators, IEEE J. Solid-State Circuits, vol. 34, no. 6, pp.

790804, Jun. 1999.

[15] G. Li, Y. M. Tousi, A. Hassibi, and E. Afshari, Delay-line-based

analog-to-digital converters, IEEE Trans. Circuits Syst. II, vol. 56,

no. 6, pp. 464468,Jun. 2009.

[16] T. Oh, H. Venkatram, J. Guerber, and U. Moon, Correlated jitter sam-

pling for jitter cancellation in pipelined TDC, inIEEE Int. Symp. Cir-

cuits Syst., 2012, pp. 810813.

[17] S. H. Lewis, H. S. Fetterman, G. F. Gross Jr., R. Ramachandran, and T.

R. Viswanathan, A 10-b 20-Msample/s analog-to-digital converter,

IEEE J. Solid- State C ircuits, vol. 27, no. 3, pp. 351358, Mar. 1992.

[18] S. Yoo, T. Oh, J. Moon, S. Lee, and U. Moon, A 2.5 V 10 b 120

MSample/s CMOS pipelined ADC with high SFDR, in Proc. IEEECustom Integrated Circuits Conf., 2002, pp. 441444.

[19] D. Chang, J. Li, and U. Moon, Radix-based digital calibration tech-nique for multi-stage recycling pipelined ADC, IEEE Trans. Circuits

Syst. I, vol. 51, no. 11, pp. 21332140, Nov. 2004.[20] T. Morieet al., A 71 dB-SNDR 50 MS/s 4.2 mW CMOS SAR ADC

by SNR enhancement tech niques utilizing noise, in IEEE ISSCC Dig.

Tech. Papers, 2013, pp. 272273.[21] R. Kapusta, J. Shen, S. Decker, H. Li, and E. Ibaragi, A 14 b 80 MS/s

SAR ADC with 73.6 dB SNDR in 65 nm CMOS, inIEEE ISSCC Dig.Tech. Papers, 2013, pp. 472473.

[22] N. Dolev, M. Kramer, and B. Murmann, A 12-bit, 200-MS/s,11.5-mW pipeline ADC using a pulsed bucked brigade front-end, in

IEEE Sym p. VLSI Circuits Dig. Tech. Papers, 2013, pp. C98C99.

[23] J. Chu, L.Brooks,andH.-S. Lee,A zero-crossing based12 b 100MS/spipelined ADC with decision boundary gap estimatio n calibration , in

IEEE Sym p. VLSI Circuits Dig. Tech. P apers, 2010, pp. 237238.[24] C. C. Lee and M. P. Flynn, A 12 b 50 MS/s 3.5 mW SAR assisted

2-stage pipeline ADC, in IEEE Symp. VLSI Circuits Dig. Tech. Pa-pers, 2010, pp. 239240.

Taehwan Oh (S09M14) received the B.S. and

M.S. degrees in electronic engineering from SogangUniversity, Seoul, Korea, in 2000 and 2002, respec-

tively, and the Ph.D. degree in electrical engineering

and computer science from Oregon State University,Corvallis, OR, USA, in 2013.

He is currently an analog design engineer atTektronix, Inc., Beaverton, OR, USA. From 2002

to 2009, he was with Samsung Electronics, Yongin,Korea, where he was working on analog-to-digital

converters and analog front-end for various ap-

plications. His research interests include high performance analog-to-digital

converters and analog front-end for signal interface in many applications.

Hariprasath Venkatram (S08M14) received the

B.Tech. and M.Tech. dual degrees in electrical engi-

neering from Indian Institute of Technology, Madras,

India, in 2008, and the Ph.D. degree in electrical en-

gineering and computer science from Oregon State

University, Corvallis, OR, USA, in 2013.

He is currently a research scientist at Intel Cor-

poration, Hillsboro, OR, USA. He has received theProfessor Achim Bopp Award from IIT-Madras and

a finalist in the Broadcom Foundation University

Research competition. His research interests include

data converters, timing circuits, amplifiers, fi lters and mixed signal design. He

is a member of Solid-State Circuits and Circuits and Systems Society.

Un-Ku Moon (S92M94SM99F09) received

the B.S. degree from the University of Washington,

Seattle, WA, USA, in 1987, the M.Eng. degree from

Cornell University, Ithaca, NY, USA, in 1989, and

the Ph.D. degree from the University of Illinois,

Urbana-Champaign, IL, USA, in 1994.

He has been with the School of Electrical Engi-

neeringand Computer Science, Oregon State Univer-

sity, Corvallis, OR, USA, since 1998. Before joining

Oregon State University, he was with Bell Laborato-ries from 1988 to 1989, andfrom 1994 to 1998. His

technical contributions have been in the area of analog and mixed-signal cir-

cuits including high linearity filters, timing recovery, PLLs, data converters, and

low-voltage circuits for CMOS.

Dr. Moon served as the Editor-in-Chief of the IEEE JOURNAL OF SOLID-

STATE CIRCUITS and the IEEE TRANSACTIONS ONCIRCUITS ANDSYSTEMS II,

as a Distinguished Lecturer of the IEEE Solid-State Circuits Society, as an As-

sociate Editor of the IEEE JOURNAL OF SOLID-STATE CIRCUITSand the IEEE

TRANSACTIONS ON CIRCUITS AND SYSTEMS II, and as the Deputy Editor-in-

Chief of the IEEE TRANSACTIONS ONCIRCUITS ANDSYSTEMS II. He served on

governing boards ofboth the IEEE Solid-State Circuits Society (SSCS AdCom)

and the IEEE Circuits and Systems Society (CASS BoG) as the SSCS represen-

tative to CASS. He also served as a Technical Program Committee member of

the IEEE International Solid-State Circuits Conference, the IEEE VLSI Circuits

Symposium, and the IEEECustom Integrated Circuits Conference. He currently

serves on the Executive Committee of the IEEE Symposia on VLSI Technologyand Circuits.