2. FET Biasing(1)

-

Upload

akmtouhidur-rahman -

Category

Documents

-

view

3.842 -

download

26

Transcript of 2. FET Biasing(1)

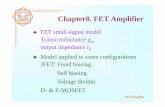

Week 7 Chapter 3FET Small Signal Analysis

√Able to discuss and analyze the ac analysis for various MOSFET configuration using the FET ac

equivalent circuit

√Able to relate the dc analysis and ac analysis for FET and MOSFET configuration or

network system

Objective

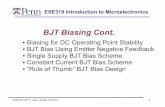

FETs provide

• excellent voltage gain

• high input impedance

• low-power consumption

• good frequency range

• small in size and weight

Introduction

Transconductance

The relationship of VGS (input) to ID (output) is called transconductance.

The transconductance is denoted gm. Unit is siemens (S)

GS

Dm

V

Ig

Introduction

Graphical determination of gm

Introduction

GS

Dm

VΔ

Ig

P

GS

P

DSSm

V

V1

V

2Ig

P

DSSm0

V

2Ig

P

GSm0m

V

V1gg

DSS

D

P

GS

I

I

V

V1

DSS

Dm0

P

GSm0m

I

Ig)

V

V(1gg

Using differential calculus

Maximum gm at VGS =0V:

Effect of ID on gm for

Mathematical Definition of gm

Introduction

Zi

osd

Y

1rZo

constantVI

Vr

GSD

DSd

FET Impedance

Input Impedance Zi:

Output Impedance Zo:

Yos: admittance equivalent circuit parameter listed on FET specification sheets.

Introduction

Yos: admittance equivalent circuit parameter listed on FET specification sheet.

FET AC Equivalent Circuit

Introduction

Introduction

To do the AC analysis, remember these 4 STEPs:

1) Set all the DC sources to zero and replace them by a short circuit equivalent.2) Replace all capacitors by a short circuit equivalent3) Remove all elements bypassed by the short circuit equivalents as introduced by Step 1 and Step 24) Redraw the network in a more convenient and logical form.

JFET Common-Source (CS) Fixed-Bias

The input is on the gate and the output is on the drain.

JFET CS Fixed-Bias

JFET Common-Source (CS) Fixed-Bias

JFET CS Fixed-Bias

AC Equivalent Circuit

JFET CS Fixed-Bias

Impedances

GRZi dD r||RZoDd

D 10RrRZo

JFET CS Fixed-Bias

)R||(rgVi

VoAv Ddm

Dd Dm 10RrRg

Vi

VoAv

Voltage Gain

JFET CS Fixed-Bias

A CS amplifier configuration has a 180-degree phase shift between input and output.

Phase Relationship

JFET CS Fixed-Bias

Fixed-bias configuration has an operating point defined by VGSQ = -2V and IDQ = 5.625 mA, with IDSS = 10mA and VP = -8V. The value of yos is provided as 40 µS. Determine:

a) gm

b) Zi

c) Zo

d) AV

e) AV ignoring the effects of rd

JFET Fixed-Bias

Example:

JFET Fixed-Bias

Solution:

JFET CS Self-Bias

Bypass capacitor

JFET CS Self-Bias

JFET CS Self-Bias

JFET CS Self-Bias

Input Impedance:

Output Impedance:

GRZi

Dd R||rZo DdD 10RrRZo

JFET CS Self-Bias

)R||(rgAv Ddm

Dd Dm 10RrRgAv

Voltage Gain

A CS amplifier configuration has a 180-degree phase shift between input and output.

If Cs is removed, it affects the gain of the circuit.

JFET CS Self-Bias Unbypassed C

AC Equivalent Circuit

JFET CS Self-Bias Unbypassed C

Input Impedance:

Output Impedance:

JFET CS Self-Bias Unbypassed C

JFET CS Self-Bias Unbypassed C

JFET CS Self-Bias Unbypassed C

JFET CS Self-Bias Unbypassed C

Voltage Gain

Example

Solution

Solution

JFET CS Voltage Divider

JFET CS Voltage Divider

AC Equivalent Circuit

Input Impedance: 21 R||RZi

Dd R||rZo

DdD 10RrRZo

Output Impedance:

JFET CS Voltage Divider

Impedance

)R||(rgAv Ddm

Dd Dm 10RrRgAv

JFET CS Voltage Divider

Voltage Gain

JFET CS Voltage Divider

EXAMPLE:

If Vi =20mV,determine:

(i) Zi

(ii)Zo

(iii)Vo

with CS and without CS.

1. D-MOSFETs have similar AC equivalent models.

2. D-MOSFETs has the same equation for gm as like JFET.

3. The only difference is that VGS can be positive for n-channel devices and negative for p-channel devices.

4. This means that gm can be greater than gm0.

Depletion-Type MOSFETs

Depletion-type MOSFET in Depletion Mode

Depletion mode The characteristics are similar to the JFET.When VGS = 0V, ID = IDSS

When VGS < 0V, ID < IDSS

The formula used to plot the Transfer Curve still applies:

Depletion mode The characteristics are similar to the JFET.When VGS = 0V, ID = IDSS

When VGS < 0V, ID < IDSS

The formula used to plot the Transfer Curve still applies:

2

P

GSDSSD )

V

V(1II

D-MOSFET AC Equivalent Model

D-MOSFET AC Equivalent Model

Example: Given VGSQ =0.35V and IDQ = 7.6mA, analyze the network given and calculate:

a. gm

b. rd

c. Zi

d. Zo

e. Av

D-MOSFET AC Equivalent Model

mS43

2(6m)

V

2Ig

P

DSSm0

Solution:

mS47.43-

35.01mS4

V

V1gg

P

GSm0m

kohm10010uS

1

Y

1r

osd

Mohm17.9M110//M10R//RZ 21i

kohm77.1k8.1//k100R//rZ Ddo

05.8RgA

thereforeR10r since

DmV

Dd

Enhancement-Type MOSFETs

There are two types of E-MOSFETs:

nMOS or n-channel MOSFETspMOS or p-channel MOSFETs

E-MOSFET AC Equivalent Model

gm and rd can be found in the specification sheet for the FET.

Forward transfer admittance

E-MOSFET CS Drain-Feedback Configuration

AC Equivalent Circuit

Impedances

Input Impedance:

)R||(rg1

R||rRZi

Ddm

DdF

DdDdFDm

F

10Rr,R||rR Rg1

RZi

DdF R||r||RZo

DdDdF D 10Rr,R||rRRZo

Output Impedance:

Voltage Gain

)R||r||(RgAv DdFm

DdDdF Dm 10Rr,R||rRRgAv

Phase Relationship

This is a CS amplifier configuration therefore it has 180-degree phase shift between input and output.

E-MOSFET CS Voltage-Divider Configuration

AC Equivalent Circuit

E-MOSFET CS Voltage-Divider Configuration

Impedances

Input Impedance:

Output Impedance:

21 R||RZi

Dd R||rZo

Dd D 10RrRZo

E-MOSFET CS Voltage-Divider Configuration

Voltage Gain

)R||(rgAv Ddm

Dd Dm 10RrRgAv

E-MOSFET CS Voltage-Divider Configuration

Summary Table

Summary Table

Example: Design the fixed bias network shown in the figure with AC gain equals to 10.

a. Determine value of RD

Design FET Amplifier Networks

mS54

2(10m)

V

2Ig

P

DSSm0

Solution:

mS53-

01mS5

V

V1gg

P

GSm0m

kohm5020uS

1

Y

1r

osd

kohm08.2Rtherefore

k2Rk50/)R(k50

k2Rr/Rr

kohm2R//r Z

D

DD

DdDd

Ddo

kohm2mS5/10)R//r(

10)R//r(gA

Dd

DdmV

Design FET Amplifier Networks

Effect of RL and Rsig

1. Effect of source resistance and load resistance on the AC gain

2. Analysis using AC model or two port equations.

3. The two-port equations for FET are exactly same as BJT because quantities of interest are at the input and output terminals (not the components).

4. The loaded gain is always less than the no-load gain.

5. AVNL > AV

Effect of RL and Rsig

TWO-PORT SYSTEM

VNLOL

LV A

R R

RA

AVNL is no load voltage gain

Effect of RL and Rsig

Rsig RL

)R//R//r(gV

VA LDdm

i

OV

Effect of RL and Rsig

Using two-port approach:

)R//R//r(g

)R//r(g)R//r( R

R

)R//r(gR R

RA

therefore

R//r Rbut

)R//r(gR R

RA

R R

RA

systemport -for twoagain Overall

LDdm

DdmDdL

L

DdmOL

LV

DdO

DdmOL

LVNL

OL

LV

Cascade Configuration

V2V1V AAA Voltage gain,

Cascade Configuration

D2o

g1i

RZ

RZ

Impedances

Practical Applications

• Three-Channel Audio Mixer

• Silent Switching

• Phase Shift Networks

• Motion Detection System