基本逻辑电路: 组合逻辑电路、 时序逻辑电路 一 组合逻辑电路设计 简单门电路、编码器、译码器、 加法器、多路选择器、三态门等。

第三章 组合逻辑电路

Click here to load reader

-

Upload

amena-villarreal -

Category

Documents

-

view

104 -

download

3

description

Transcript of 第三章 组合逻辑电路

第三章 组合逻辑电路 本章提要: 既介绍算术运算电路、信号变换电路、数字比较器等常用组合逻辑电路的工作原理和使用方法,又介绍 CMOS 、LSTTL 集成芯片在工程设计中的应用。通过本章的学习,应达到以下要求:1 、掌握半加器、全加器、常用算术 / 逻辑运算单元等运算电路集成芯片的工作原理和使用方法;2 、掌握典型的译码器、编码器、数据选择器、数据分配器等信号变换电路集成芯片的工作原理和使用方法;3 、了解数值比较器的工作原理和扩展方法;了解组合逻辑电路中的竞争与冒险现象。会进行基本组合逻辑电路的应用设计。

◆ 数字电路按逻辑功能和电路结构的不同特点来划分可分为两类:组合逻辑电路、时序逻辑电路。

在任何时刻,输出状态只决定于该时刻各输出状态的组合,而于电路以前的状态无关的逻辑电路称为组合逻辑电路。

第三章 组合逻辑电路

3.1 概 述

XX11

XXnn

XX22 YY22

YY11

YYnn

. . . . ... . .. . .

组合逻辑电路组合逻辑电路输入输入 输出输出

◆ 组合逻辑电路的特点是: (1) 输出与输入之间没有反馈延时通路 (2) 电路中没有记忆元件◆ 组合逻辑电路的表示方法除函数表达式外,还可以

由真值表、卡诺图、逻辑电路图来表达,实际上由一种表示方法可推出另一种表示方法。

第三章 组合逻辑电路

3.1 概 述

组合逻辑电路分析的主要任务是根据其逻辑电路图确定组合逻辑电路分析的主要任务是根据其逻辑电路图确定逻辑功能。逻辑功能。

第三章 组合逻辑电路

3.1 概 述组合逻辑电路的分析组合逻辑电路的分析

分析步骤:分析步骤: ① ① 写出逻辑图输出端的逻辑表达式写出逻辑图输出端的逻辑表达式 ② ② 化简和变换逻辑表达式化简和变换逻辑表达式 ③ ③ 列出真值表列出真值表 ④ ④ 根据真值表和逻辑表达式对逻辑电路进行分析,最根据真值表和逻辑表达式对逻辑电路进行分析,最后确定电路的逻辑功能,并可附加简单说明。后确定电路的逻辑功能,并可附加简单说明。

已知逻辑电路已知逻辑电路确定

逻辑功能逻辑功能

第三章 组合逻辑电路

3.1 概 述组合逻辑电路的分析组合逻辑电路的分析

例

Y1 .A

B&

&

&

&

Y

Y3

Y2

.

.BAY1

BAAY2

BABY3

Y = Y2

Y3

BABABABBAAYYY 32

进行逻辑变换和化简进行逻辑变换和化简 ::

第三章 组合逻辑电路

3.1 概 述组合逻辑电路的分析组合逻辑电路的分析

例

A B Y

001 1

0

01

110

01

真值表

BA

BABAY

=1=1

AABB

YY

逻辑符号逻辑符号

““ 异或”门异或”门

◆◆ 当用小规模集成电路设计组合逻辑电路时一般步骤如下:当用小规模集成电路设计组合逻辑电路时一般步骤如下: ① ① 分析设计任务,确定输入变量、输出变量,找到输出与输入之间的 分析设计任务,确定输入变量、输出变量,找到输出与输入之间的 因果关系,列出真值表。 因果关系,列出真值表。 ② ② 由真值表写出逻辑表达式。由真值表写出逻辑表达式。 ③ ③ 化简、变换逻辑表达式,并画出逻辑图。化简、变换逻辑表达式,并画出逻辑图。 这样逻辑电路原理设计的工作任务就完成了,实际设计工作还包括集这样逻辑电路原理设计的工作任务就完成了,实际设计工作还包括集成电路芯片的选择,电路板工艺设计,安装、调试等内容成电路芯片的选择,电路板工艺设计,安装、调试等内容

第三章 组合逻辑电路

3.1 概 述组合逻辑电路的设计组合逻辑电路的设计◆◆ 组合逻辑电路设计的任务是根据给定的逻辑问题(课题),设计出能组合逻辑电路设计的任务是根据给定的逻辑问题(课题),设计出能实现其逻辑功能的组合逻辑电路,最后画出实现逻辑功能的电路图,当实现其逻辑功能的组合逻辑电路,最后画出实现逻辑功能的电路图,当用逻辑门设计组合逻辑电路时,要求使用的芯片最少、连接线最少。实用逻辑门设计组合逻辑电路时,要求使用的芯片最少、连接线最少。实际上,组合逻辑电路的设计与分析过程是一个相反的工作际上,组合逻辑电路的设计与分析过程是一个相反的工作

第三章 组合逻辑电路

3.1 概 述组合逻辑电路的设计组合逻辑电路的设计◆◆ 设计步骤设计步骤

实际逻辑问题

真值表逻辑抽象

逻辑赋值

逻辑电路图最简式卡诺图化简 用 SSI 实现

逻辑电路图适当形式的函数式 用 MSI 实现函数变换

第三章 组合逻辑电路

3.1 概 述组合逻辑电路的设计组合逻辑电路的设计

用与非门设计一个举重裁判表决电路。设举重比赛有 3 个裁判,一个主裁判和两个副裁判。杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表成功的灯才亮

例

1 、设主裁判为变量 A,副裁判分别为 B和 C ;表示成功与否的灯为 Y ,根据逻辑要求列出真值表

A B C Y A B C Y

0 0 0

0 0 1

0 1 0

0 1 1

0

0

0

0

1 0 0

1 0 1

1 1 0

1 1 1

0

1

1

1

2 、逻辑表达式 :

ABCCABCBAmmmY 765

第三章 组合逻辑电路

3.1 概 述组合逻辑电路的设计组合逻辑电路的设计

用与非门设计一个举重裁判表决电路。设举重比赛有 3 个裁判,一个主裁判和两个副裁判。杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表成功的灯才亮

例

3 、化简 AB C 00 01 11 10

0 1

11 1

Y= AB +AC ACABY A

B

A

C

Y

&

&

&

4、逻辑电路图

在我们设计电路时,最终电路可能存在一个门电路的输出带的负载非常多,可能超过器件的带负载能力,由于负载一般为同系列的门电路,故这类问题通常叫扇出问题。解决这种问题通过可通过两种方法解决:一种是采用扇出系数大的门作为输出(选择器件手册中称为带缓冲的门),这种门的扇出可达 20个,是可以满足要求的。另一种方法是采用分组的方法增加驱动能力

第三章 组合逻辑电路

3.1 概 述组合逻辑电路设计中应注意的问题组合逻辑电路设计中应注意的问题

◆ 输入端的限制问题(扇入问题)◇多余输入端的处理◇电路提供的输入端少于实际需要的输入端

当集成电路的输入端少于实际电路需要的输入端数时,比输入有多余端的处理措施复杂得多,通常采用分组的方法进行解决

◆扇出问题

第三章 组合逻辑电路

3.2 算术运算电路半加器电路半加器电路半加器是只考虑两个加数本身相加,而不考虑来自低位进位的逻辑电路

设计一位二进制半加器,输入变量有两个,分别为加数 A 和被加数 B ;输出也有两个,分别为和数 S 和进位 C

例

半加器真值表

Ai Bi Si Ci

0 0

0 1

1 0

1 1

0 0

1 0

1 0

0 1

iii

iiiiiii

BAC

BABABAS

1 、真值表 2 、逻辑表达式 =1

&

Ai

BiSi

Ci

Ai

Bi

Si

Ci

∑CO

半加器符号

半加器电路图3 、逻辑电路

设计一个全加器,其中, Ai 和 Bi 分别是被加数和加数 , Ci-1 为相邻低位的进位, Si 为本位的和, Ci 为本位的进位

第三章 组合逻辑电路

3.2 算术运算电路全加器电路全加器电路全加器是完成两个二进制数 Ai 和 Bi及相邻低位的进位 Ci-1

相加的逻辑电路例

1 、真值表 Ai Bi Ci-1 Si Ci

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0

1 0

1 0

0 1

1 0

0 1

0 1

1 1

2 、逻辑表达式

1iii1iii1iii1iiii CBACBACBACBAS

1iii1iii1iii1iiii CBACBACBACBAC

1ii1iiii CACBBA

1iii CBA

第三章 组合逻辑电路

3.2 算术运算电路

3 、逻辑电路

设计一个全加器,其中, Ai 和 Bi 分别是被加数和加数 , Ci-1 为相邻低位的进位, Si 为本位的和, Ci 为本位的进位

全加器电路全加器电路例

&

≥1

AAii

Ci

Si

CCi-1i-1BBii

&

&

=1

Ai

BiCi-1

Si

Ci COCO

CICI

第三章 组合逻辑电路

3.3 信号变换电路编码器十进制码→ 8421BCD编码器在日常生活中 , 人们通常使用十进制数来进行处理计算 , 然而数字设备却用二进制数或代码进行判断处理。十进制码→ 8421BCD编码器的作用就是将人们习惯使用的十进制数变换成 8421BCD码的电路 (十进制数 X 与四位二进制数的关系是 ,对应权分别为 8421)

编码器

高高低低电电平平信信号号

二二进进制制代代码码

22nn 个个 nn位位

十进制码输入有 10 个数码 , 要求对应有 10 种输出状态 , 而 3位二进制代码只有 8 种状态 ,所以输出需用 4位 (取 n=4)二进制代码 . 设输入的 10 个数码分别用 I0 、 I1 、…、 I9 表示 ,输出的 8421BCD 码分别采用Y3 、 Y2 、 Y1 、 Y0 表示

第三章 组合逻辑电路

3.3 信号变换电路编码器十进制码→ 8421BCD编码器

真值表

由于 I0 、 I1 、…、 I9 是一组相互排斥的变量 , 故可由真值表直接写出输出函数的逻辑表达式:

97531

975310

7632

76321

7654

76542

98

983

IIIII

IIIIIY

IIII

IIIIY

IIII

IIIIY

II

IIY

第三章 组合逻辑电路

3.3 信号变换电路编码器十进制码→ 8421BCD编码器

第三章 组合逻辑电路

3.3 信号变换电路译码器译码是编码的反过程,它是将代码的组合译成一个特定的译码是编码的反过程,它是将代码的组合译成一个特定的输出信号输出信号

译码器译码器

二二进进制制代代码码

高高低低电电平平信信号号

(a)(a)引脚排列图 (引脚排列图 ( bb )逻辑功能)逻辑功能 CC74HC42CC74HC42 的输出为反变量的输出为反变量 ,, 即为低电平有效即为低电平有效 ,,并且采用完全译码的方案 并且采用完全译码的方案

第三章 组合逻辑电路

3.3 信号变换电路译码器

集成 4线 -10线译码器8421BCD 输入的集成 4 线 -10 线译码器 CC74HC42 的引脚排列图和逻辑功能示意图

第三章 组合逻辑电路

3.3 信号变换电路译码器8421BCD8421BCD码→七段码→七段 1010进制码显示的译码器进制码显示的译码器

半导体显示半导体显示 (LED)(LED)液晶显示液晶显示 (LCD)(LCD)

数字系统中,常需要将运算结果用人们习惯的十进制显示出数字系统中,常需要将运算结果用人们习惯的十进制显示出来,这就要用到来,这就要用到显示译码器显示译码器

主要用于显示数字和字线主要用于显示数字和字线

可以显示数字、字母、文字和图形等可以显示数字、字母、文字和图形等

BCD数码BCD数码

显示译码器显示译码器

数码显示器数码显示器

a

e

b

c

f g

d

每字段是一只每字段是一只发光二极管发光二极管

七段显示器七段显示器 ::用七个发光字用七个发光字段构成 段构成 0 0 9 9 十个数字十个数字

第三章 组合逻辑电路

3.3 信号变换电路译码器

8421BCD8421BCD 码→七段码→七段 1010 进制码显示的译码器进制码显示的译码器— — 高电平驱动高电平驱动◆◆共阴极共阴极 a b c d e f g

Ya

A3

A2

A1

A0

+VCC

显示译码器

共阴

Yb

Yc

Yd

Ye

Yf

Yg

0

0

0

0

1111110

0

0

0

1

0

0

1

0

0110000

1101101

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1111001

0110011

1011011

1011111

1110000

1111111

1111011

f

a

b

c

d

e

g

. h

CO

Md c . he

f CO

M

bag

第三章 组合逻辑电路

3.3 信号变换电路译码器

8421BCD8421BCD 码→七段码→七段 1010 进制码显示的译码器进制码显示的译码器— — 低电平驱动低电平驱动◆◆共阳极共阳极

a b c d e f g

UCC

Ya

A3

A2

A1

A0

+UCC +UCC

显示译码器

共阳

Yb

Yc

Yd

Ye

Yf

Yg

0

0

0

0

0000001

0

0

0

1

0

0

1

0

1001111

0010010

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0000110

1001100

0100100

0100000

0

1

1

1

0001111

1

0

0

0

0000000

1

0

0

1

0000100

0 0 0 1 0 1 1 0 0 0 0 0 0 1 0 1 1 0 1 1 0 1

0 0 0 0 1 1 1 1 1 1 0

A3A2A1A0 a b c d e f g 09

0 0 1 1 1 1 1 1 0 0 1 0 1 0 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1

1 0 0 0 1 1 1 1 1 1 1 1 0 0 1 1 1 1 0 0 1 1

0 1 1 1 1 1 1 0 0 0 0

a

e

b

c

f g

d

77 段显示译码器真值表段显示译码器真值表

第三章 组合逻辑电路

3.3 信号变换电路译码器

8421BCD8421BCD 码→七段码→七段 1010 进制码显示的译码器进制码显示的译码器

≥1≥1 1 ≥1 ≥1 ≥1 ≥1

≥1≥1≥1 ≥1 ≥1 ≥1≥1≥1 ≥1 ≥1≥1 ≥1 ≥1

1 1 1

a b c d e f g

A3A2A1A0

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的工作原理

A0 A1

I3

I2

I1

I0

Y

控制信号

输入信号

输出信

号

从一组数据中选择一路信号进行传输的电路

数据选择器类似多路开关。选择哪一路信号由相应的一组控制信号控制

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的工作原理

四选一

A1A0

E

D0D1D2D3

Y

& ≥1

111

A0A1

D1

D0

D2

D3

Y

E

逻辑图

符号图

CC4539

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的工作原理

四选一功能表四选一功能表

输入输入 输出输出 E AE A11 A A22 YY

1 × ×1 × × 0 0 0 0 0 0 0 0 10 0 1 0 1 0 0 1 0 0 1 10 1 1

00D0D0D1D1D2D2D3D3

E)ABDDBABDADBA(Y 3210

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器 CC74HC151CC74HC151 一种典型的集成一种典型的集成 88线-线- 11 线数据选择器线数据选择器

E

74HC151

A0A1

Y

Y

5

16

71110

74HC151D0

GND

D1

D2

W

9432115141312

A2D0D1D2D3D4D5D6D7

A0

A1

A2

D3

W

E

1 16

8 9

DD44

DD55

DD77

DD66

UUCCCC

符号图符号图 引脚图引脚图

使能端,低电平有效

地址信号输入端

8 路数据输入端

互补输出端

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器 CC74HC151CC74HC151

E AE A22 A A11 A A00

W WW W

1 × × ×1 × × × 0 0 0 00 0 0 0 0 0 0 10 0 0 1 0 0 1 00 0 1 0 0 0 1 10 0 1 1 0 1 0 00 1 0 0 0 1 0 10 1 0 1 0 1 1 00 1 1 0 0 1 1 10 1 1 1

0 10 1DD00 D D00

DD11 D D11

DD2 2 DD22

DD3 3 DD33

DD4 4 DD44

DD5 5 DD55

DD6 6 DD66

DD77 D D77

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的应用利用数据选择器,当使能端有效时,将地址输入、数据输入代替逻辑函数中的变量实现逻辑函数

用八选一数据选择器用八选一数据选择器 CC74HC151CC74HC151产生逻辑函数产生逻辑函数 ::例BABCACABY

BABCACABY CBACBABCACAB

6310 mmmm

11 、把逻辑函数变换成最小项表达示、把逻辑函数变换成最小项表达示 ::

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的应用的应用用八选一数据选择器用八选一数据选择器 CC74HC151CC74HC151产生逻辑函数产生逻辑函数 ::例 BABCACABY

22 、八选一数据选择器的输出逻辑函数表达式为、八选一数据选择器的输出逻辑函数表达式为

4012302201210120012 1 DAAADAAADAAADAAADAAAY

701260125012 DAAADAAADAAA

7766554433211100 DmDmDmDmDmDmDmDm

若将式中若将式中 A2A2 、、 A1A1 、、 A0A0用用 AA、、 BB 、、 CC 来代来代 ,D0=D1=,D0=D1=D3=D6=1, D2=D4=D5=D7=0D3=D6=1, D2=D4=D5=D7=0,画出该逻辑函数的逻辑,画出该逻辑函数的逻辑图图

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的应用的应用用八选一数据选择器用八选一数据选择器 CC74HC151CC74HC151产生逻辑函数产生逻辑函数 ::例 BABCACABY

33 、逻辑图为、逻辑图为

E

A0

A1

A2

D0 D1 D2 D3 D4 D5 D6 D7

Y

74HC151A

B

C

1

0

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的应用用数据选择器实现三变量多数表决器用数据选择器实现三变量多数表决器例

11 、选择数据选择器、选择数据选择器YY 为三变量函数 ,故选用 为三变量函数 ,故选用 8 8 选 选 1 1 数据选择器,现选用 数据选择器,现选用 74HC15174HC151

22 、写出逻辑函数的最小项表达式、写出逻辑函数的最小项表达式Y = AB + AC + BC = ABC + ABC + ABC + ABC

33 、写出数据选择器的输出表达式、写出数据选择器的输出表达式Y′= A2A1A0D0 + A2A1A0D1 + A2A1A0D2 + A2A1A0D3 + A2A1A0D4 + A2A1A0D5 + A2A1A0D6 + A2A1A0D7

44 、比较 、比较 Y Y 和 和 Y′Y′ 两式中最小项的对应关系两式中最小项的对应关系

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的应用用数据选择器实现三变量多数表决器用数据选择器实现三变量多数表决器例

令 A = A2 , B = A1 , C = A0则 Y′= ABCD0 + ABCD1 + ABCD2 + ABCD3 +

ABCD4 + ABCD5 + ABCD6 + ABCD7

为使 Y = Y′ ,应令 D0 = D1 = D2 = D4= 0D3 = D5 = D6 = D7 = 1

55 、画连线图、画连线图

第三章 组合逻辑电路

3.3 信号变换电路数据选择器

数据选择器的应用用数据选择器实现三变量多数表决器用数据选择器实现三变量多数表决器例

CT74LS151A2

A1

A0D0 D7D6D5D4D3D2D1

E

Y Y

Y′ABC

1

即可得输出函数

D0 D2D1 D4 D7D6D5D3

1

。 1 路对 8路数据分配器 CC4051 的示意图如图 3.23所示。 根据输出端的个数不同 ,数据分配器 (即 1 路对多路模拟开关 ) 可分为 1 对 4路模拟开关、 1 对 8路模拟开关等不同类型 .在图 3.25中 ,INH作为数据输入端 ,C 、 B、 A作为地址端 , 从Y0 ~ Y7 分别得到相应的输出。 1 路 8 路模拟开关 CC4051 的功能表如表 3.14所示。

第三章 组合逻辑电路

3.3 信号变换电路数据分配器数据分配器又称 1 路对多对模拟开关,是数据选择器的逆过程,即将一路输入变为多路输出的电路

图图 3.24 3.24 双双 11 对对 44路模拟开关路模拟开关 CC74HC4352CC74HC4352引脚图 引脚图 图图 3.25 13.25 1 对对 88模拟开关模拟开关 CC4051CC4051引脚图 引脚图

※※3.43.4数值比较器数值比较器3.4.1 13.4.1 1位数值比较器位数值比较器 在数字系统中,特别是计算机中的在数字系统中,特别是计算机中的 CPUCPU 具有多种运算功能,其中一种简单具有多种运算功能,其中一种简单的运算功能就是比较两个数的运算功能就是比较两个数 AA和和 BB的大小。数值比较就是对两数的大小。数值比较就是对两数 AA、、 BB进行进行比较,以判断其大小的逻辑电路。比较结果有比较,以判断其大小的逻辑电路。比较结果有 AA >> BB、、 AA << BB、、 A﹦BA﹦B三种三种情况。情况。 11位数值比较器是多位比较器的基础。两个位数值比较器是多位比较器的基础。两个 11位二进制数进行比较,输入信位二进制数进行比较,输入信号是两个要进行比较的号是两个要进行比较的 11位二进制数,先用位二进制数,先用 AA、、 BB表示;输出是比较结果,表示;输出是比较结果,有三种情况:有三种情况: AA >> BB、、 AA << BB、、 A﹦BA﹦B,现分别用,现分别用 LL11 、、 LL22 、、 LL33 表示。设表示。设 AA>> BB时时 LL11=1=1 ;; AA << BB时时 LL22=1=1 ;; A=BA=B时时 LL33=1=1 。由此可列出。由此可列出 11位数值比较器位数值比较器的真值表,如表的真值表,如表 3.153.15所示。根据此表可写出各输出的逻辑表达式:所示。根据此表可写出各输出的逻辑表达式:

由以上逻辑表达式可列出由以上逻辑表达式可列出 11 位数值比 位数值比较器的逻辑图,如图较器的逻辑图,如图 3.263.26所示。所示。

表表 3.15 13.15 1位数值比较器的真值表位数值比较器的真值表

3.4.2 3.4.2 集成数值比较器集成数值比较器1.1. 1 1 集成数值比较器集成数值比较器 CC74HC85CC74HC85的功能的功能 集成数值比较器集成数值比较器 CC74HC85CC74HC85是是 44 位数值比位数值比较器,其引脚图如图较器,其引脚图如图 3.273.27 所示,其功能如表所示,其功能如表3.163.16。从表。从表 3.163.16中可以看出,两个中可以看出,两个 44 位数位数 AA、、BB 比较,是先将比较,是先将 AA的最高位的最高位 AA33 和和 BB 的最的最高位BB33 进行比较,如果二者不相等就可以作为进行比较,如果二者不相等就可以作为 AA、、BB 的比较结果;如果二者相等,则再比较次高的比较结果;如果二者相等,则再比较次高位位 AA22 和和 BB22,, 依次类推。显然,如果依次类推。显然,如果 A=B,A=B, 则比则比较步骤必须进行到最低位上才能得到结果。较步骤必须进行到最低位上才能得到结果。 真值表中的输入变量包括真值表中的输入变量包括 AA33 与与 BB33 、、 AA22 与与BB22 、、 AA11 与与 BB11 、、 AA00 与与 BB00 输出变量为输出变量为 AA与与 BB的比较结果。其中低位片第的比较结果。其中低位片第 55,, 66,, 77 脚的输脚的输出信号出信号 FFAA >> BB 、、 FFAA << BB 、、 FFA=BA=B 是这两个低位数是这两个低位数字的比较结果。设置级联输入端第字的比较结果。设置级联输入端第 22 ,, 33 ,, 44脚是为了进行数值比较器的扩展,以便组成位脚是为了进行数值比较器的扩展,以便组成位数更多的数值比较器。数更多的数值比较器。

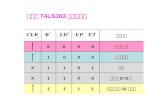

表 3.16 4位数值比较器 CC74HC85

由真值表可以看出,仅对由真值表可以看出,仅对 44 位数进行比较时,应对位数进行比较时,应对 IIAA>> BB 、、 IIAA << BB 、 、 IIA=BA=B 进行适当的处理,及进行适当的处理,及 IIAA >> BB=I=IAA << BB=0=0、、IIA=BA=B=1=1 。 。

22 、、数值比较器的扩展数值比较器的扩展 利用集成数值比较器的级联输入端,很容易构成更多位的数值比较器。数利用集成数值比较器的级联输入端,很容易构成更多位的数值比较器。数值比较器的扩展方式有串联和并联两种。采用串联方式扩展数值比较器时,随值比较器的扩展方式有串联和并联两种。采用串联方式扩展数值比较器时,随着位数的增加,从数据输入到稳定输出的延迟时间增加,当位数较多且要满足着位数的增加,从数据输入到稳定输出的延迟时间增加,当位数较多且要满足一定的速度要求时,可以采用并联方式。下面仅以串联方式为例说明数值比较一定的速度要求时,可以采用并联方式。下面仅以串联方式为例说明数值比较器的扩展方法。器的扩展方法。 如图如图 3.283.28 所示,两个所示,两个 44 位数值比较器位数值比较器 CC74HC85CC74HC85 串联而成为一个串联而成为一个 88 位数位数值比较器。由于两个值比较器。由于两个 88 位数,若高位数,若高 44 位相同,它们的大小则由低位相同,它们的大小则由低 44 位的比较结位的比较结果确定。因此,低果确定。因此,低 44 位的比较结果应作为高位的比较结果应作为高 44 位的条件,即低位的条件,即低 44 位比较器的输位比较器的输出端应分别与高出端应分别与高 44 位比较器的位比较器的 IIAA >> BB、、 IIAA << BB、、 IIA=BA=B的级联输入端连接。的级联输入端连接。

图图 3.28 3.28 数值比较器的数值比较器的位数扩展联接图 位数扩展联接图

对于对于 LSTTLLSTTL 集成数值比较器,最低集成数值比较器,最低 44 位的级联输入端位的级联输入端 IIAA >> BB 、、 IIAA << BB 、、 IIA=BA=B 必须预先预置为必须预先预置为 00、、 00、、 11 ,这样就能使两个多位数的各位都相同时,,这样就能使两个多位数的各位都相同时,比较器的比较器的 FFA=BA=B 输出端为输出端为 11 。。 应该注意的是,在应该注意的是,在 CMOSCMOS 集成数值比较器中,集成数值比较器中, IIAA >> BB 输入端应该接高输入端应该接高电平。这是因为在电平。这是因为在 CMOSCMOS 集成集成 44 位数值比较器中,为了使电路简化,首先位数值比较器中,为了使电路简化,首先实现实现 FFAA << BB 和和 FFA=BA=B ,再将两者进行或非运算而求得,再将两者进行或非运算而求得 FFAA >> BB ;而在;而在 LSTTL LSTTL 集成集成 44 位数值比较器中,是由各位数码的比较结果求得位数值比较器中,是由各位数码的比较结果求得 FFAA >> BB 、、 FFA=BA=B 和和 FFAA<< BB 的。的。

※ ※ 3.5 3.5 组合逻辑电路的竞争和冒险组合逻辑电路的竞争和冒险

3.5.1 3.5.1 组合逻辑电路中的竞争、冒险现象组合逻辑电路中的竞争、冒险现象例例 3.8 3.8 试分别画出图试分别画出图 3.293.29(( aa )、()、( bb )所示电路的输出)所示电路的输出波形。给定输入波形如图波形。给定输入波形如图 3.293.29(( cc )所示,设门的传输延迟)所示,设门的传输延迟时间为时间为 ttPDPD ,门,门 GG22 、、 GG33 的传输延时不予考虑。的传输延时不予考虑。

图图 3.29 3.29 例例 3.73.7电路及其波形电路及其波形

解:若不考虑门解:若不考虑门 GG11 的延迟时间,则图的延迟时间,则图 3.293.29(( aa )()( bb )所示的输出分别为:)所示的输出分别为: 若考虑门若考虑门 GG11 的传输延迟时间,则波形 反相以外还要延迟的传输延迟时间,则波形 反相以外还要延迟 ttPDPD ,从而在,从而在 tt11 ~~tt22 期间,波形 和期间,波形 和 AA同时为高电平,同时为高电平, Y1Y1 中出现了一个正向的窄脉冲。同理在中出现了一个正向的窄脉冲。同理在 tt33 ~~ tt44期间,期间, YY22 中出现了一个负向脉冲,如图中出现了一个负向脉冲,如图 3.293.29(( cc )所示,从图)所示,从图 3.293.29中中可以看出,同一个门的一组输入信号,由于经过不同长度导线或经过不同数目可以看出,同一个门的一组输入信号,由于经过不同长度导线或经过不同数目的“门”的传输,到达门输入端的时间有先有后,这种现象称为“竞争”。的“门”的传输,到达门输入端的时间有先有后,这种现象称为“竞争”。 逻辑因输入端的竞争而导致输出产生本不该出现的干扰窄脉冲,后续有“记逻辑因输入端的竞争而导致输出产生本不该出现的干扰窄脉冲,后续有“记忆”功能的电路会将其当成有效信号而予以响应,从而使系统出现逻辑错误,忆”功能的电路会将其当成有效信号而予以响应,从而使系统出现逻辑错误,称为“冒险”。根据出现的干扰窄脉冲的极性,冒险又分为“称为“冒险”。根据出现的干扰窄脉冲的极性,冒险又分为“ 0”0” 型冒险和型冒险和““ 1”1” 型冒险。型冒险。 11 、“、“ 0”0” 型冒险,输出负脉冲型冒险,输出负脉冲 在图在图 3.293.29(( bb )中, ,当变量)中, ,当变量 AA由高电平变到低电平时,输出由高电平变到低电平时,输出 YY22 产生产生一个负脉冲,宽度为 ,这一负向脉冲又成为毛刺。但一个负脉冲,宽度为 ,这一负向脉冲又成为毛刺。但 AA变化不一定都产生冒变化不一定都产生冒险,当险,当 AA由低变到高时,就无冒险产生。由低变到高时,就无冒险产生。

22 、 “、 “ 1”1” 型冒险,输出正脉冲型冒险,输出正脉冲在图在图 3.293.29(( aa )中, ,当)中, ,当 AA由低电平变到高电平时产生一宽度为由低电平变到高电平时产生一宽度为 ttPDPD 的的正脉冲。正脉冲。综上所述,在组合逻辑电路中,当一个门电路同时输入两个同时向相反方向综上所述,在组合逻辑电路中,当一个门电路同时输入两个同时向相反方向变化的互补信号时,则在输出端可能会产生不应该有的干扰窄脉冲,这是产变化的互补信号时,则在输出端可能会产生不应该有的干扰窄脉冲,这是产生竞争冒险的根本原因。生竞争冒险的根本原因。3.5.2 3.5.2 冒险现象的识别冒险现象的识别在电路输入端只有一个变量改变状态在电路输入端只有一个变量改变状态的情况下,用代数法或卡诺图法可判的情况下,用代数法或卡诺图法可判断一个组合逻辑是否存在冒险。断一个组合逻辑是否存在冒险。11 、 代数判别法、 代数判别法写出组合逻辑电路的逻辑表达式,当写出组合逻辑电路的逻辑表达式,当某些逻辑变量取特定值(某些逻辑变量取特定值( 00或或 11 )时,)时,若表达式能转换为 或 时,则存若表达式能转换为 或 时,则存在冒险。在冒险。例例 3.9 3.9 试判断如图试判断如图 3.303.30所示逻辑电所示逻辑电路是否存在冒险。路是否存在冒险。

因此,如图因此,如图 3.303.30 所示的电路存在冒险。所示的电路存在冒险。

2. 2. 卡诺图判别法卡诺图判别法根据电路逻辑表达式,画出输出变量卡诺图,若卡诺图上的圈相切,根据电路逻辑表达式,画出输出变量卡诺图,若卡诺图上的圈相切,且相切处又且相切处又无无其他圈包含,则存在冒险。其他圈包含,则存在冒险。

例例 3.10 3.10 设逻辑函数 试用卡诺图法判别该电路是否存在冒险。 设逻辑函数 试用卡诺图法判别该电路是否存在冒险。 解解 ::

卡诺图如图卡诺图如图 3.313.31所示,因此存在冒险。所示,因此存在冒险。

在试验室中,通过示波器和逻辑分在试验室中,通过示波器和逻辑分析仪来检查电路的竞争和冒险是常用析仪来检查电路的竞争和冒险是常用的方法,并能对电路的设计和计算机的方法,并能对电路的设计和计算机仿真的结果进行验证。仿真的结果进行验证。

3.5.3 3.5.3 冒险现象的消除方法冒险现象的消除方法 消除组合逻辑电路的冒险现象,主要有以消除组合逻辑电路的冒险现象,主要有以下三种方法。下三种方法。 11 、在输出端接滤波电容、在输出端接滤波电容 由于竞争产生的干扰脉冲一般很窄,所以由于竞争产生的干扰脉冲一般很窄,所以在电路的输出端对地接一个电容值在在电路的输出端对地接一个电容值在 100pF100pF以下的小电容,是输出波形的上升和下降都以下的小电容,是输出波形的上升和下降都变得比较缓慢,从而消除冒险现象。变得比较缓慢,从而消除冒险现象。 22 、引入选择脉冲、引入选择脉冲 因为冒险现象仅仅从发生因为冒险现象仅仅从发生在在输入信号变化输入信号变化转换的瞬间,在稳定状态是没有冒险信号的,转换的瞬间,在稳定状态是没有冒险信号的,所以,采用选择脉冲,输入信号发生转换的所以,采用选择脉冲,输入信号发生转换的瞬间,正确反映组合电路稳定瞬间,正确反映组合电路稳定时时的输出值,的输出值,可以有效地避免各种冒险。常用的选择脉冲可以有效地避免各种冒险。常用的选择脉冲的极性及所加的位置如图的极性及所加的位置如图 3.323.32所示。所示。

图图 3.32 3.32 选通脉冲的极性及选通脉冲的极性及所加的位置示意图所加的位置示意图

当输入信号变换完成,进入稳当输入信号变换完成,进入稳态后,才启动选通脉冲将门打态后,才启动选通脉冲将门打开。这样,输出端就不会出现开。这样,输出端就不会出现冒险脉冲。冒险脉冲。

3.3.增加冗余项增加冗余项 在例在例 3.83.8中 中 ,,在其逻辑表达式中增加乘积项在其逻辑表达式中增加乘积项 AB,AB,使其变为使其变为 F= F= 则在原来产生冒险条件则在原来产生冒险条件 A=B=1A=B=1 时时 ,F=C+ +1=1,,F=C+ +1=1,不会产生冒险。这不会产生冒险。这个函数增加了乘积项个函数增加了乘积项 AA、、 BB 后后 ,,已不是“最简式”已不是“最简式” ,, 故这种乘积项故这种乘积项称为”冗余项”。称为”冗余项”。 上述三种方法的适用场合上述三种方法的适用场合 ,, 效果等仍有利有弊效果等仍有利有弊 ::输出端接滤波电容输出端接滤波电容虽方便易行虽方便易行 ,, 但会使输出电压波形变坏但会使输出电压波形变坏 ,,因此因此 ,, 仅仅适合于对信号波仅仅适合于对信号波形要求不高的场合。引入图形要求不高的场合。引入图 3.323.32所示选通信号的方法,虽然比较所示选通信号的方法,虽然比较简单,一般不需要增加电路元件,但选通信号必须与输入信号维持简单,一般不需要增加电路元件,但选通信号必须与输入信号维持严格的时间关系,因此,选通信号的产生并不容易。增加冗余项虽严格的时间关系,因此,选通信号的产生并不容易。增加冗余项虽然可以解决每次只有单个输入信号发生变化时电路的冒险问题,但然可以解决每次只有单个输入信号发生变化时电路的冒险问题,但不能解决多个输入信号同时发生变化时的冒险现象,适用范围非常不能解决多个输入信号同时发生变化时的冒险现象,适用范围非常有限。有限。

※※ 3.6 3.6 组合逻辑电路应用举例组合逻辑电路应用举例应用应用 1.1.试用八选一芯片试用八选一芯片 CC74HC151CC74HC151安装在楼梯间安装在楼梯间 33处不同位置上处不同位置上 ,,控控制同一盏灯制同一盏灯 L,L,要求改变任何一个开关的状态都能改变灯要求改变任何一个开关的状态都能改变灯 LL的原有状态的原有状态 ..

解解 :(1):(1) 设设 33 个输入逻辑变量个输入逻辑变量 C,BC,B 和和 AA 代代表三个开关表三个开关 ,,逻辑输出逻辑输出 LL 代表灯的状态代表灯的状态 ,,L=1L=1 表示灯亮表示灯亮 ..(2)(2) 根据(根据( 3.113.11 ),取),取 DD00=D=D33=D=D55=D=D66=0=0,, DD11=D=D22=D=D44=D=D77=1 =1 写出逻辑函数:写出逻辑函数: ,,可可以用八选一芯片以用八选一芯片 CC74HC151CC74HC151 实现实现 ,, 也也可以用全加器实现可以用全加器实现 ,, 且电路更简单。且电路更简单。(3)(3)画出八选一芯片实现例画出八选一芯片实现例 3.103.10的电的电路如图路如图 3.333.33所示。所示。 例例 3.103.10的逻辑电路图的逻辑电路图

应用应用 2 2 试用两片双四选一数据选择器试用两片双四选一数据选择器 CC74HC153CC74HC153 和门电路设和门电路设计一个计一个 77 段显示码段显示码 /8421BCD/8421BCD码的转换电路。码的转换电路。解:(解:( 11)) 77段显示码段显示码 /8421BCD/8421BCD码对应的关系真值表如表码对应的关系真值表如表 3.13.177所示。所示。

(2)(2)写出逻辑表达式。由表写出逻辑表达式。由表 3.173.17 直接写出 直接写出 的逻辑表达式。以化简得的逻辑表达式。以化简得 对于式(对于式( 3.143.14)) ,, 若用若用 CC74HC151(1)CC74HC151(1) 实现 实现 ,,用用 aa 、、 ff作为其地址作为其地址 ,,剩余段码为被选数据剩余段码为被选数据 ,,而用而用 CC74HC153(2)CC74HC153(2) 实现 用实现 用 a,ba,b 作为其地址作为其地址 ,,剩剩余段码作为其被选数据余段码作为其被选数据 ,, 则式则式 (3.14)(3.14) 已完全符合数据选择器的输入已完全符合数据选择器的输入 // 输出输出表示式。表示式。(( 33 )) 77 段显示码段显示码 /8421BCD/8421BCD码的逻辑电路如图码的逻辑电路如图 3.343.34 所示。所示。应用应用 3 PCB3 PCB板(电子线路板)的制作过程有板(电子线路板)的制作过程有 AA(用(用 Proter2004D×pProter2004D×p软软件编辑好线路板走线图),件编辑好线路板走线图), BB(激光打印机在热转印纸上输出线路板的走(激光打印机在热转印纸上输出线路板的走线图,并用过塑机在转印纸背面加热,将油墨热转印到覆铜板上),线图,并用过塑机在转印纸背面加热,将油墨热转印到覆铜板上), CC(加热(加热 FeCeFeCe33 溶液并用该溶液把不要的覆铜板腐蚀掉),溶液并用该溶液把不要的覆铜板腐蚀掉), DD(从腐蚀槽取(从腐蚀槽取出线路板,先用环己酮溶液洗去炭粉,再用清水冲洗,然后干燥),出线路板,先用环己酮溶液洗去炭粉,再用清水冲洗,然后干燥), EE(钻孔,打磨,再覆盖松香溶液)等五道工序,每道工序时间不完全相同,(钻孔,打磨,再覆盖松香溶液)等五道工序,每道工序时间不完全相同,分分 88个时间段完成,每道工序与时间的关系列于表个时间段完成,每道工序与时间的关系列于表 3.183.18中,试设计该产中,试设计该产品生产工序流程的控制电路。品生产工序流程的控制电路。

解:(解:( 11 )分析设计要求,确定输入)分析设计要求,确定输入 // 输出情况。由表输出情况。由表 3.183.18可知,可知, PPCBCB 板制作的五道工序共需八个时间段(即单位时间),显然,板制作的五道工序共需八个时间段(即单位时间),显然, 88个单个单位时间为一个加工周期,控制电路输出高电平表示工序能进行,若输位时间为一个加工周期,控制电路输出高电平表示工序能进行,若输出低电平则表示该工序不能进行。每个单位时间用一个时钟脉冲周期出低电平则表示该工序不能进行。每个单位时间用一个时钟脉冲周期表示,制作过程与时钟脉冲间的关系如图表示,制作过程与时钟脉冲间的关系如图 3.353.35 所示。 所示。

(2) (2) 选择合适的逻辑器件。由图选择合适的逻辑器件。由图 3.33.355可知,输出信号可知,输出信号 AA、、 BB 、、 CC 、、 DD、、EE 是是 55个脉冲信号。显然,每个输出个脉冲信号。显然,每个输出信号以信号以 88个单位时间为周期,可选个单位时间为周期,可选用用 33 线线 -8-8线译码器线译码器 74HC13874HC138,其,其地址码可用地址码可用 CPCP 脉冲和计数器产生。脉冲和计数器产生。当地址码当地址码 AA、、 BB 、、 CC 按按 8421BCD8421BCD码规律变化时,从码规律变化时,从 YY00~~ YY77 可产生脉可产生脉冲信号(低电平有效)。当冲信号(低电平有效)。当 ABCDABCD和和 CC74HC138CC74HC138的的 YY00~~ YY77满足下述满足下述关系就可得到图关系就可得到图 3.353.35 所示的波形。所示的波形。

上式的逻辑关系可用图 3.36 所示逻辑电路实现。

(3.15)(3.15)

本 章 小 结本 章 小 结 常用的中规模组合逻辑电路包括加法器、算术运算单元、编码器、译常用的中规模组合逻辑电路包括加法器、算术运算单元、编码器、译码器、数据选择器和数值比较器等。它们不仅是计算机中的基本逻辑功码器、数据选择器和数值比较器等。它们不仅是计算机中的基本逻辑功能构件,而且也常常应用于其它数字系统中。在高密度可编程逻辑器件能构件,而且也常常应用于其它数字系统中。在高密度可编程逻辑器件 CCPLDPLD出现后,它们又成为软件工具库中的标准元件以供调用。出现后,它们又成为软件工具库中的标准元件以供调用。 应用组合逻辑器件进行组合逻辑电路的设计时,有以下特点:应用组合逻辑器件进行组合逻辑电路的设计时,有以下特点: 11 、对逻辑表达式的变换与化简的目的,是使其尽可能与给定的组合逻、对逻辑表达式的变换与化简的目的,是使其尽可能与给定的组合逻辑器件的形式一致,而不单纯是简化。辑器件的形式一致,而不单纯是简化。 22 、设计时应考虑合理充分地应用组合器件的功能。同类的组合器件有、设计时应考虑合理充分地应用组合器件的功能。同类的组合器件有不同的型号,应尽量选用比较简单的器件、较少的数量来满足设计要求。不同的型号,应尽量选用比较简单的器件、较少的数量来满足设计要求。 33 、如果一个组合器件的部分功能就可以满足要求,这时需要对输入、如果一个组合器件的部分功能就可以满足要求,这时需要对输入 //输出信号作适当的处理。如果一个组合器件不能满足设计要求,就需要输出信号作适当的处理。如果一个组合器件不能满足设计要求,就需要对组合器件进行扩展,直接将若干个器件组合或者由适当的逻辑门将这对组合器件进行扩展,直接将若干个器件组合或者由适当的逻辑门将这些器件组合起来。 些器件组合起来。

思考题与习题3.1 试用 CC4560 芯片中的三个半加器实现下列函数。

3.23.2 试分别用下列逻辑器件设计全加器试分别用下列逻辑器件设计全加器 ..(1)(1) 与非门 与非门 (2)(2) 异或门和与非门 异或门和与非门 (3)(3)四选一数据选择器四选一数据选择器3.33.3试分析如图试分析如图 3.373.37所示的四个组合逻辑电路所示的四个组合逻辑电路 ,,并写出逻辑表达式并写出逻辑表达式 ,,列出列出真值表真值表 .. 3.43.4 试分析如图试分析如图 3.383.38 所示的逻辑电路所示的逻辑电路 ,, 写出逻辑表达式写出逻辑表达式 ,, 化简后画出新的化简后画出新的逻辑图逻辑图 .. 3.53.5试分析如图试分析如图 3.393.39所示的逻辑电路所示的逻辑电路 , , 化简并画出新的逻辑图化简并画出新的逻辑图 3.63.6试分析如图试分析如图 3.403.40 所示的逻辑电路所示的逻辑电路 , , 化简并画出新的逻辑图化简并画出新的逻辑图 ..3.73.7 试设计组合逻辑电路试设计组合逻辑电路 ,, 有四个输入端和一个输出端有四个输入端和一个输出端 ,, 当输入全为当输入全为 11 或输或输入全为入全为 00 时时 ,, 或者输入为奇数个或者输入为奇数个 11 时时 ,, 输出为输出为 1,1, 请列出真值表请列出真值表 ,, 写出最简写出最简与或表达式与或表达式 ,,并画出逻辑图并画出逻辑图 ..3.83.8 试设计一个组合电路试设计一个组合电路 ,, 把把 44 位格雷码转换为位格雷码转换为 44 位位 8421BCD8421BCD 码码 ,, 写出表写出表达式达式 ,,并画出逻辑图并画出逻辑图 .. 3.93.9试设计一位二进制数减法器试设计一位二进制数减法器 ,,要包括低位的借位和向高位的借位要包括低位的借位和向高位的借位 , , 并并画出逻辑图画出逻辑图 .. 3.103.10试设计一个组合电路试设计一个组合电路 , , 输入为两个两位的二进制数输入为两个两位的二进制数 ,,输出为两数的乘输出为两数的乘积积 , , 并画出逻辑图并画出逻辑图 ..

3.11 试设计一个组合电路 ,当输入四位二进制数大于 2 而小于等于 7时 ,输出为 1,画出逻辑图。

3.12 试用 4位二进制并行进位全加法器和四异或门 CC4070芯片构成 4位二进制数求补电路 ,并画出逻辑图。

3.13 试用 8位数据大小比较器 CC74HC682 实现数值比较 ,当输入四位二 进制数大于等于 8时 ,输出为 1, 否则为 0( 提示 :用进位输出端 C0作

为输出 ) 。 3.14 试用两片 4位数值比较器 CC74HC85实现两个 7位二进制数比较

的逻辑图。 3.15 试用 3 线 ---8线译码器 CC74HC138扩展为 5线 ---32 线译码器 ,

并画出示意图。 3.16 试用 3 线 ---8线译码器 CC74HC138和与非门实现下列逻辑函数。

3.17 如图 3.41所示 ,试写出由 3 线 ---8线译码器 CC74HC138构成的输出 Z1 和 Z2 的最简与或表达式。

3.18 试用 4选 1 数据选择器 CC74HC153分别实现下列逻辑函数。

3.19 试用若干片双 4选 1 数据选择器 CC74HC153 和逻辑门分别实现下列逻辑函数 ( 要尽可能节省芯片如图 3.42所示 ) 。

3.20试用 8选 1 数据选择器 CC74HC151 和逻辑门分别实现下列逻辑函数 .

3.21 试用 4选 1 数据选择器 CC74HC153 构成 16选 1 数据选择器 ,并画出示意图。3.22 试用 3 线— 8线译码器 CC74HC238和与非门实现如下多输出逻辑函数。

※ ※ 3.23 3.23 已知函数已知函数 F(A,B,C)= ,F(A,B,C)= ,画出用最少逻辑门实现画出用最少逻辑门实现的电路并分析是否存在竟争冒险的电路并分析是否存在竟争冒险 ,,试用增加冗余项的办法消除。试用增加冗余项的办法消除。